Ldmos Modeling and High Efficiency Power Amplifier Design Using Pso Algorithm

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Chapter 7: AC Transistor Amplifiers

Chapter 7: Transistors, part 2 Chapter 7: AC Transistor Amplifiers The transistor amplifiers that we studied in the last chapter have some serious problems for use in AC signals. Their most serious shortcoming is that there is a “dead region” where small signals do not turn on the transistor. So, if your signal is smaller than 0.6 V, or if it is negative, the transistor does not conduct and the amplifier does not work. Design goals for an AC amplifier Before moving on to making a better AC amplifier, let’s define some useful terms. We define the output range to be the range of possible output voltages. We refer to the maximum and minimum output voltages as the rail voltages and the output swing is the difference between the rail voltages. The input range is the range of input voltages that produce outputs which are not at either rail voltage. Our goal in designing an AC amplifier is to get an input range and output range which is symmetric around zero and ensure that there is not a dead region. To do this we need make sure that the transistor is in conduction for all of our input range. How does this work? We do it by adding an offset voltage to the input to make sure the voltage presented to the transistor’s base with no input signal, the resting or quiescent voltage , is well above ground. In lab 6, the function generator provided the offset, in this chapter we will show how to design an amplifier which provides its own offset. -

Power Electronics

Diodes and Transistors Semiconductors • Semiconductor devices are made of alternating layers of positively doped material (P) and negatively doped material (N). • Diodes are PN or NP, BJTs are PNP or NPN, IGBTs are PNPN. Other devices are more complex Diodes • A diode is a device which allows flow in one direction but not the other. • When conducting, the diodes create a voltage drop, kind of acting like a resistor • There are three main types of power diodes – Power Diode – Fast recovery diode – Schottky Diodes Power Diodes • Max properties: 1500V, 400A, 1kHz • Forward voltage drop of 0.7 V when on Diode circuit voltage measurements: (a) Forward biased. (b) Reverse biased. Fast Recovery Diodes • Max properties: similar to regular power diodes but recover time as low as 50ns • The following is a graph of a diode’s recovery time. trr is shorter for fast recovery diodes Schottky Diodes • Max properties: 400V, 400A • Very fast recovery time • Lower voltage drop when conducting than regular diodes • Ideal for high current low voltage applications Current vs Voltage Characteristics • All diodes have two main weaknesses – Leakage current when the diode is off. This is power loss – Voltage drop when the diode is conducting. This is directly converted to heat, i.e. power loss • Other problems to watch for: – Notice the reverse current in the recovery time graph. This can be limited through certain circuits. Ways Around Maximum Properties • To overcome maximum voltage, we can use the diodes in series. Here is a voltage sharing circuit • To overcome maximum current, we can use the diodes in parallel. -

MW6IC2420NBR1 2450 Mhz, 20 W, 28 V CW RF LDMOS Integrated

Freescale Semiconductor Document Number: MW6IC2420N Technical Data Rev. 3, 12/2010 RF LDMOS Integrated Power Amplifier MW6IC2420NBR1 The MW6IC2420NB integrated circuit is designed with on--chip matching that makes it usable at 2450 MHz. This multi--stage structure is rated for 26 to 32 Volt operation and covers all typical industrial, scientific and medical modulation formats. 2450 MHz, 20 W, 28 V Driver Applications CW • Typical CW Performance at 2450 MHz: VDD =28Volts,IDQ1 = 210 mA, RF LDMOS INTEGRATED POWER I = 370 mA, P = 20 Watts DQ2 out AMPLIFIER Power Gain — 19.5 dB Power Added Efficiency — 27% • Capable of Handling 3:1 VSWR, @ 28 Vdc, 2170 MHz, 20 Watts CW Output Power • Stable into a 3:1 VSWR. All Spurs Below --60 dBc @ 100 mW to 10 Watts CW Pout. Features Y • Characterized with Series Equivalent Large--Signal Impedance Parameters and Common Source Scattering Parameters • On--Chip Matching (50 Ohm Input, DC Blocked, >3 Ohm Output) • Integrated Quiescent Current Temperature Compensation with Enable/Disable Function (1) • Integrated ESD Protection CASE 1329--09 • 225°C Capable Plastic Package TO--272 WB--16 • RoHS Compliant PLASTIC • In Tape and Reel. R1 Suffix = 500 Units, 44 mm Tape Width, 13 inch Reel GND 1 16 GND VDS1 2 NC 3 15 NC NC 4 LIFETIME BU VDS1 NC 5 RF / RFin 6 14 out RFin RFout/VDS2 VDS2 NC 7 VGS1 8 VGS2 9 VGS1 Quiescent Current VDS1 10 13 NC (1) VGS2 Temperature Compensation GND 11 12 GND VDS1 (Top View) Note: Exposed backside of the package is the source terminal for the transistors. -

RF LDMOS/EDMOS: Embedded Devices for Highly Integrated Solutions

RF LDMOS/EDMOS: embedded devices for highly integrated solutions T. Letavic, C. Li, M. Zierak, N. Feilchenfeld, M. Li, S. Zhang, P. Shyam, V. Purakh Outline • PowerSoc systems and product drivers – Systems that benefit from embedded power supplies also require .. • Ubiquitous wireless connectivity – RF integration (802.11.54, BTLE, BT, WPAN, …) • MCU + memory – code, actuation, network configuration – IoT network edge node = miniaturized embedded power supply and RF link • PowerSoC and RF device integration strategies – 180nm bulk-Si mobile power management process – LDMOS – 55nm bulk-Si silicon IoT platform – EDMOS – DC and RF benchmark to 5V CMOS • Power and RF application characterization – ISM bands, WiFi, performance against cellular industry standards – Embedded power and RF with the same device unit cell • Summary – PowerSoc and RF use the same device unit cell 2 Embedded power and RF: Envelope Tracking https://www.nujira.com Motorola eg. US 6,407,634 B1, US 6,617,920 B2 • RF supply modulation to reduce power dissipation (WiFi, 4G LTE) – Linear amplifier: 5Vpk-pk 80 MHz BW, >16QAM -> fT > 20 Ghz – SMPS: > 10-20 MHz fsw, 5-7 V FSOA, ultra-low Rsp*Qgg FOM • Optimal solution fT/fmax of cSiGe/GaN/GaAs with Si BCD voltage handling – RF LDMOS and RF EDMOS are challenging the incumbents …. 3 Embedded Power and RF: IoT Edge Node Semtech integrated RF transceiver SX123SX • Wireless IEEE 802.15.4, IEEE 802.11.ah, 2G/3G/4G LTE MTC, …. – 50 B connected endpoints 2020 (Cisco Mobility Report Dec 2016) – Integrated low power RF modem + PA, SMPS, -

Gan Or Gaas, TWT Or Klystron - Testing High Power Amplifiers for RADAR Signals Using Peak Power Meters

Application Note GaN or GaAs, TWT or Klystron - Testing High Power Amplifiers for RADAR Signals using Peak Power Meters Vitali Penso Applications Engineer, Boonton Electronics Abstract Measuring and characterizing pulsed RF signals used in radar applications present unique challenges. Unlike communication signals, pulsed radar signals are “on” for a short time followed by a long “off” period, during “on” time the system transmits anywhere from kilowatts to megawatts of power. The high power pulsing can stress the power amplifier (PA) in a number of ways both during the on/off transitions and during prolonged “on” periods. As new PA device technologies are introduced, latest one being GaN, the behavior of the amplifier needs to be thoroughly tested and evaluated. Given the time domain nature of the pulsed RF signal, the best way to observe the performance of the amplifier is through time domain signal analysis. This article explains why the peak power meter is a must have test instrument for characterizing the behavior of pulsed RF power amplifiers (PA) used in radar systems. Radar Power Amplifier Technology Overview Peak Power Meter for Pulsed RADAR Measurements Before we look at the peak power meter and its capabilities, let’s The most critical analysis of the pulsed RF signal takes place in the look at different technologies used in high power amplifiers (HPA) time domain. Since peak power meters measure, analyze and dis- for RADAR systems, particularly GaN on SiC, and why it has grabbed play the power envelope of a RF signal in the time domain, they the attention over the past decade. -

Notes for Lab 1 (Bipolar (Junction) Transistor Lab)

ECE 327: Electronic Devices and Circuits Laboratory I Notes for Lab 1 (Bipolar (Junction) Transistor Lab) 1. Introduce bipolar junction transistors • “Transistor man” (from The Art of Electronics (2nd edition) by Horowitz and Hill) – Transistors are not “switches” – Base–emitter diode current sets collector–emitter resistance – Transistors are “dynamic resistors” (i.e., “transfer resistor”) – Act like closed switch in “saturation” mode – Act like open switch in “cutoff” mode – Act like current amplifier in “active” mode • Active-mode BJT model – Collector resistance is dynamically set so that collector current is β times base current – β is assumed to be very high (β ≈ 100–200 in this laboratory) – Under most conditions, base current is negligible, so collector and emitter current are equal – β ≈ hfe ≈ hFE – Good designs only depend on β being large – The active-mode model: ∗ Assumptions: · Must have vEC > 0.2 V (otherwise, in saturation) · Must have very low input impedance compared to βRE ∗ Consequences: · iB ≈ 0 · vE = vB ± 0.7 V · iC ≈ iE – Typically, use base and emitter voltages to find emitter current. Finish analysis by setting collector current equal to emitter current. • Symbols – Arrow represents base–emitter diode (i.e., emitter always has arrow) – npn transistor: Base–emitter diode is “not pointing in” – pnp transistor: Emitter–base diode “points in proudly” – See part pin-outs for easy wiring key • “Common” configurations: hold one terminal constant, vary a second, and use the third as output – common-collector ties collector -

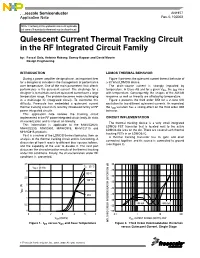

Quiescent Current Control for the RF Integrated Circuit Device Family

Freescale Semiconductor AN1977 Application Note Rev. 0, 10/2003 NOTE: The theory in this application note is still applicable, but some of the products referenced may be discontinued. Quiescent Current Thermal Tracking Circuit in the RF Integrated Circuit Family by: Pascal Gola, Antoine Rabany, Samay Kapoor and David Maurin Design Engineering INTRODUCTION LDMOS THERMAL BEHAVIOR During a power amplifier design phase, an important item Figure 1 presents the quiescent current thermal behavior of for a designer to consider is the management of performance a 30 Watt LDMOS device. over temperature. One of the main parameters that affects The drain-source current is strongly impacted by performance is the quiescent current. The challenge for a temperature. In Class AB and for a given VGS, the IDQ rises designer is to maintain constant quiescent current over a large with temperature. Consequently, the shapes of the AM/AM temperature range. The problem becomes more challenging response as well as linearity are affected by temperature. in a multistage IC (integrated circuit). To overcome this Figure 2 presents the third order IMD for a 2-tone CW difficulty, Freescale has embedded a quiescent current excitation for two different quiescent currents. As expected, thermal tracking circuit in its recently introduced family of RF the IDQ variation has a strong effect on the third order IMD power integrated circuits. behavior. This application note reviews the tracking circuit implemented in the RF power integrated circuit family, its static CIRCUIT IMPLEMENTATION characterization and its impact on linearity. The thermal tracking device is a very small integrated This information is applicable to the MW4IC2020, LDMOS FET transistor that is located next to the active MW4IC2230, MWIC930, MW4IC915, MHVIC2115 and LDMOS die area on the die. -

ECE 255, MOSFET Basic Configurations

ECE 255, MOSFET Basic Configurations 8 March 2018 In this lecture, we will go back to Section 7.3, and the basic configurations of MOSFET amplifiers will be studied similar to that of BJT. Previously, it has been shown that with the transistor DC biased at the appropriate point (Q point or operating point), linear relations can be derived between the small voltage signal and current signal. We will continue this analysis with MOSFETs, starting with the common-source amplifier. 1 Common-Source (CS) Amplifier The common-source (CS) amplifier for MOSFET is the analogue of the common- emitter amplifier for BJT. Its popularity arises from its high gain, and that by cascading a number of them, larger amplification of the signal can be achieved. 1.1 Chararacteristic Parameters of the CS Amplifier Figure 1(a) shows the small-signal model for the common-source amplifier. Here, RD is considered part of the amplifier and is the resistance that one measures between the drain and the ground. The small-signal model can be replaced by its hybrid-π model as shown in Figure 1(b). Then the current induced in the output port is i = −gmvgs as indicated by the current source. Thus vo = −gmvgsRD (1.1) By inspection, one sees that Rin = 1; vi = vsig; vgs = vi (1.2) Thus the open-circuit voltage gain is vo Avo = = −gmRD (1.3) vi Printed on March 14, 2018 at 10 : 48: W.C. Chew and S.K. Gupta. 1 One can replace a linear circuit driven by a source by its Th´evenin equivalence. -

6 Insulated-Gate Field-Effect Transistors

Chapter 6 INSULATED-GATE FIELD-EFFECT TRANSISTORS Contents 6.1 Introduction ......................................301 6.2 Depletion-type IGFETs ...............................302 6.3 Enhancement-type IGFETs – PENDING .....................311 6.4 Active-mode operation – PENDING .......................311 6.5 The common-source amplifier – PENDING ...................312 6.6 The common-drain amplifier – PENDING ....................312 6.7 The common-gate amplifier – PENDING ....................312 6.8 Biasing techniques – PENDING ..........................312 6.9 Transistor ratings and packages – PENDING .................312 6.10 IGFET quirks – PENDING .............................313 6.11 MESFETs – PENDING ................................313 6.12 IGBTs ..........................................313 *** INCOMPLETE *** 6.1 Introduction As was stated in the last chapter, there is more than one type of field-effect transistor. The junction field-effect transistor, or JFET, uses voltage applied across a reverse-biased PN junc- tion to control the width of that junction’s depletion region, which then controls the conduc- tivity of a semiconductor channel through which the controlled current moves. Another type of field-effect device – the insulated gate field-effect transistor, or IGFET – exploits a similar principle of a depletion region controlling conductivity through a semiconductor channel, but it differs primarily from the JFET in that there is no direct connection between the gate lead 301 302 CHAPTER 6. INSULATED-GATE FIELD-EFFECT TRANSISTORS and the semiconductor material itself. Rather, the gate lead is insulated from the transistor body by a thin barrier, hence the term insulated gate. This insulating barrier acts like the di- electric layer of a capacitor, and allows gate-to-source voltage to influence the depletion region electrostatically rather than by direct connection. In addition to a choice of N-channel versus P-channel design, IGFETs come in two major types: enhancement and depletion. -

Differential Amplifiers

www.getmyuni.com Operational Amplifiers: The operational amplifier is a direct-coupled high gain amplifier usable from 0 to over 1MH Z to which feedback is added to control its overall response characteristic i.e. gain and bandwidth. The op-amp exhibits the gain down to zero frequency. Such direct coupled (dc) amplifiers do not use blocking (coupling and by pass) capacitors since these would reduce the amplification to zero at zero frequency. Large by pass capacitors may be used but it is not possible to fabricate large capacitors on a IC chip. The capacitors fabricated are usually less than 20 pf. Transistor, diodes and resistors are also fabricated on the same chip. Differential Amplifiers: Differential amplifier is a basic building block of an op-amp. The function of a differential amplifier is to amplify the difference between two input signals. How the differential amplifier is developed? Let us consider two emitter-biased circuits as shown in fig. 1. Fig. 1 The two transistors Q1 and Q2 have identical characteristics. The resistances of the circuits are equal, i.e. RE1 = R E2, RC1 = R C2 and the magnitude of +VCC is equal to the magnitude of �VEE. These voltages are measured with respect to ground. To make a differential amplifier, the two circuits are connected as shown in fig. 1. The two +VCC and �VEE supply terminals are made common because they are same. The two emitters are also connected and the parallel combination of RE1 and RE2 is replaced by a resistance RE. The two input signals v1 & v2 are applied at the base of Q1 and at the base of Q2. -

INA106: Precision Gain = 10 Differential Amplifier Datasheet

INA106 IN A1 06 IN A106 SBOS152A – AUGUST 1987 – REVISED OCTOBER 2003 Precision Gain = 10 DIFFERENTIAL AMPLIFIER FEATURES APPLICATIONS ● ACCURATE GAIN: ±0.025% max ● G = 10 DIFFERENTIAL AMPLIFIER ● HIGH COMMON-MODE REJECTION: 86dB min ● G = +10 AMPLIFIER ● NONLINEARITY: 0.001% max ● G = –10 AMPLIFIER ● EASY TO USE ● G = +11 AMPLIFIER ● PLASTIC 8-PIN DIP, SO-8 SOIC ● INSTRUMENTATION AMPLIFIER PACKAGES DESCRIPTION R1 R2 10kΩ 100kΩ 2 5 The INA106 is a monolithic Gain = 10 differential amplifier –In Sense consisting of a precision op amp and on-chip metal film 7 resistors. The resistors are laser trimmed for accurate gain V+ and high common-mode rejection. Excellent TCR tracking 6 of the resistors maintains gain accuracy and common-mode Output rejection over temperature. 4 V– The differential amplifier is the foundation of many com- R3 R4 10kΩ 100kΩ monly used circuits. The INA106 provides this precision 3 1 circuit function without using an expensive resistor network. +In Reference The INA106 is available in 8-pin plastic DIP and SO-8 surface-mount packages. Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners. PRODUCTION DATA information is current as of publication date. Copyright © 1987-2003, Texas Instruments Incorporated Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters. www.ti.com SPECIFICATIONS ELECTRICAL ° ± At +25 C, VS = 15V, unless otherwise specified. -

Building a Vacuum Tube Amplifier

Brian Large Physics 398 EMI Final Report Building a Vacuum Tube Amplifier First, let me preface this paper by saying that I will try to write it for the idiot, because I knew absolutely nothing about amplifiers before I started. Project Selection I had tried putting together a stomp box once before (in high school), with little success, so the idea of building something as a project for this course intrigued me. I also was intrigued with building an amplifier because it is the part of the sound creation process that I understand the least. Maybe that’s why I’m not an electrical engineer. Anyways, I already own a solid-state amplifier (a Fender Deluxe 112 Plus), so I decided that it would be nice to add a tube amp. I drew up a list of “Things I wanted in an Amplifier” and began to discuss the matters with the course instructor, Professor Steve Errede, and my lab TA, Dan Finkenstadt. I had decided I wanted a class AB push-pull amp putting out 10-20 Watts. I had decided against a reverb unit because it made the schematic much more complicated and would also cost more. With these decisions in mind, we decided that a Fender Tweed Deluxe would be the easiest to build that fit my needs. The Deluxe schematic that I built my amp off of was a 5E3, built by Fender from 1955-1960 (Figure 1). The reason we chose such an old amp is because they sound great and their schematics are considerably easier to build.