An Introduction to Picmicro Microcontrollers

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Zilog’S Ez80acclaim!™ Product Family, Which Offers On-Chip Flash Versions of Zilog’S Ez80® • 3.0–3.6 V Supply Voltage with 5 V Tolerant Inputs Processor Core

eZ80Acclaim!™ Flash Microcontrollers eZ80F91 Product Brief PB013502-0104 Product Block Diagram • I2C with independent clock rate generator • SPI with independent clock rate generator eZ80F91 MCU • Four Counter/Timers with prescalers supporting event counting, input capture, output compare, and 256 KB Flash + 32-Bit GPIO PWM modes 512 B Flash • Watch-Dog Timer with internal RC clocking 10/100 Mbps option 8KB SRAM Ethernet MAC • Real-time clock with on-chip 32kHz oscillator, 8KB Frame Buffer selectable 50/60Hz input, and separate RTC_VDD pin for battery backup. Infrared 2 • Glueless external memory interface with 4 Chip- Encoder/ 2 UART I C SPI Selects/Wait-State Generators and external WAIT Decoder input pin. Supports Intel and Motorola buses. Real-Time • JTAG Interface supporting emulation features 4 PRT WDT Clock • Low-power PLL and on-chip oscillator • Programmable-priority vectored interrupts, non- 4 CS JTAG ZDI PLL maskable interrupts, and interrupt controller +WSG • New DMA-like eZ80® CPU instructions • Power management features supporting HALT/ Features SLEEP modes and selective peripheral power- down controls The eZ80F91 microcontroller is a member of • 144-pin BGA or 144-pin LQFP package ZiLOG’s eZ80Acclaim!™ product family, which offers on-chip Flash versions of ZiLOG’s eZ80® • 3.0–3.6 V supply voltage with 5 V tolerant inputs processor core. The eZ80F91 offers the following • Operating Temperature Ranges: features: – Standard: 0ºC to +70ºC • 50MHz High-Performance eZ80® CPU – Extended: –40ºC to +105ºC • 256 KB Flash Program Memory plus extra 512B device configuration Flash memory General Description • 32 bits of General-Purpose I/O The eZ80F91 device is an industry first, featuring a • 16K B total on-chip high-speed SRAM: high-performance 8-bit microcontroller with an integrated 10/100 BaseT Ethernet Media Access – 8KB for general-purpose use controller (EMAC). -

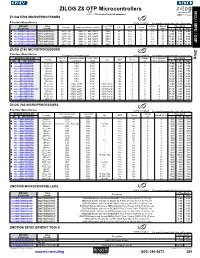

ZILOG Z8 OTP Microcontrollers MCU / MPU / DSP This Product Is Rohs Compliant

ZILOG Z8 OTP Microcontrollers DSP MPU / MCU / This product is RoHS compliant. ZILOG EZ80 MICROPROCESSORS ♦ Surface Mount Device For quantities greater than listed, call for quote. MOUSER Zilog Core CPU Voltage Speed Price Each Package Communications Controller I/O WDT Timers STOCK NO. Part No. Used (V) (MHz) 1 25 100 ♦ 692-EZ80L92AZ020EG EZ80L92AZ020EC LQFP-100 DMA, I2C, SPI, UART EZ80 24 Yes 6 3.3 20 9.29 9.10 8.63 ♦ 692-EZ80L92AZ020SG EZ80L92AZ020SC LQFP-100 DMA, I2C, SPI, UART EZ80 24 Yes 6 3.3 20 8.08 7.78 7.50 ♦ 692-EZ80L92AZ050EG EZ80L92AZ050EC LQFP-100 DMA, I2C, SPI, UART EZ80 24 Yes 6 3.3 50 10.21 9.75 9.49 ♦ 692-EZ80L92AZ050SG EZ80L92AZ050SC LQFP-100 DMA, I2C, SPI, UART EZ80 24 Yes 6 3.3 50 8.89 8.54 8.26 ♦ 692-EZ80190AZ050SG EZ80190AZ050SC LQFP-100 DMA, I2C, SPI, UART EZ80 32 Yes 6 3.3 50 12.03 11.59 11.17 ♦ 692-EZ80190AZ050EG EZ80190AZ050EC LQFP-100 DMA, I2C, SPI, UART EZ80 32 Yes 6 3.3 50 13.82 13.28 12.84 ZILOG Z180 MICROPROCESSORS Zilog ♦Surface Mount Device *See above for development tools. For quantities greater than listed, call for quote. MOUSER STOCK NO. Speed Communications Core CPU Voltage Development Price Each Package I/O WDT Timers Mfr. Mfr. Part No. (MHz) Controller Used (V) Tools Available 1 25 100 ♦ 692-Z8018006VSG PLCC-68 6 CPU Z180 - No 2 5 - 8.40 7.36 6.01 ♦ 692-Z8018006VEG PLCC-68 6 CPU Z180 - No 2 5 - 10.00 8.55 7.14 692-Z8018006PSG DIP-64 6 CPU Z180 - No 2 5 - 8.40 7.36 6.01 692-Z8018006PEG DIP-64 6 CPU Z180 - No 2 5 - 10.00 8.55 7.14 692-Z8018008PSG DIP-64 8 CPU Z180 - No 2 5 - 8.75 7.38 6.25 ♦ 692-Z8018008VSG -

Data Acquisition

#147 October 2002 www.circuitcellar.com CIRCUIT CELLAR® THE MAGAZINE FOR COMPUTER APPLICATIONS DATA ACQUISITION 2-D Or Not 2-D Solar-Powered Robot The LED Alternative Mad DashWWW.GiURUMELE.Hi2.RO For Flash Cash Contest Primer 10> 7925274 75349 $4.95 U.S. ($5.95 Canada) WWW.GiURUMELE.Hi2.RO WWW.GiURUMELE.Hi2.RO Digital Oscilloscopes • 2 Channel Digital Oscilloscope DSO-2102S $525 • 100 MSa/s max single shot rate DSO-2102M $650 • 32K samples per channel Each includes Oscilloscope, • Advanced Triggering Probes, Interface Cable, Power • Only 9 oz and 6.3” x 3.75” x 1.25” Adapter, and software for • Small, Lightweight, and Portable Win95/98, WinNT, Win2000 • Parallel Port interface to PC and DOS. • Advanced Math options • FFT Spectrum Analyzer options Logic Analyzers • 40 to 160 channels • 24 Channel Logic Analyzer • up to 500 MSa/s • 100MSa/S max sample rate • Variable Threshold • Variable Threshold Voltage • 8 External Clocks • Large 128k Buffer • 16 Level Triggering • Small, Lightweight and Portable • up to 512KWWW.GiURUMELE.Hi2.RO samples/ch • Only 4 oz and 4.75” x 2.75” x 1” • Optional Parallel Interface • Parallel Port Interface to PC • Optional 100 MSa/s Pattern Generator • Trigger Out • Windows 95/98 Software LA4240-32K (200MHz, 40CH) $1350 LA4280-32K (200MHz, 80CH) $2000 LA2124-128K (100MSa/s, 24CH) LA4540-128K (500MHz, 40CH) $1900 Clips, Wires, Interface Cable, AC LA4580-128K (500MHz, 80CH) $2800 Adapter and Software $800 LA45160-128K (500MHz, 160CH) $7000 All prices include Pods and Software www.LinkIns4.com Link Instruments • 369 Passaic Ave • Suite 100 • Fairfield, NJ 07004 • (973) 808-8990 • Fax (973) 808-8786 WWW.GiURUMELE.Hi2.RO TASK MANAGER EDITORIAL DIRECTOR/FOUNDER CHIEF FINANCIAL OFFICER Be a Contender Steve Ciarcia Jeannette Ciarcia MANAGING EDITOR Jennifer Huber CUSTOMER SERVICE Elaine Johnston TECHNICAL EDITOR C.J. -

Natalia Nikolaevna Shusharina Maxin.Pmd

BIOSCIENCES BIOTECHNOLOGY RESEARCH ASIA, September 2016. Vol. 13(3), 1523-1536 Development of the Brain-computer Interface Based on the Biometric Control Channels and Multi-modal Feedback to Provide A Human with Neuro-electronic Systems and Exoskeleton Structures to Compensate the Motor Functions Natalia Nikolaevna Shusharina1, Evgeny Anatolyevich Bogdanov1, Stepan Aleksandrovich Botman1, Ekaterina Vladimirovna Silina2, Victor Aleksandrovich Stupin3 and Maksim Vladimirovich Patrushev1 1Immanuel Kant Baltic Federal University (IKBFU), Nevskogo Str., 14, Kaliningrad, 236041, Russia 2I.M. Sechenov First Moscow State Medical University (First MSMU), Trubetskaya str, 8, Moscow, 119991, Russia 3Pirogov´s Russian National Research Medical University (RNRMU), Ostrovityanova str, 1, Moscow, 117997, Russia http://dx.doi.org/10.13005/bbra/2295 (Received: 15 June 2016; accepted: 05 August 2016) The aim of this paper is to create a multi-functional neuro-device and to study the possibilities of long-term monitoring of several physiological parameters of an organism controlled by brain activity with transmitting the data to the exoskeleton. To achieve this goal, analytical review of modern scientific-and-technical, normative, technical, and medical literature involving scientific and technical problems has been performed; the research area has been chosen and justified, including the definition of optimal electrodes and their affixing to the body of the patient, the definition of the best suitable power source and its operation mode, the definition of the best suitable useful signal amplifiers, and a system of filtering off external noises. A neuro-device mock-up has been made for recognizing electrophysiological signals and transmitting them to the exoskeleton, also the software has been written. -

Portability Techniques for Embedded Systems Data Management

Portability Techniques for Embedded Systems Data Management McObject LLC st 33309 1 Way South Suite A-208 Federal Way, WA 98003 Phone: 425-888-8505 E-mail: [email protected] www.mcobject.com Copyright 2020, McObject LLC Whether an embedded systems database is developed for a specific application or as a commercial product, portability matters. Most embedded data management code is still “homegrown,” and when external forces drive an operating system or hardware change, data management code portability saves significant development time. This is especially important since increasingly, hardware’s lifespan is shorter than firmware’s. For database vendors, compatibility with the dozens of hardware designs, operating systems and compilers used in embedded systems provides a major marketing advantage. For real-time embedded systems, database code portability means more than the ability to compile and execute on different platforms: portability strategies also tie into performance. Software developed for a specific OS, hardware platform and compiler often performs poorly when moved to a new environment, and optimizations to remedy this are very time-consuming. Truly portable embedded systems data management code carries its optimization with it, requiring the absolute minimum adaptation to deliver the best performance in new environments. Using Standard C Writing portable code traditionally begins with a commitment to use only ANSI C. But this is easier said than done. Even code written with the purest ANSI C intentions frequently makes assumptions about the target hardware and operating environment. In addition, programmers often tend to use available compiler extensions. Many of the extensions – prototypes, stronger type- checking, etc, – enhance portability, but others may add to platform dependencies. -

Installing Klocwork Insight

Installation and Upgrade Klocwork Insight 10.0 SR4 Document version 1.4 Klocwork Installation and Upgrade Version 10.0 PDF generated using the open source mwlib toolkit. See http://code.pediapress.com/ for more information. PDF generated at: Wed, 30 Apr 2014 20:28:47 EST Contents Articles Before you install 1 System requirements 1 Release Notes 10 About the Klocwork packages and components 23 Upgrading from a previous version 25 Upgrading from a previous version 25 Import your existing projects into a new projects root 26 Migrate your projects root directory 29 Installing the Klocwork Server package on Windows -- Upgrade only 34 Installing the Klocwork Server package on Unix -- Upgrade only 36 Installing the Klocwork Server package on Mac -- Upgrade only 38 Get a license 40 Getting a license 40 Installing the Server package 43 Installing Klocwork Insight 43 Installing the Klocwork Server package on Windows 44 Installing the Klocwork Server package on Unix 47 Installing the Klocwork Server package on Mac 50 Viewing and changing Klocwork server settings 52 Downloading and deploying the desktop analysis plug-ins 54 kwupdate 55 Installing a desktop analysis plug-in or command line utility 57 Installing a desktop analysis plug-in 57 Installing the Klocwork plug-in from the Eclipse update site 60 Running a custom installation for new or upgraded IDEs 61 Installing the Distributed Analysis package 62 Installing the Distributed Analysis package 62 Configuring and starting the Klocwork servers 65 Viewing and changing Klocwork server settings 65 -

The New Rabbit 3000М Microprocessor

3UHOLPLQDU\Ã6XPPDU\Ã 7KH1HZ5DEELW 0LFURSURFHVVRU Key New Features Low-EMI: typically <10 dB µV/m @ 3 m Ultra-low power modes 1.5–3.6 V (5 V tolerant I/O) 54 MHz clock speed 56+ digital I/O 6 serial ports supporting IrDA, SDLC/HDLC, Async, SPI Pulse capture and measurement Quadrature encoder inputs SHOWN ACTUAL SIZE (top) PWM outputs 16 x 16 x 1.5 mm Standard Features of Rabbit Processors The new Rabbit 3000™ is an extremely low-EMI microprocessor designed Glueless memory and I/O interface specifically for embedded control, communications, and Ethernet Direct support for 1 MB code/data space connectivity. The Rabbit 3000 shares its instruction set and conceptual (up to 6 MB with glueless interface) design with the proven Rabbit 2000™. Battery-backable real-time clock The Rabbit 3000 is fast—running at up to 54 MHz—and C-friendly, with Watchdog timer compact code and direct software support for 1 MB of code/data space. Remote boot/program Rabbit 3000 development tools include extensive support for Internet and network connectivity, with full source code for TCP/IP provided royalty free. Slave port interface The Rabbit 3000 operates at 3.3 V (with 5 V tolerant I/O) and boasts 6 serial ports with IrDA, 56+ digital I/O, quadrature encoder inputs, PWM Design Advantages outputs, and pulse capture and measurement capabilities. It also features a Extensive Ethernet/Internet support battery-backable real-time clock, glueless interfacing, and ultra-low power and royalty-free TCP/IP stack with modes. Its compact instruction set and high clock speeds give the Rabbit source and sample programs 3000 blazingly fast performance for math, logic, and I/O. -

Extracting and Mapping Industry 4.0 Technologies Using Wikipedia

Computers in Industry 100 (2018) 244–257 Contents lists available at ScienceDirect Computers in Industry journal homepage: www.elsevier.com/locate/compind Extracting and mapping industry 4.0 technologies using wikipedia T ⁎ Filippo Chiarelloa, , Leonello Trivellib, Andrea Bonaccorsia, Gualtiero Fantonic a Department of Energy, Systems, Territory and Construction Engineering, University of Pisa, Largo Lucio Lazzarino, 2, 56126 Pisa, Italy b Department of Economics and Management, University of Pisa, Via Cosimo Ridolfi, 10, 56124 Pisa, Italy c Department of Mechanical, Nuclear and Production Engineering, University of Pisa, Largo Lucio Lazzarino, 2, 56126 Pisa, Italy ARTICLE INFO ABSTRACT Keywords: The explosion of the interest in the industry 4.0 generated a hype on both academia and business: the former is Industry 4.0 attracted for the opportunities given by the emergence of such a new field, the latter is pulled by incentives and Digital industry national investment plans. The Industry 4.0 technological field is not new but it is highly heterogeneous (actually Industrial IoT it is the aggregation point of more than 30 different fields of the technology). For this reason, many stakeholders Big data feel uncomfortable since they do not master the whole set of technologies, they manifested a lack of knowledge Digital currency and problems of communication with other domains. Programming languages Computing Actually such problem is twofold, on one side a common vocabulary that helps domain experts to have a Embedded systems mutual understanding is missing Riel et al. [1], on the other side, an overall standardization effort would be IoT beneficial to integrate existing terminologies in a reference architecture for the Industry 4.0 paradigm Smit et al. -

Ez80 Sales Demonstration Platform

ZiLOG Development Platforms eZ80® Sales Demonstration Platform User Manual UM015201-0603 ZiLOG Worldwide Headquarters • 532 Race Street • San Jose, CA 95126-3432 Telephone: 408.558.8500 • Fax: 408.558.8300 • www.ZiLOG.com ZiLOG Development Platforms eZ80® Sales Demonstration Platform ii This publication is subject to replacement by a later edition. To determine whether a later edition exists, or to request copies of publications, contact: ZiLOG Worldwide Headquarters 532 Race Street San Jose, CA 95126-3432 Telephone: 408.558.8500 Fax: 408.558.8300 Document Disclaimer ZiLOG is a registered trademark of ZiLOG Inc. in the United States and in other countries. All other products and/or service names mentioned herein may be trademarks of the companies with which they are associated. ©2003 by ZiLOG, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZiLOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZiLOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. Except with the express written approval of ZiLOG, use of information, devices, or technology as critical components of life support systems is not authorized. No licenses are conveyed, implicitly or otherwise, by this document under any intellectual property rights. User Manual UM015201-0603 ZiLOG Development Platforms eZ80® Sales Demonstration Platform iii Safeguards The following precautions must be observed when working with the devices described in this document. -

SDCC Compiler User Guide

SDCC Compiler User Guide SDCC 4.1.11 $Date:: 2021-09-17 #$ $Revision: 12682 $ Contents 1 Introduction 7 1.1 About SDCC.............................................7 1.2 SDCC Suite Licenses.........................................8 1.3 Documentation............................................9 1.4 Typographic conventions.......................................9 1.5 Compatibility with previous versions.................................9 1.6 System Requirements......................................... 11 1.7 Other Resources............................................ 12 2 Installing SDCC 13 2.1 Configure Options........................................... 13 2.2 Install paths.............................................. 15 2.3 Search Paths.............................................. 16 2.4 Building SDCC............................................ 18 2.4.1 Building SDCC on Linux.................................. 18 2.4.2 Building SDCC on Mac OS X................................ 19 2.4.3 Cross compiling SDCC on Linux for Windows....................... 19 2.4.4 Building SDCC using Cygwin and Mingw32........................ 19 2.4.5 Building SDCC Using Microsoft Visual C++ 2010 (MSVC)................ 20 2.4.6 Windows Install Using a ZIP Package............................ 21 2.4.7 Windows Install Using the Setup Program.......................... 21 2.4.8 VPATH feature........................................ 21 2.5 Building the Documentation..................................... 22 2.6 Reading the Documentation.................................... -

Microprocessors Ez80190 Product Brief

eZ80® Microprocessors eZ80190 Product Brief PB005207-1103 Product Block Diagram • 3.3 V±0.3V supply voltage with 5V tolerant inputs eZ80190 MPU • 100-pin LQFP package 8KB MACC with 1KB 32-Bit • Up to 50MHz clock speed SRAM Dual-Port SRAM GPIO • Operating Temperature: – Standard Temperature Range: 0ºC to +70ºC 6 PRT WDT – Extended Temperature Range: –40ºC to 4 CS + +105ºC 2 DMA 2 UZI ZDI WSG • ZiLOG Debug Interface (ZDI) General Description Features The eZ80190 device is a high-speed, optimized The eZ80190 microprocessor is a member of pipeline architecture microprocessor, operating at ® ZiLOG’s eZ80 product family. It offers the fol- 50MHz. It is the first in a line of new eZ80® -based lowing features: standard products targeted toward embedded Inter- • Single-cycle instruction fetch, high-performance net applications. ® 50MHz eZ80 CPU core The eZ80® CPU is one of the fastest 8-bit CPUs • 8KB high-speed data SRAM available today, executing code four times faster than a standard Z80 operating at the same clock • 16x16-bit Multiply and 40-bit Accumulate with speed. In addition, the eZ80190 device includes a 1KB dual-port SRAM high-performance Multiply-Accumulator, ideal for • 32 bits of General-Purpose I/O signal processing. • Six Counter/Timers with prescalers The eZ80® CPU can operate in Z80-compatible (64 KB) mode, or full 24-bit (16 MB) addressing • Watch-Dog Timer mode. Considering both the increased clock speed • Four Chip Selects with individual Wait State and processor efficiency, the eZ80® CPU’s pro- generators cessing power rivals the performance of 16-bit microprocessors. -

2016 Media Kit

circuitcellar.com 2016 MEDIA KIT Circuit Cellar’s mission is to collect, select, and distribute need- to-know information on the topics of electrical engineering, embedded systems, programming, and computer applications. Circuit Cellar uses an assortment of print and electronic content-delivery platforms to reach a diverse international readership of professionals, academics, and electronics specialists who work with embedded, MCU-related technologies on a regular basis. Circuit Cellar’s aim is to help each reader become a well-rounded, multidisciplinary practitioner who can confidently bring innovative, cutting-edge engineering ideas to bear on any number of relevant tasks, problems, and technologies. Whether it’s microcontroller-based design tips or embedded programming advice, engineers rely on Circuit Cellar for solutions to all their electronics challenges. ADVERTISING Strategic Media Marketing, Inc. 2 Main Street, Gloucester, MA 01930 P: 978.281.7708 | Email: [email protected] EDITORIAL Circuit Cellar, Inc. 111 Founders Plaza, Suite 904, E. Hartford, CT 06108 P: 860.289.0800 | Email: [email protected] Scan to See an Issue @editor_cc @circuitcellar circuitcellar circuitcellar.com circuitcellar.com @editor_cc @circuitcellar circuitcellar circuitcellar.com ADVERTISING CALENDAR Issue Theme Space Close *Bonus Distribution Material Close Mailing Date 306 January Embedded Applications 11/10/15 *CES 2016; Embedded World 2016 11/13/15 12/23/15 307 February Wireless Communications 12/11/15 12/18/15 1/19/16 308 March Robotics