Klocwork V. 10.4 System Requirements System Requirements the Following System Configurations Are Required to Run the Klocwork Tools

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

08-02-2021 Agenda Packet.Pdf

AGENDA DELANO CITY COUNCIL REGULAR MEETING August 2, 2021 DELANO CITY HALL, 1015 – 11th Avenue 5:30 P.M. IN ACCORDANCE WITH THE GOVERNOR NEWSOM’S EXECUTIVE ORDER #N-08-21, THIS MEETING WILL BE CONDUCTED FULLY VIA TELECONFERENCE, DUE TO THE CURRENT RESTRICTIONS BY SAID ORDER AND CENTERS FOR DISEASES CONTROL AND PREVENTION (CDC) GUIDELINES. THE PUBLIC WILL HAVE ACCESS TO CALL IN, LISTEN TO THE MEETING AND PROVIDE PUBLIC COMMENT. IN ACCORDANCE WITH GOVERNOR NEWSOM’S EXECUTIVE ORDER N-08-21, THERE WILL NOT BE A PHYSICAL LOCATION FROM WHICH THE PUBLIC MAY ATTEND. IN ORDER TO CALL INTO TH E MEETING PLEASE SEE THE DIRECTIONS BELOW. CALL TO ORDER INVOCATION FLAG SALUTE ROLL CALL PRESENTATIONS AND AWARDS Featured Pet – Tabitha PUBLIC COMMENT: The public may address the Council on items which do not appear on the agenda. The Council cannot respond nor take action on items that do not appear on the agenda but may refer the item to staff for further study or for placement on a future agenda. Comments are limited to 3 minutes for each person and 15 minutes on each subject. Please state your name and address for the record. CONSENT AGENDA: The Consent Agenda consists of items that in staff’s opinion are routine and non-controversial. These items are approved in one motion unless a Councilmember or member of the public removes a particular item. 1) Authorization to waive the reading of any ordinance in its entirety and consenting to the reading of such ordinances by title only 2) Warrant Register in the amount of $3,044,398.54 3) Minutes of regular City Council Meeting of July 19, 2021 4) Acceptance and Approval of the City of Delano Quarterly Investment Report 5) Resolution adopting the 2020-2021 Kern Multi-Jurisdiction Hazard Mitigation Plan (MJHMP) 6) Approval of agreement with Youth Educational Sports, Inc. -

Fill Your Boots: Enhanced Embedded Bootloader Exploits Via Fault Injection and Binary Analysis

IACR Transactions on Cryptographic Hardware and Embedded Systems ISSN 2569-2925, Vol. 2021, No. 1, pp. 56–81. DOI:10.46586/tches.v2021.i1.56-81 Fill your Boots: Enhanced Embedded Bootloader Exploits via Fault Injection and Binary Analysis Jan Van den Herrewegen1, David Oswald1, Flavio D. Garcia1 and Qais Temeiza2 1 School of Computer Science, University of Birmingham, UK, {jxv572,d.f.oswald,f.garcia}@cs.bham.ac.uk 2 Independent Researcher, [email protected] Abstract. The bootloader of an embedded microcontroller is responsible for guarding the device’s internal (flash) memory, enforcing read/write protection mechanisms. Fault injection techniques such as voltage or clock glitching have been proven successful in bypassing such protection for specific microcontrollers, but this often requires expensive equipment and/or exhaustive search of the fault parameters. When multiple glitches are required (e.g., when countermeasures are in place) this search becomes of exponential complexity and thus infeasible. Another challenge which makes embedded bootloaders notoriously hard to analyse is their lack of debugging capabilities. This paper proposes a grey-box approach that leverages binary analysis and advanced software exploitation techniques combined with voltage glitching to develop a powerful attack methodology against embedded bootloaders. We showcase our techniques with three real-world microcontrollers as case studies: 1) we combine static and on-chip dynamic analysis to enable a Return-Oriented Programming exploit on the bootloader of the NXP LPC microcontrollers; 2) we leverage on-chip dynamic analysis on the bootloader of the popular STM8 microcontrollers to constrain the glitch parameter search, achieving the first fully-documented multi-glitch attack on a real-world target; 3) we apply symbolic execution to precisely aim voltage glitches at target instructions based on the execution path in the bootloader of the Renesas 78K0 automotive microcontroller. -

Managing Projects with GNU Make, Third Edition by Robert Mecklenburg

ManagingProjects with GNU Make Other resources from O’Reilly Related titles Unix in a Nutshell sed and awk Unix Power Tools lex and yacc Essential CVS Learning the bash Shell Version Control with Subversion oreilly.com oreilly.com is more than a complete catalog of O’Reilly books. You’ll also find links to news, events, articles, weblogs, sample chapters, and code examples. oreillynet.com is the essential portal for developers interested in open and emerging technologies, including new platforms, pro- gramming languages, and operating systems. Conferences O’Reilly brings diverse innovators together to nurture the ideas that spark revolutionary industries. We specialize in document- ing the latest tools and systems, translating the innovator’s knowledge into useful skills for those in the trenches. Visit con- ferences.oreilly.com for our upcoming events. Safari Bookshelf (safari.oreilly.com) is the premier online refer- ence library for programmers and IT professionals. Conduct searches across more than 1,000 books. Subscribers can zero in on answers to time-critical questions in a matter of seconds. Read the books on your Bookshelf from cover to cover or sim- ply flip to the page you need. Try it today with a free trial. THIRD EDITION ManagingProjects with GNU Make Robert Mecklenburg Beijing • Cambridge • Farnham • Köln • Sebastopol • Tokyo Managing Projects with GNU Make, Third Edition by Robert Mecklenburg Copyright © 2005, 1991, 1986 O’Reilly Media, Inc. All rights reserved. Printed in the United States of America. Published by O’Reilly Media, Inc., 1005 Gravenstein Highway North, Sebastopol, CA 95472. O’Reilly books may be purchased for educational, business, or sales promotional use. -

Red Hat Enterprise Linux 6 Developer Guide

Red Hat Enterprise Linux 6 Developer Guide An introduction to application development tools in Red Hat Enterprise Linux 6 Dave Brolley William Cohen Roland Grunberg Aldy Hernandez Karsten Hopp Jakub Jelinek Developer Guide Jeff Johnston Benjamin Kosnik Aleksander Kurtakov Chris Moller Phil Muldoon Andrew Overholt Charley Wang Kent Sebastian Red Hat Enterprise Linux 6 Developer Guide An introduction to application development tools in Red Hat Enterprise Linux 6 Edition 0 Author Dave Brolley [email protected] Author William Cohen [email protected] Author Roland Grunberg [email protected] Author Aldy Hernandez [email protected] Author Karsten Hopp [email protected] Author Jakub Jelinek [email protected] Author Jeff Johnston [email protected] Author Benjamin Kosnik [email protected] Author Aleksander Kurtakov [email protected] Author Chris Moller [email protected] Author Phil Muldoon [email protected] Author Andrew Overholt [email protected] Author Charley Wang [email protected] Author Kent Sebastian [email protected] Editor Don Domingo [email protected] Editor Jacquelynn East [email protected] Copyright © 2010 Red Hat, Inc. and others. The text of and illustrations in this document are licensed by Red Hat under a Creative Commons Attribution–Share Alike 3.0 Unported license ("CC-BY-SA"). An explanation of CC-BY-SA is available at http://creativecommons.org/licenses/by-sa/3.0/. In accordance with CC-BY-SA, if you distribute this document or an adaptation of it, you must provide the URL for the original version. Red Hat, as the licensor of this document, waives the right to enforce, and agrees not to assert, Section 4d of CC-BY-SA to the fullest extent permitted by applicable law. -

MSP430FR2433 Mixed-Signal Microcontroller

Product Order Technical Tools & Support & Folder Now Documents Software Community MSP430FR2433 SLASE59C –OCTOBER 2015–REVISED AUGUST 2018 MSP430FR2433 Mixed-Signal Microcontroller 1 Device Overview 1.1 Features 1 • Embedded Microcontroller Storage – 16-Bit RISC Architecture – 1015 Write Cycle Endurance – Clock Supports Frequencies up to 16 MHz – Radiation Resistant and Nonmagnetic – Wide Supply Voltage Range From 3.6 V Down – High FRAM-to-SRAM Ratio, up to 4:1 to 1.8 V (Minimum Supply Voltage is Restricted • Clock System (CS) by SVS Levels, See the SVS Specifications) – On-Chip 32-kHz RC Oscillator (REFO) • Optimized Ultra-Low-Power Modes – On-Chip 16-MHz Digitally Controlled Oscillator – Active Mode: 126 µA/MHz (Typical) (DCO) With Frequency-Locked Loop (FLL) – Standby: <1 µA With VLO – ±1% Accuracy With On-Chip Reference at – LPM3.5 Real-Time Clock (RTC) Counter With Room Temperature 32768-Hz Crystal: 730 nA (Typical) – On-Chip Very Low-Frequency 10-kHz Oscillator – Shutdown (LPM4.5): 16 nA (Typical) (VLO) • High-Performance Analog – On-Chip High-Frequency Modulation Oscillator – 8-Channel 10-Bit Analog-to-Digital Converter (MODOSC) (ADC) – External 32-kHz Crystal Oscillator (LFXT) – Internal 1.5-V Reference – Programmable MCLK Prescalar of 1 to 128 – Sample-and-Hold 200 ksps – SMCLK Derived from MCLK With • Enhanced Serial Communications Programmable Prescalar of 1, 2, 4, or 8 – Two Enhanced Universal Serial Communication • General Input/Output and Pin Functionality Interfaces (eUSCI_A) Support UART, IrDA, and – Total of 19 I/Os on -

Schedule 14A Employee Slides Supertex Sunnyvale

UNITED STATES SECURITIES AND EXCHANGE COMMISSION Washington, D.C. 20549 SCHEDULE 14A Proxy Statement Pursuant to Section 14(a) of the Securities Exchange Act of 1934 Filed by the Registrant Filed by a Party other than the Registrant Check the appropriate box: Preliminary Proxy Statement Confidential, for Use of the Commission Only (as permitted by Rule 14a-6(e)(2)) Definitive Proxy Statement Definitive Additional Materials Soliciting Material Pursuant to §240.14a-12 Supertex, Inc. (Name of Registrant as Specified In Its Charter) Microchip Technology Incorporated (Name of Person(s) Filing Proxy Statement, if other than the Registrant) Payment of Filing Fee (Check the appropriate box): No fee required. Fee computed on table below per Exchange Act Rules 14a-6(i)(1) and 0-11. (1) Title of each class of securities to which transaction applies: (2) Aggregate number of securities to which transaction applies: (3) Per unit price or other underlying value of transaction computed pursuant to Exchange Act Rule 0-11 (set forth the amount on which the filing fee is calculated and state how it was determined): (4) Proposed maximum aggregate value of transaction: (5) Total fee paid: Fee paid previously with preliminary materials. Check box if any part of the fee is offset as provided by Exchange Act Rule 0-11(a)(2) and identify the filing for which the offsetting fee was paid previously. Identify the previous filing by registration statement number, or the Form or Schedule and the date of its filing. (1) Amount Previously Paid: (2) Form, Schedule or Registration Statement No.: (3) Filing Party: (4) Date Filed: Filed by Microchip Technology Incorporated Pursuant to Rule 14a-12 of the Securities Exchange Act of 1934 Subject Company: Supertex, Inc. -

Zilog’S Ez80acclaim!™ Product Family, Which Offers On-Chip Flash Versions of Zilog’S Ez80® • 3.0–3.6 V Supply Voltage with 5 V Tolerant Inputs Processor Core

eZ80Acclaim!™ Flash Microcontrollers eZ80F91 Product Brief PB013502-0104 Product Block Diagram • I2C with independent clock rate generator • SPI with independent clock rate generator eZ80F91 MCU • Four Counter/Timers with prescalers supporting event counting, input capture, output compare, and 256 KB Flash + 32-Bit GPIO PWM modes 512 B Flash • Watch-Dog Timer with internal RC clocking 10/100 Mbps option 8KB SRAM Ethernet MAC • Real-time clock with on-chip 32kHz oscillator, 8KB Frame Buffer selectable 50/60Hz input, and separate RTC_VDD pin for battery backup. Infrared 2 • Glueless external memory interface with 4 Chip- Encoder/ 2 UART I C SPI Selects/Wait-State Generators and external WAIT Decoder input pin. Supports Intel and Motorola buses. Real-Time • JTAG Interface supporting emulation features 4 PRT WDT Clock • Low-power PLL and on-chip oscillator • Programmable-priority vectored interrupts, non- 4 CS JTAG ZDI PLL maskable interrupts, and interrupt controller +WSG • New DMA-like eZ80® CPU instructions • Power management features supporting HALT/ Features SLEEP modes and selective peripheral power- down controls The eZ80F91 microcontroller is a member of • 144-pin BGA or 144-pin LQFP package ZiLOG’s eZ80Acclaim!™ product family, which offers on-chip Flash versions of ZiLOG’s eZ80® • 3.0–3.6 V supply voltage with 5 V tolerant inputs processor core. The eZ80F91 offers the following • Operating Temperature Ranges: features: – Standard: 0ºC to +70ºC • 50MHz High-Performance eZ80® CPU – Extended: –40ºC to +105ºC • 256 KB Flash Program Memory plus extra 512B device configuration Flash memory General Description • 32 bits of General-Purpose I/O The eZ80F91 device is an industry first, featuring a • 16K B total on-chip high-speed SRAM: high-performance 8-bit microcontroller with an integrated 10/100 BaseT Ethernet Media Access – 8KB for general-purpose use controller (EMAC). -

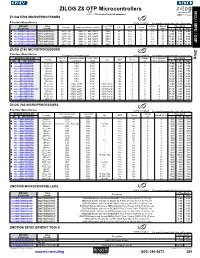

ZILOG Z8 OTP Microcontrollers MCU / MPU / DSP This Product Is Rohs Compliant

ZILOG Z8 OTP Microcontrollers DSP MPU / MCU / This product is RoHS compliant. ZILOG EZ80 MICROPROCESSORS ♦ Surface Mount Device For quantities greater than listed, call for quote. MOUSER Zilog Core CPU Voltage Speed Price Each Package Communications Controller I/O WDT Timers STOCK NO. Part No. Used (V) (MHz) 1 25 100 ♦ 692-EZ80L92AZ020EG EZ80L92AZ020EC LQFP-100 DMA, I2C, SPI, UART EZ80 24 Yes 6 3.3 20 9.29 9.10 8.63 ♦ 692-EZ80L92AZ020SG EZ80L92AZ020SC LQFP-100 DMA, I2C, SPI, UART EZ80 24 Yes 6 3.3 20 8.08 7.78 7.50 ♦ 692-EZ80L92AZ050EG EZ80L92AZ050EC LQFP-100 DMA, I2C, SPI, UART EZ80 24 Yes 6 3.3 50 10.21 9.75 9.49 ♦ 692-EZ80L92AZ050SG EZ80L92AZ050SC LQFP-100 DMA, I2C, SPI, UART EZ80 24 Yes 6 3.3 50 8.89 8.54 8.26 ♦ 692-EZ80190AZ050SG EZ80190AZ050SC LQFP-100 DMA, I2C, SPI, UART EZ80 32 Yes 6 3.3 50 12.03 11.59 11.17 ♦ 692-EZ80190AZ050EG EZ80190AZ050EC LQFP-100 DMA, I2C, SPI, UART EZ80 32 Yes 6 3.3 50 13.82 13.28 12.84 ZILOG Z180 MICROPROCESSORS Zilog ♦Surface Mount Device *See above for development tools. For quantities greater than listed, call for quote. MOUSER STOCK NO. Speed Communications Core CPU Voltage Development Price Each Package I/O WDT Timers Mfr. Mfr. Part No. (MHz) Controller Used (V) Tools Available 1 25 100 ♦ 692-Z8018006VSG PLCC-68 6 CPU Z180 - No 2 5 - 8.40 7.36 6.01 ♦ 692-Z8018006VEG PLCC-68 6 CPU Z180 - No 2 5 - 10.00 8.55 7.14 692-Z8018006PSG DIP-64 6 CPU Z180 - No 2 5 - 8.40 7.36 6.01 692-Z8018006PEG DIP-64 6 CPU Z180 - No 2 5 - 10.00 8.55 7.14 692-Z8018008PSG DIP-64 8 CPU Z180 - No 2 5 - 8.75 7.38 6.25 ♦ 692-Z8018008VSG -

Embedded Market Study, 2013

2013 EMBEDDED MARKET STUDY Essential to Engineers DATASHEETS.COM | DESIGNCON | DESIGN EAST & DESIGN WEST | EBN | EDN | EE TIMES | EMBEDDED | PLANET ANALOG | TECHONLINE | TEST & MEASUREMENT WORLD 2013 Embedded Market Study 2 UBM Tech Electronics’ Brands Unparalleled Reach & Experience UBM Tech Electronics is the media and marketing services solution for the design engineering and electronics industry. Our audience of over 2,358,928 (as of March 5, 2013) are the executives and engineers worldwide who design, develop, and commercialize technology. We provide them with the essentials they need to succeed: news and analysis, design and technology, product data, education, and fun. Copyright © 2013 by UBM. All rights reserved. 2013 Embedded Market Study 5 Purpose and Methodology • Purpose: To profile the findings of the 2013 results of EE Times Group annual comprehensive survey of the embedded systems markets worldwide. Findings include types of technology used, all aspects of the embedded development process, tools used, work environment, applications, methods and processes, operating systems used, reasons for using and not using chips and technology, and brands and chips currently used by or being considered by embedded developers. Many questions in this survey have been trended over two to five years. • Methodology: A web-based online survey instrument based on the previous year’s survey was developed and implemented by independent research company Wilson Research Group from January 18, 2013 to February 13, 2013 by email invitation • Sample: E-mail invitations were sent to subscribers to UBM/EE Times Group Embedded Brands with one reminder invitation. Each invitation included a link to the survey. • Returns: 2,098 valid respondents for an overall confidence of 95% +/- 2.13%. -

Using Energia (Arduino)

Using Energia (Arduino) Introduction This chapter of the MSP430 workshop explores Energia, the Arduino port for the Texas Instruments Launchpad kits. After a quick definition and history of Arduino and Energia, we provide a quick introduction to Wiring – the language/library used by Arduino & Energia. Most of the learning comes from using the Launchpad board along with the Energia IDE to light LED’s, read switches and communicate with your PC via the serial connection. Learning Objectives, Requirements, Prereq’s Prerequisites & Objectives Prerequisites Basic knowledge of C language Basic understanding of using a C library and header files This chapter doesn’t explain clock, interrupt, and GPIO features in detail, this is left to the other chapters in the MSP430 workshop Requirements - Tools and Software Hardware Windows (XP, 7, 8) PC with available USB port MSP430F5529 Launchpad Software Already installed, if you Energia Download have installed CCSv5.x Launchpad drivers (Optional) MSP430ware / Driverlib Objectives Define ‘Arduino’ and describe what is was created for Define ‘Energia’ and explain what it is ‘forked’ from Install Energia, open and run included example sketches Use serial communication between the board & PC Add an external interrupt to an Energia sketch Modify CPU registers from an Energia sketch MSP430 Workshop - Using Energia (Arduino) 8 - 1 What is Arduino Chapter Topics Using Energia (Arduino) ............................................................................................................ -

8-Bit All Flash 78K0 Microcontrollers 78K0S

For further information, please contact: NEC Electronics Corporation 1753, Shimonumabe, Nakahara-ku, Kawasaki, Kanagawa 211-8668, Japan Tel: 044-435-5111 http://www.necel.com/ [America] [Europe] [Asia & Oceania] NEC Electronics America, Inc. NEC Electronics (Europe) GmbH NEC Electronics (China) Co., Ltd 8-bit All Flash 2880 Scott Blvd. Arcadiastrasse 10 7th Floor, Quantum Plaza, No. 27 ZhiChunLu Haidian Santa Clara, CA 95050-2554, U.S.A. 40472 Düsseldorf, Germany District, Beijing 100083, P.R.China Tel: 408-588-6000 Tel: 0211-65030 Tel: 010-8235-1155 800-366-9782 http://www.eu.necel.com/ http://www.cn.necel.com/ http://www.am.necel.com/ Hanover Office Shanghai Branch Podbielskistrasse 166 B Room 2509-2510, Bank of ChinaTower, 30177 Hannover 200Y incheng Road Central, Tel: 0 511 33 40 2-0 Pudong New Area, Shanghai, P.R.China P.C:200120 Tel:021-5888-5400 Munich Office http://www.cn.necel.com/ Werner-Eckert-Strasse 9 81829 München Shenzhen Branch Tel: 0 89 92 10 03-0 Unit 01, 39/F, Excellence Times Square Building, Stuttgart Office No. 4068 Yi Tian Road, Futian District, Shenzhen, Industriestrasse 3 P.R.China P.C:518048 70565 Stuttgart Tel:0755-8282-9800 Tel: 0 711 99 01 0-0 http://www.cn.necel.com/ United Kingdom Branch NEC Electronics Hong Kong Ltd. Cygnus House, Sunrise Parkway Unit 1601-1613, 16/F., Tower 2, Grand Century Place, Linford Wood, Milton Keynes 193 Prince Edward Road West, Mongkok, Kowloon, Hong Kong MK14 6NP, U.K. Tel: 2886-9318 Tel: 01908-691-133 http://www.hk.necel.com/ Succursale Française 9, rue Paul Dautier, B.P. -

Design Considerations When Using the MSP430 Graphics Library, and Provides an Example of Implementation and Optimization

www.ti.com 1 Trademarks MSP430, MSP430Ware are trademarks of Texas Instruments. Stellaris is a registered trademark of Texas Instruments. All other trademarks are the property of their respective owners. SLAA548–October 2012 1 Submit Documentation Feedback Copyright © 2012, Texas Instruments Incorporated Application Report SLAA548–October 2012 Design Considerations When Using MSP430 Graphics Library Michael Stein ABSTRACT LCDs are a growing commodity in today’s market with products as diverse as children’s toys to medical devices. Modern LCDs, along with the graphics displayed on them, are growing in complexity. A graphics library can simplify and accelerate development while creating the desired user experience. TI provides the MSP430 Graphics Library for use in developing products with the MSP430™ MCU. This application report describes design considerations when using the MSP430 Graphics Library, and provides an example of implementation and optimization. Project collateral discussed in this application report can be downloaded from the following URL: www.ti.com/lit/zip/SLAA548. Contents 2 Introduction to the MSP430 Graphics Library............................................................................ 2 3 System Overview ............................................................................................................ 3 4 Hardware Implementation - LCD Bus Type .............................................................................. 4 5 Software Implementation- LCD Display Driver Layer ..................................................................