Low Power Embedded Software Optimization for the Nuttx RTOS

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

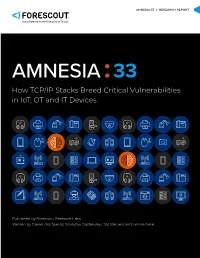

AMNESIA 33: How TCP/IP Stacks Breed Critical Vulnerabilities in Iot

AMNESIA:33 | RESEARCH REPORT How TCP/IP Stacks Breed Critical Vulnerabilities in IoT, OT and IT Devices Published by Forescout Research Labs Written by Daniel dos Santos, Stanislav Dashevskyi, Jos Wetzels and Amine Amri RESEARCH REPORT | AMNESIA:33 Contents 1. Executive summary 4 2. About Project Memoria 5 3. AMNESIA:33 – a security analysis of open source TCP/IP stacks 7 3.1. Why focus on open source TCP/IP stacks? 7 3.2. Which open source stacks, exactly? 7 3.3. 33 new findings 9 4. A comparison with similar studies 14 4.1. Which components are typically flawed? 16 4.2. What are the most common vulnerability types? 17 4.3. Common anti-patterns 22 4.4. What about exploitability? 29 4.5. What is the actual danger? 32 5. Estimating the reach of AMNESIA:33 34 5.1. Where you can see AMNESIA:33 – the modern supply chain 34 5.2. The challenge – identifying and patching affected devices 36 5.3. Facing the challenge – estimating numbers 37 5.3.1. How many vendors 39 5.3.2. What device types 39 5.3.3. How many device units 40 6. An attack scenario 41 6.1. Other possible attack scenarios 44 7. Effective IoT risk mitigation 45 8. Conclusion 46 FORESCOUT RESEARCH LABS RESEARCH REPORT | AMNESIA:33 A note on vulnerability disclosure We would like to thank the CERT Coordination Center, the ICS-CERT, the German Federal Office for Information Security (BSI) and the JPCERT Coordination Center for their help in coordinating the disclosure of the AMNESIA:33 vulnerabilities. -

Zilog’S Ez80acclaim!™ Product Family, Which Offers On-Chip Flash Versions of Zilog’S Ez80® • 3.0–3.6 V Supply Voltage with 5 V Tolerant Inputs Processor Core

eZ80Acclaim!™ Flash Microcontrollers eZ80F91 Product Brief PB013502-0104 Product Block Diagram • I2C with independent clock rate generator • SPI with independent clock rate generator eZ80F91 MCU • Four Counter/Timers with prescalers supporting event counting, input capture, output compare, and 256 KB Flash + 32-Bit GPIO PWM modes 512 B Flash • Watch-Dog Timer with internal RC clocking 10/100 Mbps option 8KB SRAM Ethernet MAC • Real-time clock with on-chip 32kHz oscillator, 8KB Frame Buffer selectable 50/60Hz input, and separate RTC_VDD pin for battery backup. Infrared 2 • Glueless external memory interface with 4 Chip- Encoder/ 2 UART I C SPI Selects/Wait-State Generators and external WAIT Decoder input pin. Supports Intel and Motorola buses. Real-Time • JTAG Interface supporting emulation features 4 PRT WDT Clock • Low-power PLL and on-chip oscillator • Programmable-priority vectored interrupts, non- 4 CS JTAG ZDI PLL maskable interrupts, and interrupt controller +WSG • New DMA-like eZ80® CPU instructions • Power management features supporting HALT/ Features SLEEP modes and selective peripheral power- down controls The eZ80F91 microcontroller is a member of • 144-pin BGA or 144-pin LQFP package ZiLOG’s eZ80Acclaim!™ product family, which offers on-chip Flash versions of ZiLOG’s eZ80® • 3.0–3.6 V supply voltage with 5 V tolerant inputs processor core. The eZ80F91 offers the following • Operating Temperature Ranges: features: – Standard: 0ºC to +70ºC • 50MHz High-Performance eZ80® CPU – Extended: –40ºC to +105ºC • 256 KB Flash Program Memory plus extra 512B device configuration Flash memory General Description • 32 bits of General-Purpose I/O The eZ80F91 device is an industry first, featuring a • 16K B total on-chip high-speed SRAM: high-performance 8-bit microcontroller with an integrated 10/100 BaseT Ethernet Media Access – 8KB for general-purpose use controller (EMAC). -

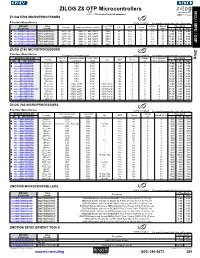

ZILOG Z8 OTP Microcontrollers MCU / MPU / DSP This Product Is Rohs Compliant

ZILOG Z8 OTP Microcontrollers DSP MPU / MCU / This product is RoHS compliant. ZILOG EZ80 MICROPROCESSORS ♦ Surface Mount Device For quantities greater than listed, call for quote. MOUSER Zilog Core CPU Voltage Speed Price Each Package Communications Controller I/O WDT Timers STOCK NO. Part No. Used (V) (MHz) 1 25 100 ♦ 692-EZ80L92AZ020EG EZ80L92AZ020EC LQFP-100 DMA, I2C, SPI, UART EZ80 24 Yes 6 3.3 20 9.29 9.10 8.63 ♦ 692-EZ80L92AZ020SG EZ80L92AZ020SC LQFP-100 DMA, I2C, SPI, UART EZ80 24 Yes 6 3.3 20 8.08 7.78 7.50 ♦ 692-EZ80L92AZ050EG EZ80L92AZ050EC LQFP-100 DMA, I2C, SPI, UART EZ80 24 Yes 6 3.3 50 10.21 9.75 9.49 ♦ 692-EZ80L92AZ050SG EZ80L92AZ050SC LQFP-100 DMA, I2C, SPI, UART EZ80 24 Yes 6 3.3 50 8.89 8.54 8.26 ♦ 692-EZ80190AZ050SG EZ80190AZ050SC LQFP-100 DMA, I2C, SPI, UART EZ80 32 Yes 6 3.3 50 12.03 11.59 11.17 ♦ 692-EZ80190AZ050EG EZ80190AZ050EC LQFP-100 DMA, I2C, SPI, UART EZ80 32 Yes 6 3.3 50 13.82 13.28 12.84 ZILOG Z180 MICROPROCESSORS Zilog ♦Surface Mount Device *See above for development tools. For quantities greater than listed, call for quote. MOUSER STOCK NO. Speed Communications Core CPU Voltage Development Price Each Package I/O WDT Timers Mfr. Mfr. Part No. (MHz) Controller Used (V) Tools Available 1 25 100 ♦ 692-Z8018006VSG PLCC-68 6 CPU Z180 - No 2 5 - 8.40 7.36 6.01 ♦ 692-Z8018006VEG PLCC-68 6 CPU Z180 - No 2 5 - 10.00 8.55 7.14 692-Z8018006PSG DIP-64 6 CPU Z180 - No 2 5 - 8.40 7.36 6.01 692-Z8018006PEG DIP-64 6 CPU Z180 - No 2 5 - 10.00 8.55 7.14 692-Z8018008PSG DIP-64 8 CPU Z180 - No 2 5 - 8.75 7.38 6.25 ♦ 692-Z8018008VSG -

B.Tech. CSE CBCS W.E.F. July, 2019

The Curriculum Book BACHELOR OF TECHNOLOGY I tn COMPUTER SCIENCE AND ENGINEERING FOUR YEAR PROGRAMME Choice Based Credit System vy. e. f. JuIy ZAlg (70:30) . ,_i 1 .I DEPARTMENT OF COMPUTER SCIENCE AI\D BNGINEERING GURU JAMBHESHWAR UNIVERSITY OF SCIENCE & TECHNOLOGY tr j HISAR.125OO1, HARYANA scheme & syllabi2019 GURU JAMBHESHWAR UNIVERSITY OF SCIENCE & TECHNOLOGY, HISAR (Established by state Legistature 'A',Grade,. Act 17 of lggs) NA.AC Accreditid state Govt. university Acad /AC-ilt,tFqc_1 Vot. 3DAlgJf 7 7 Dated: Ulfr:f To The Controller of Examinations GJUS&T, Hisar. sub: Approval of scheme of examination & syllabi of various B.Tech. progralle(sJ being run in university Teachiig Departments as welt as affil iated En g i neeri ng c oilege(s)/r nstitutelsy. AND Recommendations of Faculty Engineering open & Technology regarding Elective, Format of Minor Quu.ti;;-of papei Mooc strength for programme courses, minimum Erective, semester Registration etc. Sir, I am directed to inform you that the vice-chancellor, on the recommendations of the Faculty of Engineering & Technology, vide resolutions no. 2to 13 in its meeting held on 1B 07'2a19, is pleased to approve . the following scheme & syllabi of B.Tech. programme(s) w'e'f' the academic session batch / mentioned against each being run in University Teaching Departments as well as affiliated colleges/institutions and recommendations of Faculty of Engineering & Technolcgy, regarding open Elective, format of Minor Question Paper, Mooc courses, minimum strength for programme Elective' semester Registration etc under sectio n 11(5) in anticipation of approvat of the Acadenric councir of the University Act, 1995.- 1' B'Tech (Printing Technology), B Tec.h (Packaging Technology) (Printing & Packaging i""r'norogD-ath ""un',i""o,,,& B.Tech. -

Data Acquisition

#147 October 2002 www.circuitcellar.com CIRCUIT CELLAR® THE MAGAZINE FOR COMPUTER APPLICATIONS DATA ACQUISITION 2-D Or Not 2-D Solar-Powered Robot The LED Alternative Mad DashWWW.GiURUMELE.Hi2.RO For Flash Cash Contest Primer 10> 7925274 75349 $4.95 U.S. ($5.95 Canada) WWW.GiURUMELE.Hi2.RO WWW.GiURUMELE.Hi2.RO Digital Oscilloscopes • 2 Channel Digital Oscilloscope DSO-2102S $525 • 100 MSa/s max single shot rate DSO-2102M $650 • 32K samples per channel Each includes Oscilloscope, • Advanced Triggering Probes, Interface Cable, Power • Only 9 oz and 6.3” x 3.75” x 1.25” Adapter, and software for • Small, Lightweight, and Portable Win95/98, WinNT, Win2000 • Parallel Port interface to PC and DOS. • Advanced Math options • FFT Spectrum Analyzer options Logic Analyzers • 40 to 160 channels • 24 Channel Logic Analyzer • up to 500 MSa/s • 100MSa/S max sample rate • Variable Threshold • Variable Threshold Voltage • 8 External Clocks • Large 128k Buffer • 16 Level Triggering • Small, Lightweight and Portable • up to 512KWWW.GiURUMELE.Hi2.RO samples/ch • Only 4 oz and 4.75” x 2.75” x 1” • Optional Parallel Interface • Parallel Port Interface to PC • Optional 100 MSa/s Pattern Generator • Trigger Out • Windows 95/98 Software LA4240-32K (200MHz, 40CH) $1350 LA4280-32K (200MHz, 80CH) $2000 LA2124-128K (100MSa/s, 24CH) LA4540-128K (500MHz, 40CH) $1900 Clips, Wires, Interface Cable, AC LA4580-128K (500MHz, 80CH) $2800 Adapter and Software $800 LA45160-128K (500MHz, 160CH) $7000 All prices include Pods and Software www.LinkIns4.com Link Instruments • 369 Passaic Ave • Suite 100 • Fairfield, NJ 07004 • (973) 808-8990 • Fax (973) 808-8786 WWW.GiURUMELE.Hi2.RO TASK MANAGER EDITORIAL DIRECTOR/FOUNDER CHIEF FINANCIAL OFFICER Be a Contender Steve Ciarcia Jeannette Ciarcia MANAGING EDITOR Jennifer Huber CUSTOMER SERVICE Elaine Johnston TECHNICAL EDITOR C.J. -

TCP/IP Enabled Legos

TCP/IP enabled legOS Student research project University of applied sciences Hamburg March 3, 2002 Olaf Christ [email protected] 1 Abstract In recent years, the interest for connecting small devices such as sensors or embedded systems into an existing network infrastructure (such as the global Internet) has steadily increased. Such devices often have very limited CPU and memory resources and may not be able to run an instance of the TCP/IP protocol suite. This document describes how to use the uIP TCP/IP stack, written by Adam Dunkels, on LEGO’s RCX Mindstorm platform, a very small device / toy powered by a h8300 Hitachi microcontroller with very limited RAM (32K) and processing power. Still, it is powerful enough to run alternative operating systems such as LegOS or even a tiny Java VM as a replacement of the original firmware. The advanced user is usually not satisfied with the original firmware due to its extremely limited capabilities in terms of executing complex code and the very limited number of variables. The uIP TCP/IP stack is intended for embedded systems running on low-end 8 or 16-bit microcontrollers. The code size of uIP is an order of a magnitude smaller than similar generic TCP/IP stacks available today. The uIP code and an up-to-date version of the uIP documentation can be downloaded from the uIP homepage maintained by Adam Dunkels. 2 3 Preface This work has been carried out as a student research project at the University of applied sciences Hamburg in Hamburg, Germany. The proposal was given to me by my supervisor Prof. -

Natalia Nikolaevna Shusharina Maxin.Pmd

BIOSCIENCES BIOTECHNOLOGY RESEARCH ASIA, September 2016. Vol. 13(3), 1523-1536 Development of the Brain-computer Interface Based on the Biometric Control Channels and Multi-modal Feedback to Provide A Human with Neuro-electronic Systems and Exoskeleton Structures to Compensate the Motor Functions Natalia Nikolaevna Shusharina1, Evgeny Anatolyevich Bogdanov1, Stepan Aleksandrovich Botman1, Ekaterina Vladimirovna Silina2, Victor Aleksandrovich Stupin3 and Maksim Vladimirovich Patrushev1 1Immanuel Kant Baltic Federal University (IKBFU), Nevskogo Str., 14, Kaliningrad, 236041, Russia 2I.M. Sechenov First Moscow State Medical University (First MSMU), Trubetskaya str, 8, Moscow, 119991, Russia 3Pirogov´s Russian National Research Medical University (RNRMU), Ostrovityanova str, 1, Moscow, 117997, Russia http://dx.doi.org/10.13005/bbra/2295 (Received: 15 June 2016; accepted: 05 August 2016) The aim of this paper is to create a multi-functional neuro-device and to study the possibilities of long-term monitoring of several physiological parameters of an organism controlled by brain activity with transmitting the data to the exoskeleton. To achieve this goal, analytical review of modern scientific-and-technical, normative, technical, and medical literature involving scientific and technical problems has been performed; the research area has been chosen and justified, including the definition of optimal electrodes and their affixing to the body of the patient, the definition of the best suitable power source and its operation mode, the definition of the best suitable useful signal amplifiers, and a system of filtering off external noises. A neuro-device mock-up has been made for recognizing electrophysiological signals and transmitting them to the exoskeleton, also the software has been written. -

Evaluation of Open Source Operating Systems for Safety-Critical Applications Master’S Thesis in Embedded Electronic System Design

Evaluation of open source operating systems for safety-critical applications Master’s thesis in Embedded Electronic System Design Petter Sainio Berntsson Department of Computer Science and Engineering CHALMERS UNIVERSITY OF TECHNOLOGY UNIVERSITY OF GOTHENBURG Gothenburg, Sweden 2017 MASTER’S THESIS 2017 Evaluation of open source operating systems for Safety-critical applications Petter Sainio Berntsson Department of Computer Science and Engineering Chalmers University of Technology University of Gothenburg Gothenburg, Sweden 2017 Evaluation of open source operating systems for safety-critical applications Petter Sainio Berntsson © Petter Sainio Berntsson, 2017 Examiner: Per Larsson-Edefors Chalmers University of Technology Department of Computer Science and Engineering Academic supervisor: Jan Jonsson Chalmers University of Technology Department of Computer Science and Engineering Industrial supervisors: Lars Strandén RISE Research Institutes of Sweden Dependable Systems Fredrik Warg RISE Research Institutes of Sweden Dependable Systems Master’s Thesis 2017 Department of Computer Science and Engineering Chalmers University of Technology University of Gothenburg SE-412 96 Gothenburg Telephone +46(0) 31 772 1000 Abstract Today many embedded applications will have to handle multitasking with real-time time constraints and the solution for handling multitasking is to use a real-time operating system for scheduling and managing the real-time tasks. There are many different open source real-time operating systems available and the use of open source software for safety-critical applications is considered highly interesting by industries such as medical, aerospace and automotive as it enables a shorter time to market and lower development costs. If one would like to use open source software in a safety-critical context one would have to provide evidence that the software being used fulfills the requirement put forth by the industry specific standard for functional safety, such as the ISO 26262 standard for the automotive industry. -

Portability Techniques for Embedded Systems Data Management

Portability Techniques for Embedded Systems Data Management McObject LLC st 33309 1 Way South Suite A-208 Federal Way, WA 98003 Phone: 425-888-8505 E-mail: [email protected] www.mcobject.com Copyright 2020, McObject LLC Whether an embedded systems database is developed for a specific application or as a commercial product, portability matters. Most embedded data management code is still “homegrown,” and when external forces drive an operating system or hardware change, data management code portability saves significant development time. This is especially important since increasingly, hardware’s lifespan is shorter than firmware’s. For database vendors, compatibility with the dozens of hardware designs, operating systems and compilers used in embedded systems provides a major marketing advantage. For real-time embedded systems, database code portability means more than the ability to compile and execute on different platforms: portability strategies also tie into performance. Software developed for a specific OS, hardware platform and compiler often performs poorly when moved to a new environment, and optimizations to remedy this are very time-consuming. Truly portable embedded systems data management code carries its optimization with it, requiring the absolute minimum adaptation to deliver the best performance in new environments. Using Standard C Writing portable code traditionally begins with a commitment to use only ANSI C. But this is easier said than done. Even code written with the purest ANSI C intentions frequently makes assumptions about the target hardware and operating environment. In addition, programmers often tend to use available compiler extensions. Many of the extensions – prototypes, stronger type- checking, etc, – enhance portability, but others may add to platform dependencies. -

Installing Klocwork Insight

Installation and Upgrade Klocwork Insight 10.0 SR4 Document version 1.4 Klocwork Installation and Upgrade Version 10.0 PDF generated using the open source mwlib toolkit. See http://code.pediapress.com/ for more information. PDF generated at: Wed, 30 Apr 2014 20:28:47 EST Contents Articles Before you install 1 System requirements 1 Release Notes 10 About the Klocwork packages and components 23 Upgrading from a previous version 25 Upgrading from a previous version 25 Import your existing projects into a new projects root 26 Migrate your projects root directory 29 Installing the Klocwork Server package on Windows -- Upgrade only 34 Installing the Klocwork Server package on Unix -- Upgrade only 36 Installing the Klocwork Server package on Mac -- Upgrade only 38 Get a license 40 Getting a license 40 Installing the Server package 43 Installing Klocwork Insight 43 Installing the Klocwork Server package on Windows 44 Installing the Klocwork Server package on Unix 47 Installing the Klocwork Server package on Mac 50 Viewing and changing Klocwork server settings 52 Downloading and deploying the desktop analysis plug-ins 54 kwupdate 55 Installing a desktop analysis plug-in or command line utility 57 Installing a desktop analysis plug-in 57 Installing the Klocwork plug-in from the Eclipse update site 60 Running a custom installation for new or upgraded IDEs 61 Installing the Distributed Analysis package 62 Installing the Distributed Analysis package 62 Configuring and starting the Klocwork servers 65 Viewing and changing Klocwork server settings 65 -

D2.11 Report on RTOS Scheduling Revised

D2.11 Report on RTOS scheduling Revised Grant agreement no. 780785 Project acronym OFERA (micro-ROS) Project full title Open Framework for Embedded Robot Applications Deliverable number D2.11 Deliverable name Report on RTOS scheduling Date June 2020 Dissemination level public Workpackage and task WP2 - Task 2.4 Author Juan Flores Muñoz (eProsima) Contributors Francesca Finocchiaro (eProsima), Pablo Garrido Sanchez (eProsima) Keywords micro-ROS, robotics, ROS, microcontrollers, scheduling, real-time Abstract This document reviews the scheduling algorithms of- fered by the three RTOSes supported by micro-ROS and presents the scheduling architecture selected for the project. D2.11: Report on RTOS scheduling – Revised Contents 1 Summary 2 2 Acronyms and keywords 2 3 Introduction 2 4 Supported RTOS 2 4.1 NuttX ............................................. 3 4.2 FreeRTOS ........................................... 3 4.3 Zephyr ............................................ 4 5 Scheduling architecture 4 6 RTOS implementation 5 7 Conclusion and future steps. 5 1 D2.11: Report on RTOS scheduling – Revised 1 Summary This report is the sequel of the deliverable 2.10 (Report on RTOS scheduling-Initial) submitted in December 2018. Based on the previous deliverable, we will analyse the scheduling mechanisms that have been implemented within the micro-ROS project for each of the supported RTOSes, in order to achieve the required functionalities. 2 Acronyms and keywords Term Definition RTOS Real-Time Operating System OS Operating System DDS Data Distribution Service ROS Robot Operating System MCU Microcontroller unit AL Abstraction layer 3 Introduction Schedulers are software entities that manage the execution of processes using different techniques depending on the objectives. Their main task is to decide which process to execute at each time in the processing unit. -

MINITEE—A Lightweight Trustzone-Assisted TEE for Real-Time Systems

electronics Article MINITEE—A Lightweight TrustZone-Assisted TEE for Real-Time Systems Songran Liu 1,2 , Nan Guan 2, Zhishan Guo 3,* and Wang Yi 1 1 College of Computer Science and Engineering, Northeastern University, Shenyang 110819, China; [email protected] (S.L.); [email protected] (W.Y.) 2 Department of Computing, The Hong Kong Polytechnic University, Hong Kong 999077, China; [email protected] 3 Department of Electrical and Computer Engineering, University of Central Florida, Orlando, FL 32816-2362, USA * Correspondence: [email protected] Received: 31 May 2020; Accepted: 8 July 2020; Published: 11 July 2020 Abstract: While trusted execution environments (TEEs) provide industry standard security and isolation, TEE requests through secure monitor calls (SMCs) attribute to large time overhead and weakened temporal predictability. Moreover, as current available TEE solutions are designed for Linux and/or Android initially, it will encounter many constraints (e.g., driver libraries incompatible, large memory footprint, etc.) when integrating with low-end Real-Time Operating Systems, RTOSs. In this paper, we present MINITEE to understand, evaluate and discuss the benefits and limitations when integrating TrustZone-assisted TEEs with RTOSs. We demonstrate how MINITEE can be adequately exploited for meeting the real-time needs, while presenting a low performance overhead to the rich OSs (i.e., low-end RTOSs). Keywords: real-time system; ARM TrustZone; trusted execution environment 1. Introduction As real-time embedded systems become more complex and interconnected, certain sections or parts of the systems may need to be protected to prevent unauthorized access, or isolated to ensure functional/non-functional correctness.