SDCC Compiler User Guide

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Linux and Electronics

Linux and Electronics Urs Lindegger Linux and Electronics Urs Lindegger Copyright © 2019-11-25 Urs Lindegger Table of Contents 1. Introduction .......................................................................................................... 1 Note ................................................................................................................ 1 2. Printed Circuits ...................................................................................................... 2 Printed Circuit Board design ................................................................................ 2 Kicad ....................................................................................................... 2 Eagle ..................................................................................................... 13 Simulation ...................................................................................................... 13 Spice ..................................................................................................... 13 Digital simulation .................................................................................... 18 Wings 3D ....................................................................................................... 18 User interface .......................................................................................... 19 Modeling ................................................................................................ 19 Making holes in Wings 3D ....................................................................... -

Fill Your Boots: Enhanced Embedded Bootloader Exploits Via Fault Injection and Binary Analysis

IACR Transactions on Cryptographic Hardware and Embedded Systems ISSN 2569-2925, Vol. 2021, No. 1, pp. 56–81. DOI:10.46586/tches.v2021.i1.56-81 Fill your Boots: Enhanced Embedded Bootloader Exploits via Fault Injection and Binary Analysis Jan Van den Herrewegen1, David Oswald1, Flavio D. Garcia1 and Qais Temeiza2 1 School of Computer Science, University of Birmingham, UK, {jxv572,d.f.oswald,f.garcia}@cs.bham.ac.uk 2 Independent Researcher, [email protected] Abstract. The bootloader of an embedded microcontroller is responsible for guarding the device’s internal (flash) memory, enforcing read/write protection mechanisms. Fault injection techniques such as voltage or clock glitching have been proven successful in bypassing such protection for specific microcontrollers, but this often requires expensive equipment and/or exhaustive search of the fault parameters. When multiple glitches are required (e.g., when countermeasures are in place) this search becomes of exponential complexity and thus infeasible. Another challenge which makes embedded bootloaders notoriously hard to analyse is their lack of debugging capabilities. This paper proposes a grey-box approach that leverages binary analysis and advanced software exploitation techniques combined with voltage glitching to develop a powerful attack methodology against embedded bootloaders. We showcase our techniques with three real-world microcontrollers as case studies: 1) we combine static and on-chip dynamic analysis to enable a Return-Oriented Programming exploit on the bootloader of the NXP LPC microcontrollers; 2) we leverage on-chip dynamic analysis on the bootloader of the popular STM8 microcontrollers to constrain the glitch parameter search, achieving the first fully-documented multi-glitch attack on a real-world target; 3) we apply symbolic execution to precisely aim voltage glitches at target instructions based on the execution path in the bootloader of the Renesas 78K0 automotive microcontroller. -

Installation Guide

install_guide.book Page i Monday, May 11, 2015 8:48 PM Installation Guide Installation Guide Schrödinger Software Release 2015-2 Schrödinger Press install_guide.book Page ii Monday, May 11, 2015 8:48 PM Installation Guide Copyright © 2015 Schrödinger, LLC. All rights reserved. While care has been taken in the preparation of this publication, Schrödinger assumes no responsibility for errors or omissions, or for damages resulting from the use of the information contained herein. Canvas, CombiGlide, ConfGen, Epik, Glide, Impact, Jaguar, Liaison, LigPrep, Maestro, Phase, Prime, PrimeX, QikProp, QikFit, QikSim, QSite, SiteMap, Strike, and WaterMap are trademarks of Schrödinger, LLC. Schrödinger, BioLuminate, and MacroModel are registered trademarks of Schrödinger, LLC. MCPRO is a trademark of William L. Jorgensen. DESMOND is a trademark of D. E. Shaw Research, LLC. Desmond is used with the permission of D. E. Shaw Research. All rights reserved. This publication may contain the trademarks of other companies. Schrödinger software includes software and libraries provided by third parties. For details of the copyrights, and terms and conditions associated with such included third party software, use your browser to open third_party_legal.html, which is in the docs folder of your Schrödinger software installation. This publication may refer to other third party software not included in or with Schrödinger software ("such other third party software"), and provide links to third party Web sites ("linked sites"). References to such other third party software or linked sites do not constitute an endorsement by Schrödinger, LLC or its affiliates. Use of such other third party software and linked sites may be subject to third party license agreements and fees. -

Tortoisemerge a Diff/Merge Tool for Windows Version 1.11

TortoiseMerge A diff/merge tool for Windows Version 1.11 Stefan Küng Lübbe Onken Simon Large TortoiseMerge: A diff/merge tool for Windows: Version 1.11 by Stefan Küng, Lübbe Onken, and Simon Large Publication date 2018/09/22 18:28:22 (r28377) Table of Contents Preface ........................................................................................................................................ vi 1. TortoiseMerge is free! ....................................................................................................... vi 2. Acknowledgments ............................................................................................................. vi 1. Introduction .............................................................................................................................. 1 1.1. Overview ....................................................................................................................... 1 1.2. TortoiseMerge's History .................................................................................................... 1 2. Basic Concepts .......................................................................................................................... 3 2.1. Viewing and Merging Differences ...................................................................................... 3 2.2. Editing Conflicts ............................................................................................................. 3 2.3. Applying Patches ........................................................................................................... -

Zilog’S Ez80acclaim!™ Product Family, Which Offers On-Chip Flash Versions of Zilog’S Ez80® • 3.0–3.6 V Supply Voltage with 5 V Tolerant Inputs Processor Core

eZ80Acclaim!™ Flash Microcontrollers eZ80F91 Product Brief PB013502-0104 Product Block Diagram • I2C with independent clock rate generator • SPI with independent clock rate generator eZ80F91 MCU • Four Counter/Timers with prescalers supporting event counting, input capture, output compare, and 256 KB Flash + 32-Bit GPIO PWM modes 512 B Flash • Watch-Dog Timer with internal RC clocking 10/100 Mbps option 8KB SRAM Ethernet MAC • Real-time clock with on-chip 32kHz oscillator, 8KB Frame Buffer selectable 50/60Hz input, and separate RTC_VDD pin for battery backup. Infrared 2 • Glueless external memory interface with 4 Chip- Encoder/ 2 UART I C SPI Selects/Wait-State Generators and external WAIT Decoder input pin. Supports Intel and Motorola buses. Real-Time • JTAG Interface supporting emulation features 4 PRT WDT Clock • Low-power PLL and on-chip oscillator • Programmable-priority vectored interrupts, non- 4 CS JTAG ZDI PLL maskable interrupts, and interrupt controller +WSG • New DMA-like eZ80® CPU instructions • Power management features supporting HALT/ Features SLEEP modes and selective peripheral power- down controls The eZ80F91 microcontroller is a member of • 144-pin BGA or 144-pin LQFP package ZiLOG’s eZ80Acclaim!™ product family, which offers on-chip Flash versions of ZiLOG’s eZ80® • 3.0–3.6 V supply voltage with 5 V tolerant inputs processor core. The eZ80F91 offers the following • Operating Temperature Ranges: features: – Standard: 0ºC to +70ºC • 50MHz High-Performance eZ80® CPU – Extended: –40ºC to +105ºC • 256 KB Flash Program Memory plus extra 512B device configuration Flash memory General Description • 32 bits of General-Purpose I/O The eZ80F91 device is an industry first, featuring a • 16K B total on-chip high-speed SRAM: high-performance 8-bit microcontroller with an integrated 10/100 BaseT Ethernet Media Access – 8KB for general-purpose use controller (EMAC). -

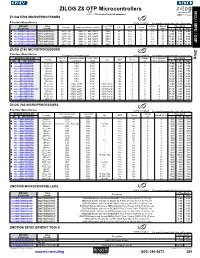

ZILOG Z8 OTP Microcontrollers MCU / MPU / DSP This Product Is Rohs Compliant

ZILOG Z8 OTP Microcontrollers DSP MPU / MCU / This product is RoHS compliant. ZILOG EZ80 MICROPROCESSORS ♦ Surface Mount Device For quantities greater than listed, call for quote. MOUSER Zilog Core CPU Voltage Speed Price Each Package Communications Controller I/O WDT Timers STOCK NO. Part No. Used (V) (MHz) 1 25 100 ♦ 692-EZ80L92AZ020EG EZ80L92AZ020EC LQFP-100 DMA, I2C, SPI, UART EZ80 24 Yes 6 3.3 20 9.29 9.10 8.63 ♦ 692-EZ80L92AZ020SG EZ80L92AZ020SC LQFP-100 DMA, I2C, SPI, UART EZ80 24 Yes 6 3.3 20 8.08 7.78 7.50 ♦ 692-EZ80L92AZ050EG EZ80L92AZ050EC LQFP-100 DMA, I2C, SPI, UART EZ80 24 Yes 6 3.3 50 10.21 9.75 9.49 ♦ 692-EZ80L92AZ050SG EZ80L92AZ050SC LQFP-100 DMA, I2C, SPI, UART EZ80 24 Yes 6 3.3 50 8.89 8.54 8.26 ♦ 692-EZ80190AZ050SG EZ80190AZ050SC LQFP-100 DMA, I2C, SPI, UART EZ80 32 Yes 6 3.3 50 12.03 11.59 11.17 ♦ 692-EZ80190AZ050EG EZ80190AZ050EC LQFP-100 DMA, I2C, SPI, UART EZ80 32 Yes 6 3.3 50 13.82 13.28 12.84 ZILOG Z180 MICROPROCESSORS Zilog ♦Surface Mount Device *See above for development tools. For quantities greater than listed, call for quote. MOUSER STOCK NO. Speed Communications Core CPU Voltage Development Price Each Package I/O WDT Timers Mfr. Mfr. Part No. (MHz) Controller Used (V) Tools Available 1 25 100 ♦ 692-Z8018006VSG PLCC-68 6 CPU Z180 - No 2 5 - 8.40 7.36 6.01 ♦ 692-Z8018006VEG PLCC-68 6 CPU Z180 - No 2 5 - 10.00 8.55 7.14 692-Z8018006PSG DIP-64 6 CPU Z180 - No 2 5 - 8.40 7.36 6.01 692-Z8018006PEG DIP-64 6 CPU Z180 - No 2 5 - 10.00 8.55 7.14 692-Z8018008PSG DIP-64 8 CPU Z180 - No 2 5 - 8.75 7.38 6.25 ♦ 692-Z8018008VSG -

Versa 8051 Mcus TB102 – Using Versa 8051 Include Files Rev 1.0

Versa 8051 MCUs TB102 – Using Versa 8051 Include Files Rev 1.0 How to Use Include Files for Versa 8051 MCUs 1 Introduction For compilers/assemblers that do not allow long file names, the naming convention is as follows: This technical bulletin addresses the include files developed for each of Ramtron’s fast and flexible AAFFDDDD.EXT Versa 8051 microcontrollers. Include files contain code AA: The initials of the compiler or assembler, such as for the MCU’s special function registers (SFRs). This ML for the MetaLink Cross Assembler. code is compatible with most popular 8051 compilers and assemblers. FF: The family of the target device: RS for the Versa 8051 family. 2 Supported Compilers DDDD: The first digit grouping of the device name, for Currently, include files exist for the following 8051 example the VRS51L2070 will use 2070. compilers and assemblers: EXT: The extension for the target programming language, such as .H for the C language, or .inc for an • MetaLink Macro Assembler assembler. • RIDE 51 (RKit) MA51 Macro Assembler • RIDE 51 (RKit) RC51 C Compiler 3.2 Location and Installation • Keil µVision3 A51 Macro Assembler All the files are placed in a zipped folder labeled with • Keil µVision3 C51 C Compiler the device name (for example, VRS51L3074.ZIP). • SDCC (Small Device C Compiler) When downloaded, the necessary file(s) can be moved • ASX8051 cross assembler to two possible locations: If you are using a different compiler, apply one of the • The compiler/assembler source directory provided files as a template or contact Ramtron for • The folder of the current project assistance. -

Tesis De Microcontroladores.Pdf

UNIVERSIDAD DE EL SALVADOR FACULTAD MULTIDISCIPLINARIA DE OCCIDENTE DEPARTAMENTO DE INGENIERÍA Y ARQUITECTURA. TRABAJO DE GRADUACIÓN DENOMINADO: “DISEÑO DE GUÍAS DE TRABAJO Y CONSTRUCCIÓN DE EQUIPO DIDÁCTICO PARA LA IMPLANTACIÓN DE PRÁCTICAS DE LABORATORIO CON MICRO CONTROLADORES EN LA CARRERA DE INGENIERÍA DE SISTEMAS INFORMÁTICOS DE LA FACULTAD MULTIDISCIPLINARIA DE OCCIDENTE.” PARA OPTAR AL GRADO DE: INGENIERO DE SISTEMA INFORMÁTICOS PRESENTAN: FRANCIA ESCOBAR, ROBERTO ANTONIO GARCÍA, JUAN CARLOS UMAÑA ORDOÑEZ, JORGE ARTURO DOCENTE DIRECTOR ING. JOSE FRANCISCO ANDALUZ NOVIEMBRE, 2007. SANTA ANA EL SALVADOR CENTRO AMÉRICA UNIVERSIDAD DE EL SALVADOR RECTOR MÁSTER RUFINO ANTONIO QUEZADA SÁNCHEZ VICERRECTOR ACADÉMICO MÁSTER MIGUEL ÁNGEL PÉREZ RAMOS VICE RECTOR ADMINISTRATIVO MÁSTER ÓSCAR NOÉ NAVARRETE SECRETARIO GENERAL LICENCIADO DOUGLAS VLADIMIR ALFARO CHÁVEZ FACULTAD MULTIDISCIPLINARIA DE OCCIDENTE DECANO LIC. JORGE MAURICIO RIVERA VICE DECANO LIC. ELADIO ZACARÍAS ORTEZ SECRETARIO LIC. VÍCTOR HUGO MERINO QUEZADA JEFE DE DEPARTAMENTO DE INGENIERÍA ING. RENÉ ERNESTO MARTÍNEZ BERMÚDEZ AGRADECIMIENTOS A DIOS TODOPODEROSO Por permitir que llegara hasta el final de la carrera, por no dejarme solo en este camino y siempre levantarme cuando necesite de su apoyo y fuerza para continuar adelante. A MI MADRE ÁNGELA VICTORIA ESCOBAR DE FRANCIA Por su apoyo, paciencia y ser un pilar en mi vida; sin la cual no hubiese podido culminar la carrera., le dedico este triunfo con las palabras con las que siempre me ha dado confianza y fuerza de seguir adelante “se triunfa cuando se persevera”. A MI PADRE JOSÉ ANTONIO FRANCIA ESCOBAR Que su ejemplo formo en mi la idea de siempre mirar más adelante, seguir luchando y creer que siempre es posible superarse cada día más; gracias por su inmenso apoyo desde todos los puntos de mi carrera y mi vida, como padre, docente, asesor y amigo. -

Operating System Components for an Embedded Linux System

INSTITUTEFORREAL-TIMECOMPUTERSYSTEMS TECHNISCHEUNIVERSITATM¨ UNCHEN¨ PROFESSOR G. F ARBER¨ Operating System Components for an Embedded Linux System Martin Hintermann Studienarbeit ii Operating System Components for an Embedded Linux System Studienarbeit Executed at the Institute for Real-Time Computer Systems Technische Universitat¨ Munchen¨ Prof. Dr.-Ing. Georg Farber¨ Advisor: Prof.Dr.rer.nat.habil. Thomas Braunl¨ Author: Martin Hintermann Kirchberg 34 82069 Hohenschaftlarn¨ Submitted in February 2007 iii Acknowledgements At first, i would like to thank my supervisor Prof. Dr. Thomas Braunl¨ for giving me the opportunity to take part at a really interesting project. Many thanks to Thomas Sommer, my project partner, for his contribution to our good work. I also want to thank also Bernard Blackham for his assistance by email and phone at any time. In my opinion, it was a great cooperation of all persons taking part in this project. Abstract Embedded systems can be found in more and more devices. Linux as a free operating system is also becoming more and more important in embedded applications. Linux even replaces other operating systems in certain areas (e.g. mobile phones). This thesis deals with the employment of Linux in embedded systems. Various architectures of embedded systems are introduced and the characteristics of common operating systems for these devices are reviewed. The architecture of Linux is examined by looking at the particular components such as kernel, standard C libraries and POSIX tools for embedded systems. Furthermore, there is a survey of real-time extensions for the Linux kernel. The thesis also treats software development for embedded Linux ranging from the prerequi- sites for compiling software to the debugging of binaries. -

Getting the Most out of Your Professional RISC-V Compiler and Debugger

Getting the most out of your professional RISC-V compiler and debugger Ryan Sheng / 盛磊, [email protected], 021-63758658 IAR Systems (China) 2019.11.13 Highlight . Meet the demand of quality & time-to-market for your RISC-V project . Easy code reuse and widest customers base from IAR Embedded Workbench, the complete IDE toolchain . Fit the needs of both memory size and necessary performance by the outstanding C/C++ compiler . Improve the code quality and find potential issues earlier by the integrated C-STAT analysis . Identify low level bugs and provide graphical visibility to all SoC resource by the powerful debugger IAR Embedded Workbench Complete C/C++ compiler and debugger toolchain Most widely used development tools for embedded applications User-friendly IDE features and broad ecosystem integration Industry leading code optimization technology Comprehensive debugger Integrated code analysis tools ISO/ANSI C/C++ compliance with C18 and C++17 Support for 12,000+ devices Different architecture, One solution All available 8-,16- and 32-bit MCUs Cortex-M0 Cortex-R8 AVR H8 Cortex-M0+ Cortex-A5 AVR32 STM8 Cortex-M1 Cortex-A7 RX ColdFire Cortex-M3 Cortex-A8 RL78 HCS12 Cortex-M4 Cortex-A9 RH850 S08 Cortex-M7 Cortex-A15 78K MAXQ Cortex-M23 ARM11 SuperH CR16C Cortex-M33 ARM9 V850 SAM8 Cortex-R4 ARM7 R32C RISC-V Cortex-R5 SecurCore M32C Cortex-R52 8051 M16C Cortex-R7 MSP430 R8C Compiler optimizations x = y - 15; Function C Source inlining Dead code elimination Parser Compiler Loop = unrolling Intermediate Code High-Level Optimizer x – Scheduling y 15 Code Generator Low-Level Peephole Target Code Optimizer c.mv a3, sp Crosscall c.li a1, 1 Assembler lui a0, 0x80002 Link time optimizations 01001000111001101001 Object Code Linker Controlling optimizations Multi-file compilation allows Language standards the optimizer to operate on . -

Anatomy of Cross-Compilation Toolchains

Embedded Linux Conference Europe 2016 Anatomy of cross-compilation toolchains Thomas Petazzoni free electrons [email protected] Artwork and Photography by Jason Freeny free electrons - Embedded Linux, kernel, drivers - Development, consulting, training and support. http://free-electrons.com 1/1 Thomas Petazzoni I CTO and Embedded Linux engineer at Free Electrons I Embedded Linux specialists. I Development, consulting and training. I http://free-electrons.com I Contributions I Kernel support for the Marvell Armada ARM SoCs from Marvell I Major contributor to Buildroot, an open-source, simple and fast embedded Linux build system I Living in Toulouse, south west of France Drawing from Frank Tizzoni, at Kernel Recipes 2016 free electrons - Embedded Linux, kernel, drivers - Development, consulting, training and support. http://free-electrons.com 2/1 Disclaimer I I am not a toolchain developer. Not pretending to know everything about toolchains. I Experience gained from building simple toolchains in the context of Buildroot I Purpose of the talk is to give an introduction, not in-depth information. I Focused on simple gcc-based toolchains, and for a number of examples, on ARM specific details. I Will not cover advanced use cases, such as LTO, GRAPHITE optimizations, etc. I Will not cover LLVM free electrons - Embedded Linux, kernel, drivers - Development, consulting, training and support. http://free-electrons.com 3/1 What is a cross-compiling toolchain? I A set of tools that allows to build source code into binary code for -

MEK6800D2 Manual 2Ed 1977.Pdf

MOTOROLA Semiconductor Products Inc. MEK6800D2 MANUAL Circuit diagrams external to Motorola products are included as a means of illustrating typical Microprocessor applications; consequently, complete information sufficient for construction purposes is not necessarily given. The information in this manual has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. Furthermore, such information does not convey to the purchaser of the semiconductor devices described any license under the patent rights of Motorola Inc. or others. Motorola reserves the right to change specifications without notice. EXORciser, JBUG and MINlbug are trademarks of Motorola Inc. Second Edition © MOTOROLA INC., 1977 First Edition © 1976 "All Rights Reserved" Printed in U.S.A. TABLE OF CONTENTS CHAPTER 1: Introduction 1-1 General Description and Capability . 1-1 1-2 Preparation for Use . 1-4 1-2.1 Construction Hints ..................................................... 1-5 1-3 Start-up Procedure . 1-6 1-4 Operating Procedures . 1-6 1-4.1 Memory Examine and Change ............................................ 1-7 1-4.2 Escape (Abort) ........................................................ 1-7 1-4.3 Register Display ....................................................... 1-7 1-4.4 Go to User Program .................................................... 1-9 1-4.5 Punch from Memory to Tape ............................................. 1-9 1-4.6 Load from Tape to Memory .............................................