Multi-Frequency Modulation and Control for DC/AC and AC/DC Resonant Converters

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Bias Circuits for RF Devices

Bias Circuits for RF Devices Iulian Rosu, YO3DAC / VA3IUL, http://www.qsl.net/va3iul A lot of RF schematics mention: “bias circuit not shown”; when actually one of the most critical yet often overlooked aspects in any RF circuit design is the bias network. The bias network determines the amplifier performance over temperature as well as RF drive. The DC bias condition of the RF transistors is usually established independently of the RF design. Power efficiency, stability, noise, thermal runway, and ease to use are the main concerns when selecting a bias configuration. A transistor amplifier must possess a DC biasing circuit for a couple of reasons. • We would require two separate voltage supplies to furnish the desired class of bias for both the emitter-collector and the emitter-base voltages. • This is in fact still done in certain applications, but biasing was invented so that these separate voltages could be obtained from but a single supply. • Transistors are remarkably temperature sensitive, inviting a condition called thermal runaway. Thermal runaway will rapidly destroy a bipolar transistor, as collector current quickly and uncontrollably increases to damaging levels as the temperature rises, unless the amplifier is temperature stabilized to nullify this effect. Amplifier Bias Classes of Operation Special classes of amplifier bias levels are utilized to achieve different objectives, each with its own distinct advantages and disadvantages. The most prevalent classes of bias operation are Class A, AB, B, and C. All of these classes use circuit components to bias the transistor at a different DC operating current, or “ICQ”. When a BJT does not have an A.C. -

Adapting Techniques to Improve Efficiency in Radio Frequency

electronics Article Adapting Techniques to Improve Efficiency in Radio Frequency Power Amplifiers for Visible Light Communications Daniel G. Aller 1,* , Diego G. Lamar 1, Juan Rodriguez 2, Pablo F. Miaja 1 , Valentin Francisco Romero 3, Jose Mendiolagoitia 3 and Javier Sebastian 1 1 Power Supplies Group—Electrical Engineering Department of the University of Oviedo, 33204 Gijon, Spain; [email protected] (D.G.L.); [email protected] (P.F.M.); [email protected] (J.S.) 2 Center for Industrial Electronics—Polytechnic University of Madrid, 28006 Madrid, Spain; [email protected] 3 Thyssenkrupp Elevator Innovation Center S A U—Thyssenkrupp AG, 33203 Gijon, Spain; [email protected] (V.F.R.); [email protected] (J.M.) * Correspondence: [email protected]; Tel.: +34-985-182-578 Received: 30 November 2019; Accepted: 3 January 2020; Published: 10 January 2020 Abstract: It is well known that modern wireless communications systems need linear, wide bandwidth, efficient Radio Frequency Power Amplifiers (RFPAs). However, conventional configurations of RFPAs based on Class A, Class B, and Class AB exhibit extremely low efficiencies when they manage signals with a high Peak-to-Average Power Ratio (PAPR). Traditionally, a number of techniques have been proposed either to achieve linearity in the case of efficient Switching-Mode RFPAs or to improve the efficiency of linear RFPAs. There are two categories in the application of aforementioned techniques. First, techniques based on the use of Switching-Mode DC–DC converters with a very-fast-output response (faster than 1 µs). Second, techniques based on the interaction of several RFPAs. The current expansion of these techniques is mainly due to their application in cellphone networks, but they can also be applied in other promising wireless communications systems such as Visible Light Communication (VLC). -

AN-937 Designing Amplifier Circuits

AN-937 APPLICATION NOTE One Technology Way • P. O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com Designing Amplifier Circuits: How to Avoid Common Problems by Charles Kitchin INTRODUCTION down toward the negative supply. The bias voltage is amplified When compared to assemblies of discrete semiconductors, by the closed-loop dc gain of the amplifier. modern operational amplifiers (op amps) and instrumenta- This process can be lengthy. For example, an amplifier with a tion amplifiers (in-amps) provide great benefits to designers. field effect transistor (FET) input, having a 1 pA bias current, Although there are many published articles on circuit coupled via a 0.1-μF capacitor, has an IC charging rate, I/C, of applications, all too often, in the haste to assemble a circuit, 10–12/10–7 = 10 μV per sec basic issues are overlooked leading to a circuit that does not function as expected. This application note discusses the most or 600 μV per minute. If the gain is 100, the output drifts at common design problems and offers practical solutions. 0.06 V per minute. Therefore, a casual lab test, using an ac- coupled scope, may not detect this problem, and the circuit MISSING DC BIAS CURRENT RETURN PATH may not fail until hours later. It is important to avoid this One of the most common application problems encountered is problem altogether. the failure to provide a dc return path for bias current in ac- +VS coupled op amp or in-amp circuits. -

Chapter 1: Modulation Systems

SYLLABUS: 141304 – ANALOG AND DIGITAL COMMUNICATION L T P C 3 1 0 4 UNIT I FUNDAMENTALS OF ANALOG COMMUNICATION 9 Principles of Amplitude Modulation – AM Envelope – Frequency Spectrum and Bandwidth – Modulation Index and Percent Modulation – AM Voltage Distribution – AM Power Distribution – Angle Modulation – FM and PM Waveforms – Phase Deviation and Modulation Index – Frequency Deviation and Percent Modulation – Frequency Analysis of Angle Modulated Waves – Bandwidth Requirements for Angle Modulated Waves. UNIT II DIGITAL COMMUNICATION 9 Basics – Shannon Limit for Information Capacity – Digital Amplitude Modulation – Frequency Shift Keying – FSK Bit Rate and Baud – FSK Transmitter – BW Consideration of FSK – FSK Receiver – Phase Shift Keying – Binary Phase Shift Keying – QPSK – Quadrature Amplitude Modulation – Bandwidth Efficiency – Carrier Recovery – Squaring Loop – Costas Loop – DPSK. UNIT III DIGITAL TRANSMISSION 9 Basics – Pulse Modulation – PCM – PCM Sampling – Sampling Rate – Signal to Quantization Noise Rate – Companding – Analog and Digital – Percentage Error – Delta Modulation – Adaptive Delta Modulation – Differential Pulse Code Modulation – Pulse Transmission – Intersymbol Interference – Eye Patterns. UNIT IV DATA COMMUNICATIONS 9 Basics – History of Data Communications – Standards Organizations for Data Communication – Data Communication Circuits – Data Communication Codes – Error Control – Error Detection – Error Correction – Data Communication Hardware – Serial and Parallel Interfaces – Data Modems – Asynchronous Modem – Synchronous Modem – Low-Speed Modem – Medium and High Speed Modem – Modem Control. UNIT V SPREAD SPECTRUM AND MULTIPLE ACCESS TECHNIQUES 9 Basics – Pseudo-Noise Sequence – DS Spread Spectrum with Coherent Binary PSK – Processing Gain – FH Spread Spectrum – Multiple Access Techniques – Wireless Communication – TDMA and CDMA in Wireless Communication Systems – Source Coding of Speech for Wireless Communications. L: 45 T: 15 Total: 60 TEXT BOOKS 1. -

Section 9: DSP Applications

DSP APPLICATIONS SECTION 9 DSP APPLICATIONS I High Performance Modems for Plain Old Telephone Service (POTS) I Remote Access Server (RAS) Modems I ADSL (Assymetric Digital Subscriber Line) I Digital Cellular Telephones I GSM Handset Using SoftFone™ Baseband Processor and Othello™ Radio I Analog Cellular Basestations I Digital Cellular Basestations I Motor Control I Codecs and DSPs in Voiceband and Audio Applications I A Sigma-Delta ADC with Programmable Digital Filter 9.a DSP APPLICATIONS 9.b DSP APPLICATIONS SECTION 9 DSP APPLICATIONS Walt Kester HIGH PERFORMANCE MODEMS FOR PLAIN OLD TELEPHONE SERVICE (POTS) Modems (Modulator/Demodulator) are widely used to transmit and receive digital data using analog modulation over the Plain Old Telephone Service (POTS) network as well as private lines. Although the data to be transmitted is digital, the telephone channel is designed to carry voice signals having a bandwidth of approximately 300 to 3300Hz. The telephone transmission channel suffers from delay distortion, noise, crosstalk, impedance mismatches, near-end and far-end echoes, and other imperfections. While certain levels of these signal degradations are perfectly acceptable for voice communication, they can cause high error rates in digital data transmission. The fundamental purpose of the transmitter portion of the modem is to prepare the digital data for transmission over the analog voice line. The purpose of the receiver portion of the modem is to receive the signal which contains the analog representation of the data , and reconstruct the original digital data at an acceptable error rate. High performance modems make use of digital techniques to perform such functions as modulation, demodulation, error detection and correction, equalization, and echo cancellation. -

Visvesvarayatechnologic

P a g e | 1 VISVESVARAYA TECHNOLOGICAL UNIVERSITY Belgaum, Karnataka-590014 A Project Report On “IMPLEMENTATION OF SPACE VECTOR PULSE WIDTH MODULATION FOR INVERTERS USING MATLAB AND SIMULINK” Submitted in partial fulfilment for the award of degree of Bachelor of Engineering In Electronics and Communication Engineering 2018-2019 Submitted by AKHIL CHOWDARY M 1NH15EC005 BUJJA AJAY 1NH15EC012 T S HIMAKEERTHI 1NH15EC121 Under the Guidance of Dr. K C R NISHA Professor Department of Electronics and Communication Engineering, NHCE P a g e | 2 DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING CERTIFICATE Certified that the project work “IMPLEMENTATION OF SPACE VECTOR PULSE WIDTH MODULATION FOR INVERTERS USING MATLAB AND SIMULINK” carried out by the following Bonafide students of New Horizon College of Engineering in partial fulfilment for the award of Bachelor of Engineering In Electronics and Communication branch , of Visvesvaraya TechnologicalUniversity , Belgaum during the academic year 2018-2019. It is certified that all corrections /suggestions indicated for internal assessment have been approved as it satisfies the academic requirements with respect of project work prescribed for said degree. 1. AKHIL CHOWDARY M 1NH15EC005 2. BUJJA AJAY 1NH15EC012 3. T.S. HIMAKEERTHI 1NH15EC121 Internal Guide HOD Principal Dr. K C R NISHA Dr. SANJEEV SHARMA Dr. MANJUNATHA External Viva Name of the Examiners: Signature with date: 1. 2. P a g e | 3 ACKNOWLEDGEMENT The satisfaction that accompanies the successful completion of task would be incomplete without mention of the people who made it possible, whose constant guidance and encouragement crown all efforts with success. We express my sincere gratitude to Dr. Sanjeev Sharma, Head of Department of Electronics and Communication Engineering, New Horizon College of Engineering, for providing guidance and encouragement. -

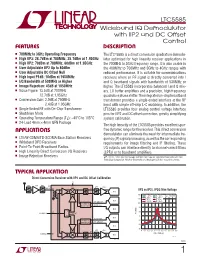

Wideband IQ Demodulator with IIP2 and DC Offset Control

LTC5585 Wideband IQ Demodulator with IIP2 and DC Offset Control FEATURES DESCRIPTION n 700MHz to 3GHz Operating Frequency The LTC®5585 is a direct conversion quadrature demodu- n High IIP3: 28.7dBm at 700MHz, 25.7dBm at 1.95GHz lator optimized for high linearity receiver applications in n High IIP2: 70dBm at 700MHz, 60dBm at 1.95GHz the 700MHz to 3GHz frequency range. It is also usable in n User Adjustable IIP2 Up to 80dBm the 400MHz to 700MHz and 3GHz to 4GHz ranges with n User Adjustable DC Offset Null reduced performance. It is suitable for communications n High Input P1dB: 16dBm at 1950MHz receivers where an RF signal is directly converted into I n I/Q Bandwidth of 530MHz or Higher and Q baseband signals with bandwidth of 530MHz or n Image Rejection: 43dB at 1950MHz higher. The LTC5585 incorporates balanced I and Q mix- n Noise Figure: 13.5dB at 700MHz ers, LO buffer amplifiers and a precision, high frequency 12.7dB at 1.95GHz quadrature phase shifter. The integrated on-chip broadband n Conversion Gain: 2.0dB at 700MHz transformer provides a single-ended interface at the RF 2.4dB at 1.95GHz input with simple off-chip L-C matching. In addition, the n Single-Ended RF with On-Chip Transformer LTC5585 provides four analog control voltage interface n Shutdown Mode pins for IIP2 and DC offset correction, greatly simplifying n Operating Temperature Range (TC): –40°C to 105°C system calibration. n 24-Lead 4mm × 4mm QFN Package The high linearity of the LTC5585 provides excellent spur- APPLICATIONS free dynamic range for the receiver. -

Dynamic Power Supply Design for High-Efficiency Wireless Transmitters

Dynamic Power Supply Design for High-Efficiency Wireless Transmitters Jason T. Stauth Seth R. Sanders Electrical Engineering and Computer Sciences University of California at Berkeley Technical Report No. UCB/EECS-2006-72 http://www.eecs.berkeley.edu/Pubs/TechRpts/2006/EECS-2006-72.html May 19, 2006 Copyright © 2006, by the author(s). All rights reserved. Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission. Dynamic Power Supply Design for High-Efficiency Wireless Transmitters by Jason T. Stauth Masters Research Project Submitted to the Department of Electrical Engineering and Computer Sciences, University of California at Berkeley, in partial satisfaction of the requirements for the degree of Master of Science, Plan II. Approval for the Report and Comprehensive Examination: Committee: Professor Seth R. Sanders Research Advisor (Date) * * * * * * * Professor Ali M. Niknejad Second Reader (Date) Table of Contents Chapter 1 Introduction..................................................................................................... 6 1.1.1 Overview..................................................................................................... 7 1.1.2 Previous Work ........................................................................................... -

Time-Frequency Analysis of DC Bias Vibration of Transformer Core on The

INGENIERÍA E INVESTIGACIÓN VOL. 36 N.° 1, APRIL - 2016 (90-97) DOI: http://dx.doi.org/10.15446/ing.investig.v36n1.51580 Time-frequency analysis of DC bias vibration of transformer core on the basis of Hilbert–Huang transform Análisis de tiempo y frecuencia de vibración de polarización DC del núcleo del transformador sobre la base de Hilbert-Transform Huang X.M. Liu1, Y.M. Yang2, F. Yang3, and Q.Y. Shi4 ABSTRACT This paper presents a time–frequency analysis of the vibration of transformer under direct current (DC) bias through Hilbert–Huang transform (HHT). First, the theory of DC bias for the transformer was analyzed. Next, the empirical mode decomposition (EMD) process, which is the key in HHT, was introduced. The results of EMD, namely, intrinsic mode functions (IMFs), were calculated and summed by Hilbert transform(HT) to obtain time-dependent series in a 2D time–frequency domain. Lastly, a test system of vibration measurement for the transformer was set up. Three direction (x, y, and z axes) components of core vibration were measured. Decomposition of EMD and HHT spectra showed that vibration strength increased, and odd harmonics were produced with DC bias. Results indicated that HHT is a viable signal processing tool for transformer health monitoring. Keywords: DC bias, transformer, vibration, HHT. RESUMEN En este trabajo se presenta un análisis tiempo-frecuencia de la vibración del transformador bajo polarización de corriente continua (CC) a través de transformación Hilbert-Huang (HHT). En primer lugar, se analizó la teoría de la DC de polarización para el transformador. A continuación, el proceso de descomposición de modo empírico (EMD), que es la clave en HHT, se introdujo. -

The Effect of DC Current on Power Transformers

University of Southern Queensland Faculty of Engineering and Surveying The Effect of DC Current on Power Transformers A dissertation submitted by Ashley Karl Zeimer in fulfilment of the requirements of Courses ENG4111 and 4112 Research Project towards the degree of Bachelor of Electrical/Electronic Engineering Submitted: October, 2000 Abstract Power transformers are an integral part of almost all electrical transmission and distribution networks. Their reliable service is of the utmost importance in modern society which is dependent on a constant electricity supply. There are a range of factors that can hinder the operation of a power transformer. This dissertation presents the results of investigations into one of these factors through an analysis of the effect that direct current has on the operational characteristics of a power transformer. There are a host of adverse effects that can accompany the presence of a direct current in a transformer’s windings. The predominant effect that is witnessed is half cycle saturation. This leads to increased harmonic distortion, increased reactive power losses, overheating and elevated acoustic noise emissions. Direct current can be found in a transformer’s windings as a result of imperfections in connected equipment and also due to magnetic disturbances of the earth’s field. Tests conducted indicate that personal computers are a potentially significant source of DC when a large number of units are connected to a common point of coupling. Similarly the possibility exists for AC and DC induction motor drives to contribute sizeable quantities of DC Bias. Page i University of Southern Queensland Faculty of Engineering and Surveying ENG4111 & ENG4112 Research Project Limitations of Use The Council of the University of Southern Queensland, its Faculty of Engineering and Surveying, and the staff of the University of Southern Queensland, do not accept any responsibility for the truth, accuracy or completeness of material contained within or associated with this dissertation. -

Capacitive Coupling Ethernet Transceivers Without Using Transformers

ANLAN120 Capacitive Coupling Ethernet Transceivers without Using Transformers Introduction It is a common practice to capacitive couple Ethernet transceivers (PHYs) together without the use of a transformer to reduce both the BOM cost and PCB area. This application note describes methods for capacitive coupling of Micrel’s 10/100 Ethernet devices. External Termination Ethernet Devices The Ethernet devices in Table 1 require external termination resistors. They require external biasing or internal biasing. Table 1. Micrel Devices with External Termination External Biasing and External Termination Ethernet Device KSZ8695 Family CENTAUR – SoC KSZ8721 Family Single Port 10/100 PHY KSZ8001 Family Single Port 10/100 PHY KSZ8041 Family Single Port 10/100 PHY KSZ8841 Family Single Port 10/100 MAC Controller KSZ8842 Family 2-Port 10/100 Switch KSZ8893 Family 3-Port 10/100 Switch KSZ8873 Family 3-Port 10/100 Switch KSZ8863 Family 3-Port 10/100 Switch KSZ8851 Family Single Port 10/100 MAC Controller KSZ8995 Family 5-Port 10/100 Switch KSZ8997 8-Port 10/100 Unmanaged Switch KSZ8999 9-Port 10/100 Unmanaged Switch Internal Biasing and external termination Ethernet Device KSZ8993 family 3-Port 10/100 Switch Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000 • http://www.micrel.com November 21, 2014 Revision 3.0 Micrel, Inc. ANLAN120 − Capacitive Coupling Ethernet Transceivers without Using Transformers Methods for Capacitive Coupling The method for capacitive coupling depends upon whether or not the receiver circuit provides an internal DC bias offset. Transmit Termination Figure 1 and Figure 2 show the capacitive coupling for transmit-side termination. -

MATLAB/Simulink Implementation and Analysis of Three Pulse-Width

MATLAB/SIMULINK IMPLEMENTATION AND ANALYSIS OF THREE PULSE-WIDTH-MODULATION (PWM) TECHNIQUES by Phuong Hue Tran A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering Boise State University May 2012 c 2012 Phuong Hue Tran ALL RIGHTS RESERVED BOISE STATE UNIVERSITY GRADUATE COLLEGE DEFENSE COMMITTEE AND FINAL READING APPROVALS of the thesis submitted by Phuong Hue Tran Thesis Title: MATLAB/Simulink Implementation and Analysis of Three Pulse- Width-Modulation (PWM) Techniques Date of Final Oral Examination: 11 May 2012 The following individuals read and discussed the thesis submitted by student Phuong Hue Tran, and they evaluated her presentation and response to questions during the final oral examination. They found that the student passed the final oral examination. Said Ahmed-Zaid, Ph.D. Chair, Supervisory Committee Elisa Barney Smith, Ph.D. Member, Supervisory Committee John Chiasson, Ph.D. Member, Supervisory Committee The final reading approval of the thesis was granted by Said Ahmed-Zaid, Ph.D., Chair of the Supervisory Committee. The thesis was approved for the Graduate College by John R. Pelton, Ph.D., Dean of the Graduate College. ACKNOWLEDGMENTS I would like to take this opportunity to express my sincere appreciation to all the people who were helpful in making this thesis successful. First of all, I would like to express my gratitude to my advisor, Dr. Said Ahmed-Zaid for his valuable comments, guidance, and discussions that guided me well in the process of my thesis. I am thankful to my committee members ( Dr. John Chiasson and Dr.