Design of Analog Baseband Circuits for Wireless Communication Receivers

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

3 Characterization of Communication Signals and Systems

63 3 Characterization of Communication Signals and Systems 3.1 Representation of Bandpass Signals and Systems Narrowband communication signals are often transmitted using some type of carrier modulation. The resulting transmit signal s(t) has passband character, i.e., the bandwidth B of its spectrum S(f) = s(t) is much smaller F{ } than the carrier frequency fc. S(f) B f f f − c c We are interested in a representation for s(t) that is independent of the carrier frequency fc. This will lead us to the so–called equiv- alent (complex) baseband representation of signals and systems. Schober: Signal Detection and Estimation 64 3.1.1 Equivalent Complex Baseband Representation of Band- pass Signals Given: Real–valued bandpass signal s(t) with spectrum S(f) = s(t) F{ } Analytic Signal s+(t) In our quest to find the equivalent baseband representation of s(t), we first suppress all negative frequencies in S(f), since S(f) = S( f) is valid. − The spectrum S+(f) of the resulting so–called analytic signal s+(t) is defined as S (f) = s (t) =2 u(f)S(f), + F{ + } where u(f) is the unit step function 0, f < 0 u(f) = 1/2, f =0 . 1, f > 0 u(f) 1 1/2 f Schober: Signal Detection and Estimation 65 The analytic signal can be expressed as 1 s+(t) = − S+(f) F 1{ } = − 2 u(f)S(f) F 1{ } 1 = − 2 u(f) − S(f) F { } ∗ F { } 1 The inverse Fourier transform of − 2 u(f) is given by F { } 1 j − 2 u(f) = δ(t) + . -

Linear Filtering of Random Processes

Linear Filtering of Random Processes Lecture 13 Spring 2002 Wide-Sense Stationary A stochastic process X(t) is wss if its mean is constant E[X(t)] = µ and its autocorrelation depends only on τ = t1 − t2 ∗ Rxx(t1,t2)=E[X(t1)X (t2)] ∗ E[X(t + τ)X (t)] = Rxx(τ) ∗ Note that Rxx(−τ)=Rxx(τ)and Rxx(0) = E[|X(t)|2] Lecture 13 1 Example We found that the random telegraph signal has the autocorrelation function −c|τ| Rxx(τ)=e We can use the autocorrelation function to find the second moment of linear combinations such as Y (t)=aX(t)+bX(t − t0). 2 2 Ryy(0) = E[Y (t)] = E[(aX(t)+bX(t − t0)) ] 2 2 2 2 = a E[X (t)] + 2abE[X(t)X(t − t0)] + b E[X (t − t0)] 2 2 = a Rxx(0) + 2abRxx(t0)+b Rxx(0) 2 2 =(a + b )Rxx(0) + 2abRxx(t0) −ct =(a2 + b2)Rxx(0) + 2abe 0 Lecture 13 2 Example (continued) We can also compute the autocorrelation Ryy(τ)forτ =0. ∗ Ryy(τ)=E[Y (t + τ)Y (t)] = E[(aX(t + τ)+bX(t + τ − t0))(aX(t)+bX(t − t0))] 2 = a E[X(t + τ)X(t)] + abE[X(t + τ)X(t − t0)] 2 + abE[X(t + τ − t0)X(t)] + b E[X(t + τ − t0)X(t − t0)] 2 2 = a Rxx(τ)+abRxx(τ + t0)+abRxx(τ − t0)+b Rxx(τ) 2 2 =(a + b )Rxx(τ)+abRxx(τ + t0)+abRxx(τ − t0) Lecture 13 3 Linear Filtering of Random Processes The above example combines weighted values of X(t)andX(t − t0) to form Y (t). -

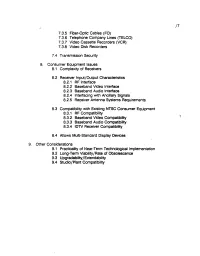

7.3.7 Video Cassette Recorders (VCR) 7.3.8 Video Disk Recorders

/7 7.3.5 Fiber-Optic Cables (FO) 7.3.6 Telephone Company Unes (TELCO) 7.3.7 Video Cassette Recorders (VCR) 7.3.8 Video Disk Recorders 7.4 Transmission Security 8. Consumer Equipment Issues 8.1 Complexity of Receivers 8.2 Receiver Input/Output Characteristics 8.2.1 RF Interface 8.2.2 Baseband Video Interface 8.2.3 Baseband Audio Interface 8.2.4 Interfacing with Ancillary Signals 8.2.5 Receiver Antenna Systems Requirements 8.3 Compatibility with Existing NTSC Consumer Equipment 8.3.1 RF Compatibility 8.3.2 Baseband Video Compatibility 8.3.3 Baseband Audio Compatibility 8.3.4 IDTV Receiver Compatibility 8.4 Allows Multi-Standard Display Devices 9. Other Considerations 9.1 Practicality of Near-Term Technological Implementation 9.2 Long-Term Viability/Rate of Obsolescence 9.3 Upgradability/Extendability 9.4 Studio/Plant Compatibility Section B: EXPLANATORY NOTES OF ATTRIBUTES/SYSTEMS MATRIX Items on the Attributes/System Matrix for which no explanatory note is provided were deemed to be self-explanatory. I. General Description (Proponent) section I shall be used by a system proponent to define the features of the system being proposed. The features shall be defined and organized under the headings ot the following subsections 1 through 4. section I. General Description (Proponent) shall consist of a description of the proponent system in narrative form, which covers all of the features and characteris tics of the system which the proponent wishe. to be included in the public record, and which will be used by various groups to analyze and understand the system proposed, and to compare with other propo.ed systems. -

Bias Circuits for RF Devices

Bias Circuits for RF Devices Iulian Rosu, YO3DAC / VA3IUL, http://www.qsl.net/va3iul A lot of RF schematics mention: “bias circuit not shown”; when actually one of the most critical yet often overlooked aspects in any RF circuit design is the bias network. The bias network determines the amplifier performance over temperature as well as RF drive. The DC bias condition of the RF transistors is usually established independently of the RF design. Power efficiency, stability, noise, thermal runway, and ease to use are the main concerns when selecting a bias configuration. A transistor amplifier must possess a DC biasing circuit for a couple of reasons. • We would require two separate voltage supplies to furnish the desired class of bias for both the emitter-collector and the emitter-base voltages. • This is in fact still done in certain applications, but biasing was invented so that these separate voltages could be obtained from but a single supply. • Transistors are remarkably temperature sensitive, inviting a condition called thermal runaway. Thermal runaway will rapidly destroy a bipolar transistor, as collector current quickly and uncontrollably increases to damaging levels as the temperature rises, unless the amplifier is temperature stabilized to nullify this effect. Amplifier Bias Classes of Operation Special classes of amplifier bias levels are utilized to achieve different objectives, each with its own distinct advantages and disadvantages. The most prevalent classes of bias operation are Class A, AB, B, and C. All of these classes use circuit components to bias the transistor at a different DC operating current, or “ICQ”. When a BJT does not have an A.C. -

Baseband Harmonic Distortions in Single Sideband Transmitter and Receiver System

Baseband Harmonic Distortions in Single Sideband Transmitter and Receiver System Kang Hsia Abstract: Telecommunications industry has widely adopted single sideband (SSB or complex quadrature) transmitter and receiver system, and one popular implementation for SSB system is to achieve image rejection through quadrature component image cancellation. Typically, during the SSB system characterization, the baseband fundamental tone and also the harmonic distortion products are important parameters besides image and LO feedthrough leakage. To ensure accurate characterization, the actual frequency locations of the harmonic distortion products are critical. While system designers may be tempted to assume that the harmonic distortion products are simply up-converted in the same fashion as the baseband fundamental frequency component, the actual distortion products may have surprising results and show up on the different side of spectrum. This paper discusses the theory of SSB system and the actual location of the baseband harmonic distortion products. Introduction Communications engineers have utilized SSB transmitter and receiver system because it offers better bandwidth utilization than double sideband (DSB) transmitter system. The primary cause of bandwidth overhead for the double sideband system is due to the image component during the mixing process. Given data transmission bandwidth of B, the former requires minimum bandwidth of B whereas the latter requires minimum bandwidth of 2B. While the filtering of the image component is one type of SSB implementation, another type of SSB system is to create a quadrature component of the signal and ideally cancels out the image through phase cancellation. M(t) M(t) COS(2πFct) Baseband Message Signal (BB) Modulated Signal (RF) COS(2πFct) Local Oscillator (LO) Signal Figure 1. -

Baseband Video Testing with Digital Phosphor Oscilloscopes

Application Note Baseband Video Testing With Digital Phosphor Oscilloscopes Video signals are complex pose instrument that can pro- This application note demon- waveforms comprised of sig- vide accurate information – strates the use of a Tektronix nals representing a picture as quickly and easily. Finally, to TDS 700D-series Digital well as the timing informa- display all of the video wave- Phosphor Oscilloscope to tion needed to display the form details, a fast acquisi- make a variety of common picture. To capture and mea- tion technology teamed with baseband video measure- sure these complex signals, an intensity-graded display ments and examines some of you need powerful instru- give the confidence and the critical measurement ments tailored for this appli- insight needed to detect and issues. cation. But, because of the diagnose problems with the variety of video standards, signal. you also need a general-pur- Copyright © 1998 Tektronix, Inc. All rights reserved. Video Basics Video signals come from a for SMPTE systems, etc. The active portion of the video number of sources, including three derived component sig- signal. Finally, the synchro- cameras, scanners, and nals can then be distributed nization information is graphics terminals. Typically, for processing. added. Although complex, the baseband video signal Processing this composite signal is a sin- begins as three component gle signal that can be carried analog or digital signals rep- In the processing stage, video on a single coaxial cable. resenting the three primary component signals may be combined to form a single Component Video Signals. color elements – the Red, Component signals have an Green, and Blue (RGB) com- composite video signal (as in NTSC or PAL systems), advantage of simplicity in ponent signals. -

Digital Baseband Modulation Outline • Later Baseband & Bandpass Waveforms Baseband & Bandpass Waveforms, Modulation

Digital Baseband Modulation Outline • Later Baseband & Bandpass Waveforms Baseband & Bandpass Waveforms, Modulation A Communication System Dig. Baseband Modulators (Line Coders) • Sequence of bits are modulated into waveforms before transmission • à Digital transmission system consists of: • The modulator is based on: • The symbol mapper takes bits and converts them into symbols an) – this is done based on a given table • Pulse Shaping Filter generates the Gaussian pulse or waveform ready to be transmitted (Baseband signal) Waveform; Sampled at T Pulse Amplitude Modulation (PAM) Example: Binary PAM Example: Quaternary PAN PAM Randomness • Since the amplitude level is uniquely determined by k bits of random data it represents, the pulse amplitude during the nth symbol interval (an) is a discrete random variable • s(t) is a random process because pulse amplitudes {an} are discrete random variables assuming values from the set AM • The bit period Tb is the time required to send a single data bit • Rb = 1/ Tb is the equivalent bit rate of the system PAM T= Symbol period D= Symbol or pulse rate Example • Amplitude pulse modulation • If binary signaling & pulse rate is 9600 find bit rate • If quaternary signaling & pulse rate is 9600 find bit rate Example • Amplitude pulse modulation • If binary signaling & pulse rate is 9600 find bit rate M=2à k=1à bite rate Rb=1/Tb=k.D = 9600 • If quaternary signaling & pulse rate is 9600 find bit rate M=2à k=1à bite rate Rb=1/Tb=k.D = 9600 Binary Line Coding Techniques • Line coding - Mapping of binary information sequence into the digital signal that enters the baseband channel • Symbol mapping – Unipolar - Binary 1 is represented by +A volts pulse and binary 0 by no pulse during a bit period – Polar - Binary 1 is represented by +A volts pulse and binary 0 by –A volts pulse. -

MT-033: Voltage Feedback Op Amp Gain and Bandwidth

MT-033 TUTORIAL Voltage Feedback Op Amp Gain and Bandwidth INTRODUCTION This tutorial examines the common ways to specify op amp gain and bandwidth. It should be noted that this discussion applies to voltage feedback (VFB) op amps—current feedback (CFB) op amps are discussed in a later tutorial (MT-034). OPEN-LOOP GAIN Unlike the ideal op amp, a practical op amp has a finite gain. The open-loop dc gain (usually referred to as AVOL) is the gain of the amplifier without the feedback loop being closed, hence the name “open-loop.” For a precision op amp this gain can be vary high, on the order of 160 dB (100 million) or more. This gain is flat from dc to what is referred to as the dominant pole corner frequency. From there the gain falls off at 6 dB/octave (20 dB/decade). An octave is a doubling in frequency and a decade is ×10 in frequency). If the op amp has a single pole, the open-loop gain will continue to fall at this rate as shown in Figure 1A. A practical op amp will have more than one pole as shown in Figure 1B. The second pole will double the rate at which the open- loop gain falls to 12 dB/octave (40 dB/decade). If the open-loop gain has dropped below 0 dB (unity gain) before it reaches the frequency of the second pole, the op amp will be unconditionally stable at any gain. This will be typically referred to as unity gain stable on the data sheet. -

Adapting Techniques to Improve Efficiency in Radio Frequency

electronics Article Adapting Techniques to Improve Efficiency in Radio Frequency Power Amplifiers for Visible Light Communications Daniel G. Aller 1,* , Diego G. Lamar 1, Juan Rodriguez 2, Pablo F. Miaja 1 , Valentin Francisco Romero 3, Jose Mendiolagoitia 3 and Javier Sebastian 1 1 Power Supplies Group—Electrical Engineering Department of the University of Oviedo, 33204 Gijon, Spain; [email protected] (D.G.L.); [email protected] (P.F.M.); [email protected] (J.S.) 2 Center for Industrial Electronics—Polytechnic University of Madrid, 28006 Madrid, Spain; [email protected] 3 Thyssenkrupp Elevator Innovation Center S A U—Thyssenkrupp AG, 33203 Gijon, Spain; [email protected] (V.F.R.); [email protected] (J.M.) * Correspondence: [email protected]; Tel.: +34-985-182-578 Received: 30 November 2019; Accepted: 3 January 2020; Published: 10 January 2020 Abstract: It is well known that modern wireless communications systems need linear, wide bandwidth, efficient Radio Frequency Power Amplifiers (RFPAs). However, conventional configurations of RFPAs based on Class A, Class B, and Class AB exhibit extremely low efficiencies when they manage signals with a high Peak-to-Average Power Ratio (PAPR). Traditionally, a number of techniques have been proposed either to achieve linearity in the case of efficient Switching-Mode RFPAs or to improve the efficiency of linear RFPAs. There are two categories in the application of aforementioned techniques. First, techniques based on the use of Switching-Mode DC–DC converters with a very-fast-output response (faster than 1 µs). Second, techniques based on the interaction of several RFPAs. The current expansion of these techniques is mainly due to their application in cellphone networks, but they can also be applied in other promising wireless communications systems such as Visible Light Communication (VLC). -

Chapter 3 FILTERS

Chapter 3 FILTERS Most images are a®ected to some extent by noise, that is unexplained variation in data: disturbances in image intensity which are either uninterpretable or not of interest. Image analysis is often simpli¯ed if this noise can be ¯ltered out. In an analogous way ¯lters are used in chemistry to free liquids from suspended impurities by passing them through a layer of sand or charcoal. Engineers working in signal processing have extended the meaning of the term ¯lter to include operations which accentuate features of interest in data. Employing this broader de¯nition, image ¯lters may be used to emphasise edges | that is, boundaries between objects or parts of objects in images. Filters provide an aid to visual interpretation of images, and can also be used as a precursor to further digital processing, such as segmentation (chapter 4). Most of the methods considered in chapter 2 operated on each pixel separately. Filters change a pixel's value taking into account the values of neighbouring pixels too. They may either be applied directly to recorded images, such as those in chapter 1, or after transformation of pixel values as discussed in chapter 2. To take a simple example, Figs 3.1(b){(d) show the results of applying three ¯lters to the cashmere ¯bres image, which has been redisplayed in Fig 3.1(a). ² Fig 3.1(b) is a display of the output from a 5 £ 5 moving average ¯lter. Each pixel has been replaced by the average of pixel values in a 5 £ 5 square, or window centred on that pixel. -

AN-937 Designing Amplifier Circuits

AN-937 APPLICATION NOTE One Technology Way • P. O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com Designing Amplifier Circuits: How to Avoid Common Problems by Charles Kitchin INTRODUCTION down toward the negative supply. The bias voltage is amplified When compared to assemblies of discrete semiconductors, by the closed-loop dc gain of the amplifier. modern operational amplifiers (op amps) and instrumenta- This process can be lengthy. For example, an amplifier with a tion amplifiers (in-amps) provide great benefits to designers. field effect transistor (FET) input, having a 1 pA bias current, Although there are many published articles on circuit coupled via a 0.1-μF capacitor, has an IC charging rate, I/C, of applications, all too often, in the haste to assemble a circuit, 10–12/10–7 = 10 μV per sec basic issues are overlooked leading to a circuit that does not function as expected. This application note discusses the most or 600 μV per minute. If the gain is 100, the output drifts at common design problems and offers practical solutions. 0.06 V per minute. Therefore, a casual lab test, using an ac- coupled scope, may not detect this problem, and the circuit MISSING DC BIAS CURRENT RETURN PATH may not fail until hours later. It is important to avoid this One of the most common application problems encountered is problem altogether. the failure to provide a dc return path for bias current in ac- +VS coupled op amp or in-amp circuits. -

A Multidimensional Filtering Framework with Applications to Local Structure Analysis and Image Enhancement

Linkoping¨ Studies in Science and Technology Dissertation No. 1171 A Multidimensional Filtering Framework with Applications to Local Structure Analysis and Image Enhancement Bjorn¨ Svensson Department of Biomedical Engineering Linkopings¨ universitet SE-581 85 Linkoping,¨ Sweden http://www.imt.liu.se Linkoping,¨ April 2008 A Multidimensional Filtering Framework with Applications to Local Structure Analysis and Image Enhancement c 2008 Bjorn¨ Svensson Department of Biomedical Engineering Linkopings¨ universitet SE-581 85 Linkoping,¨ Sweden ISBN 978-91-7393-943-0 ISSN 0345-7524 Printed in Linkoping,¨ Sweden by LiU-Tryck 2008 Abstract Filtering is a fundamental operation in image science in general and in medical image science in particular. The most central applications are image enhancement, registration, segmentation and feature extraction. Even though these applications involve non-linear processing a majority of the methodologies available rely on initial estimates using linear filters. Linear filtering is a well established corner- stone of signal processing, which is reflected by the overwhelming amount of literature on finite impulse response filters and their design. Standard techniques for multidimensional filtering are computationally intense. This leads to either a long computation time or a performance loss caused by approximations made in order to increase the computational efficiency. This dis- sertation presents a framework for realization of efficient multidimensional filters. A weighted least squares design criterion ensures preservation of the performance and the two techniques called filter networks and sub-filter sequences significantly reduce the computational demand. A filter network is a realization of a set of filters, which are decomposed into a structure of sparse sub-filters each with a low number of coefficients.