Leakage Current: Moore’S Law Meets Static Power

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Imperial College London Department of Physics Graphene Field Effect

Imperial College London Department of Physics Graphene Field Effect Transistors arXiv:2010.10382v2 [cond-mat.mes-hall] 20 Jul 2021 By Mohamed Warda and Khodr Badih 20 July 2021 Abstract The past decade has seen rapid growth in the research area of graphene and its application to novel electronics. With Moore's law beginning to plateau, the need for post-silicon technology in industry is becoming more apparent. Moreover, exist- ing technologies are insufficient for implementing terahertz detectors and receivers, which are required for a number of applications including medical imaging and secu- rity scanning. Graphene is considered to be a key potential candidate for replacing silicon in existing CMOS technology as well as realizing field effect transistors for terahertz detection, due to its remarkable electronic properties, with observed elec- tronic mobilities reaching up to 2 × 105 cm2 V−1 s−1 in suspended graphene sam- ples. This report reviews the physics and electronic properties of graphene in the context of graphene transistor implementations. Common techniques used to syn- thesize graphene, such as mechanical exfoliation, chemical vapor deposition, and epitaxial growth are reviewed and compared. One of the challenges associated with realizing graphene transistors is that graphene is semimetallic, with a zero bandgap, which is troublesome in the context of digital electronics applications. Thus, the report also reviews different ways of opening a bandgap in graphene by using bi- layer graphene and graphene nanoribbons. The basic operation of a conventional field effect transistor is explained and key figures of merit used in the literature are extracted. Finally, a review of some examples of state-of-the-art graphene field effect transistors is presented, with particular focus on monolayer graphene, bilayer graphene, and graphene nanoribbons. -

The Reliability of the Silicon Nitride Dielectric in Capacitive MEMS

The Pennsylvania State University The Graduate School Department of Materials Science and Engineering THE RELIABILITY OF THE SILICON NITRIDE DIELECTRIC IN CAPACITIVE MEMS SWITCHES A Thesis in Materials Science and Engineering by Abuzer Dogan © 2005 Abuzer Dogan Submitted in Partial Fulfillment of the Requirements for the Degree of Master of Science August 2005 I grant The Pennsylvania State University the nonexclusive right to use this work for the University's own purposes and to make single copies of the work available to the public on a not-for-profit basis if copies are not otherwise available. Abuzer Dogan We approve the thesis of Abuzer Dogan. Date of Signature Susan Trolier-McKinstry Professor of Ceramic Science and Engineering Thesis Advisor Michael Lanagan Associate Professor of Engineering Science and Mechanics and Materials Science and Engineering Mark Horn Associate Professor of Engineering Science and Mechanics James P. Runt Professor of Polymer Science Associate Head for Graduate Studies iii ABSTRACT Silicon nitride thin film dielectrics can be used in capacitive radio frequency micro-electromechanical systems switches since they provide a low insertion loss, good isolation, and low return loss. The lifetime of these switches is believed to be adversely affected by charge trapping in the silicon nitride. These charges cause the metal bridge to be partially or fully pulled down, degrading the on-off ratio of the switch. Little information is available in the literature providing a fundamental solution to this problem. Consequently, the goals of this research were to characterize SixNy–based MIM (Metal-Insulator-Metal) capacitors and capacitive MEMS switches to measure the current-voltage response. -

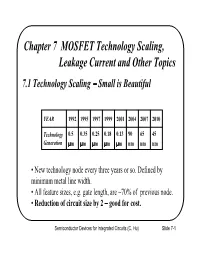

MOSFET Technology Scaling, Leakage Current, and Other Topics

Chapter 7 MOSFET Technology Scaling, Leakage Current and Other Topics 7.1 Technology Scaling Small is Beautiful YEAR 1992 1995 1997 1999 2001 2004 2007 2010 Technology 0.5 0.35 0.25 0.18 0.13 90 65 45 Generation µµµm µµµm µµµm µµµm µµµm nm nm nm • New technology node every three years or so. Defined by minimum metal line width. • All feature sizes, e.g. gate length, are ~70% of previous node. • Reduction of circuit size by 2 good for cost. Semiconductor Devices for Integrated Circuits (C. Hu) Slide 7-1 International Technology Roadmap for Semiconductors, 1999 Edition Year of Shipment 1999 2002 2005 2008 2011 2014 DRAM metal half pitch 180 130 100 70 50 35 (nm) MPU physical Lg (nm) 140 85 65 45 32 22 Tox (nm) 1.5-1.8 1.5-1.9 1-1.5 0.8-1.2 0.6-0.8 0.5-0.6 VDD 1.5-1.8 1.2-1.5 0.9-1.2 0.6-0.9 0.5-0.6 0.3-0.6 µµµ µµµ Ion,HP ( A/ m) 750/350 750/350 750/350 750/350 750/350 750/350 µµµ Ioff,HP (nA/ m) 5 10 20 40 60 160 µµµ µµµ Ion,LP ( A/ m) 490/230 490/230 490/230 490/230 490/230 490/230 µµµ Ioff,LP (pA/ m) 7 10 20 40 80 160 No known solutions •Vdd is reduced at each node to contain power consumption in spite of rising transistor density and frequency •Tox is reduced to raise I on for speed consideration Semiconductor Devices for Integrated Circuits (C. -

Leakage Current and Breakdown Electric-Field Studies on Ultrathin

APPLIED PHYSICS LETTERS 87, 182904 ͑2005͒ Leakage current and breakdown electric-field studies on ultrathin atomic-layer-deposited Al2O3 on GaAs ͒ H. C. Lin and P. D. Yea School of Electrical and Computer Engineering, Purdue University, West Lafayette, Indiana 47907 G. D. Wilk Advanced Semiconductor Materials (ASM) America, 3440 East University Drive, Phoenix, Arizona 85034 ͑Received 29 June 2005; accepted 1 September 2005; published online 25 October 2005͒ Atomic-layer deposition ͑ALD͒ provides a unique opportunity to integrate high-quality gate dielectrics on III-V compound semiconductors. We report detailed leakage current and breakdown electric-field characteristics of ultrathin Al2O3 dielectrics on GaAs grown by ALD. The leakage current in ultrathin Al2O3 on GaAs is comparable to or even lower than that of state-of-the-art SiO2 on Si, not counting the high-k dielectric properties for Al2O3. A Fowler-Nordheim tunneling analysis on the GaAs/Al2O3 barrier height is also presented. The breakdown electric field of Al2O3 is measured as high as 10 MV/cm as a bulk property. A significant enhancement on breakdown electric field up to 30 MV/cm is observed as the film thickness approaches to 1 nm. © 2005 American Institute of Physics. ͓DOI: 10.1063/1.2120904͔ Al2O3 is a widely used insulating material for gate di- sured as high as 10 MV/cm for films thicker than 50 Å, electric, tunneling barrier, and protection coating due to its which is near the bulk breakdown electric field for ALD excellent dielectric properties, strong adhesion to dissimilar Al2O3. A significant enhancement on breakdown electric materials, and its thermal and chemical stabilities. -

Analyzing the Effect of Gate Dielectric on the Leakage Currents

MATEC Web of Conferences57, 01028 (2016) DOI: 10.1051/matecconf/2016 57 01028 ICAET - 2016 Analyzing the effect of gate dielectric on the leakage currents Sakshi, Sandeep Dhariwal and Amandeep Singh Lovely Professional University- Phagwara, India Abstract. An analytical threshold voltage model for MOSFETs has been developed using different gate dielectric oxides by using MATLAB software. This paper explains the dependency of threshold voltage on the dielectric material. The variation in the subthreshold currents with the change in the threshold voltage sue to the change of dielectric material has also been studied. Index Terms— threshold voltage, gate dielectric oxides, subthreshold currents Basic material properties which are important for the selection of alternative gate dielectric are dielectric permittivity, band gap, band alignment with respect to 1 INTRODUCTION silicon, thermodynamic stability, film morphology and Earlier the VLSI designers were mainly concerned about uniformity, interface quality, and reliability [4]. the performance and miniaturization of the VLSI devices. For the last few years, power dissipation has been a serious issue because of the significant growth in portable computing and wireless communication. For more than 40 years, silicon dioxide has been used as dielectric because of its manufacturability and providing a continuous improved transistor performance as it is grown thinner and thinner [1-2]. The scaling of gate dielectric is done to improve the MOS transistor performance. The continuous scaling down of physical thickness of the gate dielectric and gate length has improved device performance and increased packing densities. Because of continuous scaling, the silicon dioxide dielectric thickness has been reduced to such an extent that further scaling will lead to increase in poly- Si gate depletion, gate dopant penetration, power consumption, etc. -

The Bipolar Junction Transistor (BJT)

CO2005: Electronics I The Bipolar Junction Transistor (BJT) 張大中 中央大學 通訊工程系 [email protected] 中央大學通訊系 張大中 Electronics I, Neamen 3th Ed. 1 Bipolar Transistor Structures 19 17 N D 10 N P 10 15 N D 10 中央大學通訊系 張大中 Electronics I, Neamen 3th Ed. 2 Forward-Active Mode in the NPN Transistor Because of the large concentration gradient in the base region, electrons injected from the emitter diffuse across the base into the BC space- charge region, where the E-field e sweeps them into the collector region. 中央大學通訊系 張大中 Electronics I, Neamen 3th Ed. 3 Currents in Emitter, Collector, and Base Emitter Current: Exponential function of the BE voltage Collector Current: Ignoring the recombination in the base region (the base width is very tiny, micrometer), the collect current is proportional to the emitter injection current and is independent of the reverse-biased BC voltage. Hence, the collector current is controlled by the BE voltage. Base Current: BE forward-biased current iB1 N D,E N P,B Base recombination current iB2 iC iB1, iE iB iC iB1 iC 中央大學通訊系 張大中 Electronics I, Neamen 3th Ed. 4 Common-Emitter Configuration i C Common-emitter current gain iB The power supply voltage Vcc iE iB iC (1)iB must be sufficiently large to keep BC junction reverse i i biased. C (1) E 中央大學通訊系 張大中 Electronics I, Neamen 3th Ed. 5 中央大學通訊系 張大中 Electronics I, Neamen 3th Ed. 6 Forward-Active Mode in the PNP Transistor 中央大學通訊系 張大中 Electronics I, Neamen 3th Ed. 7 Circuit Symbols and Conventions The arrowhead is always placed on the emitter terminal, and it indicates the direction of the emitter current. -

Leakage Power in CMOS and Its Reduction Techniques

ISSN (Print) : 2320 – 3765 ISSN (Online): 2278 – 8875 International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering (An ISO 3297: 2007 Certified Organization) Vol. 4, Issue 9, September 2015 Leakage Power in CMOS and Its Reduction Techniques Karunakar Reddy Kallam1, Pradeep Karumanchi2 Final Year B.Tech, Dept. of Electronics and Telecommunication Engineering, UCEK – JNTUK, Andhra Pradesh, India1 Final Year B.Tech, Dept. of Electronics and Telecommunication Engineering, UCEK – JNTUK, Andhra Pradesh, India2 ABSTRACT:The Power efficiency is the major concern in the field of integrated electronics. With the increase in number of transistors in a chip every year, the complexity of the chip increases and which in turn leads to increase in power consumption levels.Consequently the decrease in transistor gate length as well as path length also led to the increase in resistance of the chip escalating the power usage. So, reduction of power consumption levels has become a desperate task for the researchers all around the world. Leveraging the power includes many techniques like optimizing the logic-design, enhancing the clock distribution network and importantly reduction of power dissipation.Coming to the point of power dissipation,leakage power is one of the major source.Leakage power is primarily the result of unwanted subthreshold current in the transistor channel when the transistor is turned off. Practically, the leakage power has become inevitable.The only thing we are able to do is to reduce the leakage power to some extent.In this paperwe are going to discuss the sources of leakage power and two techniques for mitigating the leakage power which are Transistor stacking and self- adjustable voltage level circuit. -

Leakage Currents in Nanometer CMOS

ISLPED 06 Proposal for half-day Tutorial Leakage Currents in Nanometer CMOS Domenik Helms Wolfgang Nebel OFFIS Research Institute University of Oldenburg [email protected] [email protected] Abstract: In only 5 years, leakage developed from an academic corner phenomenon to a central problem of embedded system design. In sub 90nm designs the leakage power will be larger than the dynamic power. The intention of this tutorial is to present the state-of-the-art in leakage modelling, estimation and reduction methodologies. Schedule Leakage physics (40 min): From a transistor view, the known sources of leakage are reviewed and their dependencies on physical parameters as temperature, voltage-levels at the terminals, length width and thickness of the structures, doping level, etc. The introduction to the basics of leakage currents enables deeper understanding of the later parts dealing with estimation and optimization of the leakage currents. • Subthreshold current including drain induced barrier lowering (DIBL) and other short channel effects (SCE’s). Especially thermal threshold voltage, body voltage and source voltage dependence is discussed. • Gate leakage presenting an easy quantum-mechanical introduction to the tunnel- effect and discussing different oxide tunnelling mechanisms. Especially influence of gate-voltage, temperature and oxide thickness needs further attention. • PN-junction leakage carried by 3 mechanisms: drift, electron-hole generation and band to band tunnelling (BTBT) with a focus on gate induced drain leakage (GIDL) which will make PN-junction leakage becoming the second largest part in the total leakage budget within the next years. • Hot carrier injection (HCI) and Punchthrough, both having minor impact will be briefly reviewed for the sake of completeness. -

ECE606: Solid State Devices Lecture 18 Bipolar Transistors A

ECE606: Solid State Devices Lecture 18 Bipolar Transistors a) Introduction b) Design (I) Gerhard Klimeck [email protected] 1 Klimeck – ECE606 Fall 2012 – notes adopted from Alam Background E B C E C Base! Point contact Germanium transistor Ralph Bray from Purdue missed the invention of transistors. http://www.electronicsweekly.com/blogs/david-manners-semiconductor-blog/2009/02/how-purdue-university-nearly-i.html http://www.physics.purdue.edu/about_us/history/semi_conductor_research.shtml Transistor research was also in advanced stages in Europe (radar). Klimeck – ECE606 Fall 2012 – notes adopted from Alam 2 Shockley’s Bipolar Transistors … n+ emitter n+ Double p base n-collector Diffused BJT n+ n+ p n n+ emitter base collector Klimeck – ECE606 Fall 2012 – notes adopted from Alam Modern Bipolar Junction Transistors (BJTs) Base Emitter Collector N+ N- P+ N+ N SiGe intrinsic base P- Dielectric trench Why do we need all these design? Transistor speed increases as the electron's travel distance is reduced SiGe Layer Klimeck – ECE606 Fall 2012 – notes adopted from Alam 4 Symbols and Convention E Symbols Poly emitter N+ NPN PNP Collector B P Low-doped base Collector Base Base N Collector doping optimization Emitter Emitter C IC+I B+I E=0 (DC) VEB +V BC +V CE =0 Klimeck – ECE606 Fall 2012 – notes adopted from Alam 5 Outline 1) Equilibrium and forward band-diagram 2) Currents in bipolar junction transistors 3) Eber’s Moll model 4) Intermediate Summary 5) Current gain in BJTs 6) Considerations for base doping 7) Considerations for collector doping -

Leakage Power Reduction Techniques in CMOS VLSI Circuits – a Survey

ISSN: 2455-2631 © May 2016 IJSDR | Volume 1, Issue 5 Leakage Power Reduction Techniques in CMOS VLSI Circuits – A Survey 1D.vijayalakshmi, 2Dr P.C Kishore Raja 1Assistant Professor, BIT, Bangalore 2HOD, Department of E&C, Saveetha University Abstract: This paper covers the various techniques used to reduce Leakage power in CMOS circuits. The CMOS has been the leading technology in today’s world of mobile communication due to its low power consumption. Reduction of leakage power in CMOS has been the research interest for the last couple of years. In CMOS integrated circuit design there is an important trade-off between technology scaling and static power consumption. In today’s CMOS technology the leakage power consumption plays a significant role. As we approach Nano-scale design the total chip power consumption becomes dependent on leakage power. Increasing the battery life in mobile wireless communication and mobile computing and similar other applications is the topic of research nowadays. Further, since the leakage of battery exists even when devices are in idle state makes leakage power loss most critical in CMOS VLSI circuits. Many techniques have been evolved to tackle the problem and it is still in progress. This paper also focuses on a new technique called scan chain technique. Keywords: CMOS, Leakage power, VLSI circuits, multimedia applications, Static power, Nano Scale, LSSR, DUT 1. Introduction The rapid growth in semiconductor technology through the use of deep-sub micron processes has led the feature sizes to be shrinking; thereby integrating extremely complex functionality on a single chip. In the ever increasing market of mobile hand- held devices used all over the world today, the battery-powered electronic system forms the backbone. -

Lecture 6 Leakage and Low-Power Design

Lecture 6 Leakage and Low-Power Design R. Saleh Dept. of ECE University of British Columbia [email protected] RAS Lecture 6 1 Methods of Reducing Leakage Power • So far we have discussed dynamic power reduction techniques which result from switching-related currents • The transistor also exhibits many current leakage mechanisms that cause power dissipation when it is not switching • In this lecture, we will explore the different types of leakage currents and their trends • We will then describe ways to limit various types of leakage • We will also re-examine the DSM transistor in more detail as a side-effect of this study • Readings: – Sections of Chapter 2 and 3 in HJS – Many books and papers on DSM leakage power – Alvin Loke Presentation (SSCS Technical Seminar, 2007) RAS Lecture 6 2 Basic CMOS Transistor Structure • Typical process today uses twin-tub CMOS technology • Shallow-trench isolation, thin-oxide, lightly-doped drain/source • Salicided drain/source/gate to reduce resistance • extensive channel engineering for VT-adjust, punchthrough prevention, etc. • Need to examine some details to understand leakage n+ n+ p+ p+ STI p-well STI n-well STI common substrate RAS Lecture 6 3 Sources of Leakages Leakage is a big problem in the recent CMOS technology nodes A variety of leakage mechanisms exist in the DSM transistor Acutal leakage levels vary depending on biasing and physical parameters at the technology node (doping, tox, VT, W, L, etc.) I1: Subthreshold Current I2: DIBL I2’: Punchthrough I3: Thin Oxide Gate Tunneling I4: GIDL I5: -

AN-1001 Understanding Power MOSFET Parameters

AN-1001 Understanding Power MOSFET Parameters www.taiwansemi.com Taiwan Semiconductor Content 1. Absolute Maximum Ratings ................................................................................................................................... 3 1.1 Drain-Source Voltage (VDS) ............................................................................................................................. 3 1.2 Gate-Source Voltage (VGS) .............................................................................................................................. 3 1.3 Continuous Drain Current (ID) ......................................................................................................................... 3 1.4 Pulsed Drain Current (IDM) .............................................................................................................................. 4 1.5 Single Pulse Avalanche Current (IAS) ............................................................................................................... 4 1.6 Single Pulse Avalanche Energy (EAS) ............................................................................................................... 4 1.7 Total Power Dissipation (PD) ........................................................................................................................... 5 1.8 Operating Junction and Storage Temperature Range (TJ,TSTG) ...................................................................... 5 2. Thermal Performance ...........................................................................................................................................