ECE606: Solid State Devices Lecture 18 Bipolar Transistors A

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Imperial College London Department of Physics Graphene Field Effect

Imperial College London Department of Physics Graphene Field Effect Transistors arXiv:2010.10382v2 [cond-mat.mes-hall] 20 Jul 2021 By Mohamed Warda and Khodr Badih 20 July 2021 Abstract The past decade has seen rapid growth in the research area of graphene and its application to novel electronics. With Moore's law beginning to plateau, the need for post-silicon technology in industry is becoming more apparent. Moreover, exist- ing technologies are insufficient for implementing terahertz detectors and receivers, which are required for a number of applications including medical imaging and secu- rity scanning. Graphene is considered to be a key potential candidate for replacing silicon in existing CMOS technology as well as realizing field effect transistors for terahertz detection, due to its remarkable electronic properties, with observed elec- tronic mobilities reaching up to 2 × 105 cm2 V−1 s−1 in suspended graphene sam- ples. This report reviews the physics and electronic properties of graphene in the context of graphene transistor implementations. Common techniques used to syn- thesize graphene, such as mechanical exfoliation, chemical vapor deposition, and epitaxial growth are reviewed and compared. One of the challenges associated with realizing graphene transistors is that graphene is semimetallic, with a zero bandgap, which is troublesome in the context of digital electronics applications. Thus, the report also reviews different ways of opening a bandgap in graphene by using bi- layer graphene and graphene nanoribbons. The basic operation of a conventional field effect transistor is explained and key figures of merit used in the literature are extracted. Finally, a review of some examples of state-of-the-art graphene field effect transistors is presented, with particular focus on monolayer graphene, bilayer graphene, and graphene nanoribbons. -

PN Junction Is the Most Fundamental Semiconductor Device

Fundamentals of Microelectronics CH1 Why Microelectronics? CH2 Basic Physics of Semiconductors CH3 Diode Circuits CH4 Physics of Bipolar Transistors CH5 Bipolar Amplifiers CH6 Physics of MOS Transistors CH7 CMOS Amplifiers CH8 Operational Amplifier As A Black Box 1 Chapter 2 Basic Physics of Semiconductors 2.1 Semiconductor materials and their properties 2.2 PN-junction diodes 2.3 Reverse Breakdown 2 Semiconductor Physics Semiconductor devices serve as heart of microelectronics. PN junction is the most fundamental semiconductor device. CH2 Basic Physics of Semiconductors 3 Charge Carriers in Semiconductor To understand PN junction’s IV characteristics, it is important to understand charge carriers’ behavior in solids, how to modify carrier densities, and different mechanisms of charge flow. CH2 Basic Physics of Semiconductors 4 Periodic Table This abridged table contains elements with three to five valence electrons, with Si being the most important. CH2 Basic Physics of Semiconductors 5 Silicon Si has four valence electrons. Therefore, it can form covalent bonds with four of its neighbors. When temperature goes up, electrons in the covalent bond can become free. CH2 Basic Physics of Semiconductors 6 Electron-Hole Pair Interaction With free electrons breaking off covalent bonds, holes are generated. Holes can be filled by absorbing other free electrons, so effectively there is a flow of charge carriers. CH2 Basic Physics of Semiconductors 7 Free Electron Density at a Given Temperature E n 5.21015T 3/ 2 exp g electrons/ cm3 i 2kT 0 10 3 ni (T 300 K) 1.0810 electrons/ cm 0 15 3 ni (T 600 K) 1.5410 electrons/ cm Eg, or bandgap energy determines how much effort is needed to break off an electron from its covalent bond. -

Junction Field Effect Transistor (JFET)

Junction Field Effect Transistor (JFET) The single channel junction field-effect transistor (JFET) is probably the simplest transistor available. As shown in the schematics below (Figure 6.13 in your text) for the n-channel JFET (left) and the p-channel JFET (right), these devices are simply an area of doped silicon with two diffusions of the opposite doping. Please be aware that the schematics presented are for illustrative purposes only and are simplified versions of the actual device. Note that the material that serves as the foundation of the device defines the channel type. Like the BJT, the JFET is a three terminal device. Although there are physically two gate diffusions, they are tied together and act as a single gate terminal. The other two contacts, the drain and source, are placed at either end of the channel region. The JFET is a symmetric device (the source and drain may be interchanged), however it is useful in circuit design to designate the terminals as shown in the circuit symbols above. The operation of the JFET is based on controlling the bias on the pn junction between gate and channel (note that a single pn junction is discussed since the two gate contacts are tied together in parallel – what happens at one gate-channel pn junction is happening on the other). If a voltage is applied between the drain and source, current will flow (the conventional direction for current flow is from the terminal designated to be the gate to that which is designated as the source). The device is therefore in a normally on state. -

The P-N Junction (The Diode)

Lecture 18 The P-N Junction (The Diode). Today: 1. Joining p- and n-doped semiconductors. 2. Depletion and built-in voltage. 3. Current-voltage characteristics of the p-n junction. Questions you should be able to answer by the end of today’s lecture: 1. What happens when we join p-type and n-type semiconductors? 2. What is the width of the depletion region? How does it relate to the dopant concentration? 3. What is built-in voltage? How to calculate it based on dopant concentrations? How to calculate it based on Fermi levels of semiconductors forming the junction? 4. What happens when we apply voltage to the p-n junction? What is forward and reverse bias? 5. What is the current-voltage characteristic for the p-n junction diode? Why is it different from a resistor? 1 From previous lecture we remember: What happens when you join p-doped and n-doped pieces of semiconductor together? When materials are put in contact the carriers flow under driving force of diffusion until chemical potential on both sides equilibrates, which would mean that the position of the Fermi level must be the same in both p and n sides. This results in band bending: - + - + + - - Holes diffuse + Electrons diffuse The electrons will diffuse into p-type material where they will recombine with holes (fill in holes). And holes will diffuse into the n-type materials where they will recombine with electrons. 2 This means that eventually in vicinity of the junction all free carriers will be depleted leaving stripped ions behind, which would produce an electric field across the junction: The electric field results from the deviation from charge neutrality in the vicinity of the junction. -

The Pennsylvania State University the Graduate School THE

The Pennsylvania State University The Graduate School THE EFFECTS OF INTERFACE AND SURFACE CHARGE ON TWO DIMENSIONAL TRANSITORS FOR NEUROMORPHIC, RADIATION, AND DOPING APPLICATIONS A Dissertation in Electrical Engineering by Andrew J. Arnold © 2020 Andrew J. Arnold Submitted in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy August 2020 The dissertation of Andrew J. Arnold was reviewed and approved by the following: Thomas Jackson Professor of Electrical Engineering Co-Chair of Committee Saptarshi Das Assistant Professor of Engineering Science and Mechanics Dissertation Advisor Co-Chair of Committee Swaroop Ghosh Assistant Professor of Electrical Engineering Rongming Chu Associate Professor of Electrical Engineering Sukwon Choi Assistant Professor of Mechanical Engineering Kultegin Aydin Professor of Electrical Engineering Head of the Department of Electrical Engineering ii Abstract The scaling of silicon field effect transistors (FETs) has progressed exponentially following Moore’s law, and is nearing fundamental limitations related to the materials and physics of the devices. Alternative materials are required to overcome these limitations leading to increasing interest in two dimensional (2D) materials, and transition metal dichalcogenides (TMDs) in particular, due to their atomically thin nature which provides an advantage in scalability. Numerous investigations within the literature have explored various applications of these materials and assessed their viability as a replacement for silicon FETs. This dissertation focuses on several applications of 2D FETs as well as an exploration into one of the most promising methods to improve their performance. Neuromorphic computing is an alternative method to standard computing architectures that operates similarly to a biological nervous system. These systems are composed of neurons and operate based on pulses called action potentials. -

ECE 255, MOSFET Basic Configurations

ECE 255, MOSFET Basic Configurations 8 March 2018 In this lecture, we will go back to Section 7.3, and the basic configurations of MOSFET amplifiers will be studied similar to that of BJT. Previously, it has been shown that with the transistor DC biased at the appropriate point (Q point or operating point), linear relations can be derived between the small voltage signal and current signal. We will continue this analysis with MOSFETs, starting with the common-source amplifier. 1 Common-Source (CS) Amplifier The common-source (CS) amplifier for MOSFET is the analogue of the common- emitter amplifier for BJT. Its popularity arises from its high gain, and that by cascading a number of them, larger amplification of the signal can be achieved. 1.1 Chararacteristic Parameters of the CS Amplifier Figure 1(a) shows the small-signal model for the common-source amplifier. Here, RD is considered part of the amplifier and is the resistance that one measures between the drain and the ground. The small-signal model can be replaced by its hybrid-π model as shown in Figure 1(b). Then the current induced in the output port is i = −gmvgs as indicated by the current source. Thus vo = −gmvgsRD (1.1) By inspection, one sees that Rin = 1; vi = vsig; vgs = vi (1.2) Thus the open-circuit voltage gain is vo Avo = = −gmRD (1.3) vi Printed on March 14, 2018 at 10 : 48: W.C. Chew and S.K. Gupta. 1 One can replace a linear circuit driven by a source by its Th´evenin equivalence. -

Lecture 16 the Pn Junction Diode (III)

Lecture 16 The pn Junction Diode (III) Outline • Small-signal equivalent circuit model • Carrier charge storage –Diffusion capacitance Reading Assignment: Howe and Sodini; Chapter 6, Sections 6.4 - 6.5 6.012 Spring 2007 Lecture 16 1 I-V Characteristics Diode Current equation: ⎡ V ⎤ I = I ⎢ e(Vth )−1⎥ o ⎢ ⎥ ⎣ ⎦ I lg |I| 0.43 q kT =60 mV/dec @ 300K Io 0 0 V 0 V Io linear scale semilogarithmic scale 6.012 Spring 2007 Lecture 16 2 2. Small-signal equivalent circuit model Examine effect of small signal adding to forward bias: ⎡ ⎛ qV()+v ⎞ ⎤ ⎛ qV()+v ⎞ ⎜ ⎟ ⎜ ⎟ ⎢ ⎝ kT ⎠ ⎥ ⎝ kT ⎠ I + i = Io ⎢ e −1⎥ ≈ Ioe ⎢ ⎥ ⎣ ⎦ If v small enough, linearize exponential characteristics: ⎡ qV qv ⎤ ⎡ qV ⎤ ()kT (kT ) (kT )⎛ qv ⎞ I + i ≈ Io ⎢e e ⎥ ≈ Io ⎢e ⎜ 1 + ⎟ ⎥ ⎣⎢ ⎦⎥ ⎣⎢ ⎝ kT⎠ ⎦⎥ qV qV qv = I e()kT + I e(kT ) o o kT Then: qI i = • v kT From a small signal point of view. Diode behaves as conductance of value: qI g = d kT 6.012 Spring 2007 Lecture 16 3 Small-signal equivalent circuit model gd gd depends on bias. In forward bias: qI g = d kT gd is linear in diode current. 6.012 Spring 2007 Lecture 16 4 Capacitance associated with depletion region: ρ(x) + qNd p-side − n-side (a) xp x = xn vD VD − qNa = − QJ qNaxp ρ(x) + qNd p-side −x −x n-side (b) p p x xn xn = + > > vD VD vd VD-- − qNa x < x |q | < |Q | p p, J J = − qJ qNaxp = ∆ ∆ρ = ρ − ρ qj qNa xp (x) (x) (x) + qNd X p-side d n-side (c) x n xn − − xp xp x q = q − Q > j j j 0 − qN = −qN x − −qN a − = − ∆ a p ( axp) qj qNd xn = − qNa (xp xp) ∆ = qNa xp Depletion or junction capacitance: dqJ C j = C j (VD ) = dvD VD qεsNa Nd C j = A 2()Na + Nd ()φB −VD 6.012 Spring 2007 Lecture 16 5 Small-signal equivalent circuit model gd Cj can rewrite as: qεsNa Nd φB C j = A • 2()Na + Nd φB ()φB −VD C or, C = jo j V 1− D φB φ Under Forward Bias assume V ≈ B D 2 C j = 2C jo Cjo ≡ zero-voltage junction capacitance 6.012 Spring 2007 Lecture 16 6 3. -

The Reliability of the Silicon Nitride Dielectric in Capacitive MEMS

The Pennsylvania State University The Graduate School Department of Materials Science and Engineering THE RELIABILITY OF THE SILICON NITRIDE DIELECTRIC IN CAPACITIVE MEMS SWITCHES A Thesis in Materials Science and Engineering by Abuzer Dogan © 2005 Abuzer Dogan Submitted in Partial Fulfillment of the Requirements for the Degree of Master of Science August 2005 I grant The Pennsylvania State University the nonexclusive right to use this work for the University's own purposes and to make single copies of the work available to the public on a not-for-profit basis if copies are not otherwise available. Abuzer Dogan We approve the thesis of Abuzer Dogan. Date of Signature Susan Trolier-McKinstry Professor of Ceramic Science and Engineering Thesis Advisor Michael Lanagan Associate Professor of Engineering Science and Mechanics and Materials Science and Engineering Mark Horn Associate Professor of Engineering Science and Mechanics James P. Runt Professor of Polymer Science Associate Head for Graduate Studies iii ABSTRACT Silicon nitride thin film dielectrics can be used in capacitive radio frequency micro-electromechanical systems switches since they provide a low insertion loss, good isolation, and low return loss. The lifetime of these switches is believed to be adversely affected by charge trapping in the silicon nitride. These charges cause the metal bridge to be partially or fully pulled down, degrading the on-off ratio of the switch. Little information is available in the literature providing a fundamental solution to this problem. Consequently, the goals of this research were to characterize SixNy–based MIM (Metal-Insulator-Metal) capacitors and capacitive MEMS switches to measure the current-voltage response. -

Electrical Properties of Silicon Nanowires Schottky Barriers Prepared by MACE at Different Etching Time

Electrical Properties of Silicon Nanowires Schottky Barriers Prepared by MACE at Different Etching Time Ahlem Rouis ( [email protected] ) Universite de Monastir Faculte des Sciences de Monastir https://orcid.org/0000-0002-9480-061X Neila Hizem Universite de Monastir Faculte des Sciences de Monastir Mohamed Hassen Institut Supérieur des Sciences Appliquées et de Technologie de Sousse: Institut Superieur des Sciences Appliquees et de Technologie de Sousse Adel kalboussi Universite de Monastir Faculte des Sciences de Monastir Original Research Keywords: Electrical Properties of Silicon, Etching Time, symmetrical current-voltage, capacitance-voltage Posted Date: February 11th, 2021 DOI: https://doi.org/10.21203/rs.3.rs-185736/v1 License: This work is licensed under a Creative Commons Attribution 4.0 International License. Read Full License Electrical properties of silicon nanowires Schottky barriers prepared by MACE at different etching time Ahlem Rouis 1, *, Neila Hizem1, Mohamed Hassen2, and Adel kalboussi1. 1Laboratory of Microelectronics and Instrumentation (LR13ES12), Faculty of Science of Monastir, Avenue of Environment, University of Monastir, 5019 Monastir, Tunisia. 2Higher Institute of Applied Sciences and Technology of Sousse, Taffala City (Ibn Khaldoun), 4003 Sousse, Tunisia. * Address correspondence to E-mail: [email protected] ABSTRACT This article focused on the electrical characterization of silicon nanowires Schottky barriers following structural analysis of nanowires grown on p-type silicon by Metal (Ag) Assisted Chemical Etching (MACE) method distinguished by their different etching time (5min, 10min, 25min). The SiNWs are well aligned and distributed almost uniformly over the surface of a silicon wafer. In order to enable electrical measurement on the silicon nanowires device, Schottky barriers were performed by depositing Al on the vertically aligned SiNWs arrays. -

INA106: Precision Gain = 10 Differential Amplifier Datasheet

INA106 IN A1 06 IN A106 SBOS152A – AUGUST 1987 – REVISED OCTOBER 2003 Precision Gain = 10 DIFFERENTIAL AMPLIFIER FEATURES APPLICATIONS ● ACCURATE GAIN: ±0.025% max ● G = 10 DIFFERENTIAL AMPLIFIER ● HIGH COMMON-MODE REJECTION: 86dB min ● G = +10 AMPLIFIER ● NONLINEARITY: 0.001% max ● G = –10 AMPLIFIER ● EASY TO USE ● G = +11 AMPLIFIER ● PLASTIC 8-PIN DIP, SO-8 SOIC ● INSTRUMENTATION AMPLIFIER PACKAGES DESCRIPTION R1 R2 10kΩ 100kΩ 2 5 The INA106 is a monolithic Gain = 10 differential amplifier –In Sense consisting of a precision op amp and on-chip metal film 7 resistors. The resistors are laser trimmed for accurate gain V+ and high common-mode rejection. Excellent TCR tracking 6 of the resistors maintains gain accuracy and common-mode Output rejection over temperature. 4 V– The differential amplifier is the foundation of many com- R3 R4 10kΩ 100kΩ monly used circuits. The INA106 provides this precision 3 1 circuit function without using an expensive resistor network. +In Reference The INA106 is available in 8-pin plastic DIP and SO-8 surface-mount packages. Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners. PRODUCTION DATA information is current as of publication date. Copyright © 1987-2003, Texas Instruments Incorporated Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters. www.ti.com SPECIFICATIONS ELECTRICAL ° ± At +25 C, VS = 15V, unless otherwise specified. -

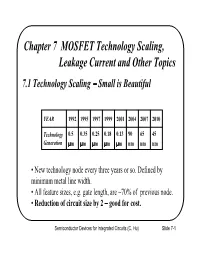

MOSFET Technology Scaling, Leakage Current, and Other Topics

Chapter 7 MOSFET Technology Scaling, Leakage Current and Other Topics 7.1 Technology Scaling Small is Beautiful YEAR 1992 1995 1997 1999 2001 2004 2007 2010 Technology 0.5 0.35 0.25 0.18 0.13 90 65 45 Generation µµµm µµµm µµµm µµµm µµµm nm nm nm • New technology node every three years or so. Defined by minimum metal line width. • All feature sizes, e.g. gate length, are ~70% of previous node. • Reduction of circuit size by 2 good for cost. Semiconductor Devices for Integrated Circuits (C. Hu) Slide 7-1 International Technology Roadmap for Semiconductors, 1999 Edition Year of Shipment 1999 2002 2005 2008 2011 2014 DRAM metal half pitch 180 130 100 70 50 35 (nm) MPU physical Lg (nm) 140 85 65 45 32 22 Tox (nm) 1.5-1.8 1.5-1.9 1-1.5 0.8-1.2 0.6-0.8 0.5-0.6 VDD 1.5-1.8 1.2-1.5 0.9-1.2 0.6-0.9 0.5-0.6 0.3-0.6 µµµ µµµ Ion,HP ( A/ m) 750/350 750/350 750/350 750/350 750/350 750/350 µµµ Ioff,HP (nA/ m) 5 10 20 40 60 160 µµµ µµµ Ion,LP ( A/ m) 490/230 490/230 490/230 490/230 490/230 490/230 µµµ Ioff,LP (pA/ m) 7 10 20 40 80 160 No known solutions •Vdd is reduced at each node to contain power consumption in spite of rising transistor density and frequency •Tox is reduced to raise I on for speed consideration Semiconductor Devices for Integrated Circuits (C. -

Transistor Basics

Transistor Basics: Collector The schematic representation of a transistor is shown to the left. Note the arrow pointing down towards the emitter. This signifies it's an NPN transistor (current flows in the direction of the arrow). See the Q1 datasheet at: www.fairchildsemi.com. Base 2N3904 A transistor is basically a current amplifier. Say we let 1mA flow into the base. We may get 100mA flowing into the collector. Note: The Emitter currents flowing into the base and collector exit through the emitter (the sum off all currents entering or leaving a node must equal zero). The gain of the transistor will be listed in the datasheet as either βDC or Hfe. The gain won't be identical even in transistors with the same part number. The gain also varies with the collector current and temperature. Because of this we will add a safety margin to all our base current calculations (i.e. if we think we need 2mA to turn on the switch we'll use 4mA just to make sure). Sample circuit and calculations (NPN transistor): Let's say we want to heat a block of metal. One way to do that is to connect a power resistor to the block and run current through the resistor. The resistor heats up and transfers some of the heat to the block of metal. We will use a transistor as a switch to control when the resistor is heating up and when it's cooling off (i.e. no current flowing in the resistor). In the circuit below R1 is the power resistor that is connected to the object to be heated.