Readingsample

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

INF 3190 Wireless Communications

Department of Informatics Networks and Distributed Systems (ND) group INF 3190 Wireless Communications Özgü Alay [email protected] Simula Research Laboratory Outline • Brief history of wireless • What is wireless communication? • Bottom-down approach – Physical layer : how can we transmit signals in air? – Link layer : multiple access – Wireless impact higher layers? • Wireless Systems – Mobile Broadband Networks – Wifi – Sensor Networks, Adhoc Networks 2 Wireless History • James C Maxwell ( 1831- 1879) laying the theoretical foundation for EM fields with his famous equations • Heinrich Hertz (1857- 1894 ) was the first to demonstrate the wave character of electrical transmission through space (1886). (Note Today the unit Hz reminds us of this discovery). • Radio invented in the 1880s by Marconi • The 1st radio broadcast took place in 1906 when Reginald A Fessenden transmitted voice and music for Christmas. • The invention of electronic vacuum tube in 1906 by Lee De Forest (1873-1961) & Robert Von Lieben (1878 – 1913) helped to reduce the size of sender and receiver . 3 Wireless History cont… • In 1915 , the first wireless voice transmission was set up between New York and San Francisco • The 1st commercial radio station started in 1920 – Note Sender & Receiver still needed huge antennas due to high transmission power. • In 1926, the first telephone in a train was available on the Berlin – Hamburg line • 1928 was the year of many field trials for TV broadcasting. John L Baird ( 1888 – 1946 ) transmitted TV across Atlantic and demonstrated color TV 4 Wireless History cont … • Invention of FM in 1933 by Edwin H Armstrong [ 1890 - 1954 ] . • 1946, Public Mobile in 25 US cities, high power transmitter on large tower. -

7: Society III

A History Of Knowledge What The Victorian Age Knew Chapter 7: Society III Piero Scaruffi (2004) www.scaruffi.com Edited and revised by Chris Hastings (2013) Abolitions • Abolition of slavery in the USA (1861) • Abolition of serfdom in Russia (1861) 2 Democracy • USA: 1865 • France: 1875 • Britain: 1918 • But not for women 3 Puritanism • 1865: The “Salvation Army” • 1873: Anthony Comstock founds the Society for the Suppression of Vice • 1874: The Woman's Christian Temperance Union is founded 4 The Invention Of Childhood • Kate Greenaway (Britain): “Under the Window: Pictures & Rhymes for Children” (1879) 5 Customs • One is a gentleman/lady not by birth but by good manners • The dandy (modeled after Bryan “Beau” Brummell of the 1800s) 6 Private Life Board games of the 1880s 7 Private Life • Moving panoramas: Before cinema and before virtual reality • Robert Baker’s proto-panorama of Edinburgh (1791) • John Banvard: Moving panorama of 1848 • Albert Smith’s panorama of the Mont Blanc, showed more than 2000 times (1852-58) • Moses Gompertz and the Poole brothers’ Myriorama (1890s) Banvard’s panorama 8 Transportation • 1825: Britain inaugurates the first railway in the world • 1840s: Boom of railways in Britain • 1869: The Union and Central Pacific railroads create the first transcontinental railroad • 1885: Gottlieb Daimler and Wilhelm Maybach invent the motorcycle • 1886: Karl Benz builds a gasoline-powered car • 1890: The first electrical subway (London) • 1900: Ferdinand von Zeppelin builds the first rigid dirigible • 1903: Wilbur and Orville -

The Great War and Wireless Communications

Chapter 1 The Great War and Wireless Communications 1.1 LAND - BOUND COMMUNICATIONS 1.1.1 The Battle of Tannenberg and the Electron Tube The guns of August 1914 thundered along a western front from Belgium through northeastern France to the Jura mountains and along an eastern front from East Prussia through Russian Poland and Austro - Hungarian Galicia. (See Figure 1.1 .) When war broke out at the beginning of that month, German leaders followed a strategy formulated by Alfred von Schlieffen nine years earlier in directing most of the available manpower and materiel against their enemies in the West, while fi ght- ing a holding action against the Russians. Fearful of a two - front war, they hoped to force France to sue for peace before the massive Russian armies could be brought effectively to bear on the much smaller German armies in East Prussia and Silesia. In the West, the Germans moved steadily through Belgium, entering Li è ge on 7 August and Brussels on 20 August, and at the same time sharply repulsed the French offensive in Alsace - Lorraine. But news from the Eastern Front was, from the German point of view, quite disturbing. Russia ’ s huge First and Second Armies, numbering some 200,000 men each, had mobilized and reached the front much faster than expected. On 17 August the Russians took the offensive, and on 20 August the Germans suffered a defeat at Gumbinnen. Soon a third of East Prussia was in Russian hands. There wasCOPYRIGHTED widespread fear and some panic MATERIALbehind German lines, and refugees streamed westward toward Berlin. -

1999-2018 INDEX This Index Covers Tube Collector Through August 2018, the TCA "Data Cache" DVD- ROM Set, and the Following TCA Special Publications: No

1999-2018 INDEX This index covers Tube Collector through August 2018, the TCA "Data Cache" DVD- ROM set, and the following TCA Special Publications: No. 1 Manhattan College Vacuum Tube Museum - List of Displays .........................1999 No. 2 Triodes in Radar: The Early VHF Era ...............................................................2000 No. 3 Auction Results ....................................................................................................2001 No. 4 A Tribute to George Clark, with audio CD ........................................................2002 No. 5 J. B. Johnson and the 224A CRT.........................................................................2003 No. 6 McCandless and the Audion, with audio CD......................................................2003 No. 7 AWA Tube Collector Group Fact Sheet, Vols. 1-6 ...........................................2004 No. 8 Vacuum Tubes in Telephone Work.....................................................................2004 No. 9 Origins of the Vacuum Tube, with audio CD.....................................................2005 No. 10 Early Tube Development at GE...........................................................................2005 No. 11 Thermionic Miscellany.........................................................................................2006 No. 12 RCA Master Tube Sales Plan, 1950....................................................................2006 No. 13 GE Tungar Bulb Data Manual................................................................. -

The Vacuum Tube a “Hollow State” Device

The Vacuum Tube A “Hollow State” Device Ken Moak KM8AM 22-Feb-18All images are property of their owners 1 What We’ll Cover • In the beginning (One element) • Diode (Two elements) • Triode (Three elements) and more • Tubes today 22-Feb-18 2 We’re still looking for a radio job What’s up guys? www.huyzebladelin.com 22-Feb-18 3 In The Beginning “One Element” 1873: British Professor Frederick Guthrie showed a negatively- charged, red-hot, iron sphere would quickly discharge A positively-charged sphere did not discharge as fast 22-Feb-18 4 In The Beginning “One Element” www.ieeeghn.org 1880: Edison received a patent for an electric lamp using “… a carbon filament or strip coiled and connected to platina contact wires …" 22-Feb-18 5 In The Beginning “One Element” A red hot cathode emits a cloud of electrons www.ieeeghn.org www.r-type.org 22-Feb-18 6 The Diode “Two Elements” • 1883: The Edison Effect - Edison thought his bulbs became dark from carbon atoms from the filament hitting the glass • Tried a second, positively-charged element in the bulb to attract the negative atoms away from hitting the glass • A positive charge relative to the filament caused current flow in the circuit. When reversed, no http://handley.org.uk current flowed 22-Feb-18 7 The Diode “Two Elements” 1904: The Fleming Valve – John Fleming, using some Edison bulbs, observed that if he applied alternating current (AC) to the bulb, only one half of the cycle passed. It was rectifying the AC to produce a pulsed direct current (DC) wb0nni.dakotamade.com yourdictionary.com Science Museum/Science & Society Picture Library 22-Feb-18 8 The Diode “Two Elements” Plate current only flows when plate is positive relative to the cathode http://www.angelfire.com/electronic/funwithtubes/Basics_03_Diodes.html 22-Feb-18 9 The Triode “Three Elements” 1906: Robert von Lieben filed for a patent for a cathode ray tube. -

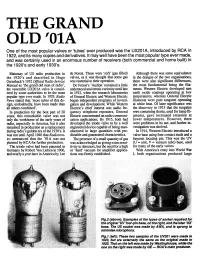

THE GRAND OLD '01A One of the Most Popular Valves Or `Tubes' Ever Produced Was the UX201 A, Introduced by RCA in 1922, and Its Many Copies and Derivatives

THE GRAND OLD '01A One of the most popular valves or `tubes' ever produced was the UX201 A, introduced by RCA in 1922, and its many copies and derivatives. It may well have been the most popular type ever made, and was certainly used in an enormous number of receivers (both commercial and home built) in the 1920's and early 1930's. Mainstay of US radio production in de Forest. These were `soft' (gas filled) Although there was some equivalence the 1920's and described in Hugo valves, as it was thought that some gas in the designs of the two organisations, Gernsback's 1932 Official Radio Service was essential to their operation. there were also significant differences, Manual as 'the grand old man of radio', De Forest's `Audion' remained a little the most fundamental being the fila- the venerable UX201A valve is consid- understood and erratic curiosity until late ments. Western Electric developed rare ered by some authorities to be the most in 1912, when the research laboratories earth oxide coatings operating at low popular type ever made. In 1929, Radio of General Electric and Western Electric temperatures, whereas General Electric News stated that 'more tubes of this de- began independent programs of investi- filaments were pure tungsten operating sign, undoubtedly, have been made than gation and development. While Western at white heat. Of later significance was all others combined'. Electric's chief interest was audio fre- the discovery in 1913 that the tungsten In production for the best part of 20 quency telephone repeaters, General wire containing thoria, used for lamp fil- years, this remarkable valve was not Electric concentrated on radio communi- aments, gave increased emission at only the 'workhorse of the early years of cation applications. -

The Role of the First World War in the Rise of the Electronics Industry by Frederik Nebeker

The role of the First World War in the rise of the electronics industry by Frederik Nebeker The Firyt World Mh6 sovnetinzcs called tlzc har of invention', broukht technology to the attention 4 rvr'ryotw and played a tnajor role in cstahlishing the electronics industry. It brought about mass production of clcctron tubes, esperiallyfar use in wirclcs~telqraphy and telephony, and revealed how versatile the new technology was, as dozens of new applications emerged. Because of these applicatzons, la ye numbers oj people wew tvuincd in the tcrhnologl< anti many of these people continued to work with tubes dfter the war. lectronics dorninates modern econoiiies. The electromapetically without mechanical action. production of electronics hardware is the largest The birth of the electronics industry might be branch of the inanufactliring sector, aiid all thought of as occurring in four steps: sectors of the economy make great use of electronics, especially in the form of conununications (11) Invention or discovery In the 19th century and computing. At the beginning of the twentieth physicists invented electron tubes in the course of century, however, there was no electronics industry. studying electrical discharges. World War I played a huge role in creating that industry. (b) Application. In the years around 1900 cnginecrs World War I is one of the clearest turning points in recognised that tubes could pcrform usefiil all of history. It brought four empires (Hohenzollerii, functions. Habsburg, Romanov, and Ottoman) to an cnd and (i) Technological advance. Engineers found how to created the modern map of Europe. It ternlinated the improve the performance of tubes through better colonial era. -

Historical German Contributions to Physics and Applications of Electromagnetic Oscillations and Waves

HISTORICAL GERMAN CONTRIBUTIONS TO PHYSICS AND APPLICATIONS OF ELECTROMAGNETIC OSCILLATIONS AND WAVES Manfred Thumm Forschungszentrum Karlsruhe, Association EURATOM-FZK, Institut für Hochleistungsimpuls- und Mikrowellentechnik Postfach 3640, D-76021 Karlsruhe, Germany and Universität Karlsruhe, Institut für Höchstfrequenztechnik und Elektronik, Kaiserstraße 12, D-76128 Karlsruhe, Germany Phone: ++49 7247 82 2440, Fax: ++49 7247 82 4874, E-mail: [email protected] The present review summarizes a series of the most important historical contri- butions of German scientific researchers and industrial companies in Germany to the physics and applications of electromagnetic oscillations and waves during the past 140 years and intends to point out some relations to Russian scientists. The chronology highlights the following scientists: Philipp Reis (*1834-†1874): first telephone; Hermann von Helmholtz (*1821-†1894): unification of different ap- proaches to electrodynamics; Heinrich Hertz (*1857-†1894): fundamental experi- ments on electromagnetic waves; Karl Ferdinand Braun (*1850-†1918): crystal diode, cathode ray tube, transceiver with coupled resonance circuits; Christian Hülsmeyer (*1881-†1957): rudimentary form of RADAR; Robert von Lieben (*1878-†1913): triode as amplifier in transmitter; Heinrich Barkhausen (*1881- †1956): Barkhausen-Kurz oscillations, first transit-time microwave tube; Manfred von Ardenne (*1907-†1997): first integrated vacuum tube circuits; Hans Erich Hollmann (*1899-†1961): multi-cavity magnetron, principle of reflex klystron; Oskar Heil (*1908-†1994): principle of the klystron, multi-stage depressed collector, patent of field effect transistor (FET); Walter Schottky (*1886-†1976): tetrode electron tube, theory of shot noise, Schottky effect, Schottky barrier; Herbert Kroemer (*1928): III-V semiconductor heterostructures; Jürgen Schneider (*1931): quantum electronic model of electron cyclotron resonance maser. -

International Journal of Electronics Review Article: Microwave Tube Development in Germany from 1920-1945

This article was downloaded by: [Technische Universiteit Delft] On: 21 May 2010 Access details: Access Details: [subscription number 787619779] Publisher Taylor & Francis Informa Ltd Registered in England and Wales Registered Number: 1072954 Registered office: Mortimer House, 37- 41 Mortimer Street, London W1T 3JH, UK International Journal of Electronics Publication details, including instructions for authors and subscription information: http://www.informaworld.com/smpp/title~content=t713599654 Review article: Microwave tube development in Germany from 1920-1945 H. Döring a a Institut für Hochfrequenztechnik Rheinisch Westfälische Technische Hochschule Aachen, Aachen, Federal Republic of Germany To cite this Article Döring, H.(1991) 'Review article: Microwave tube development in Germany from 1920-1945', International Journal of Electronics, 70: 5, 955 — 978 To link to this Article: DOI: 10.1080/00207219108921341 URL: http://dx.doi.org/10.1080/00207219108921341 PLEASE SCROLL DOWN FOR ARTICLE Full terms and conditions of use: http://www.informaworld.com/terms-and-conditions-of-access.pdf This article may be used for research, teaching and private study purposes. Any substantial or systematic reproduction, re-distribution, re-selling, loan or sub-licensing, systematic supply or distribution in any form to anyone is expressly forbidden. The publisher does not give any warranty express or implied or make any representation that the contents will be complete or accurate or up to date. The accuracy of any instructions, formulae and drug doses should be independently verified with primary sources. The publisher shall not be liable for any loss, actions, claims, proceedings, demand or costs or damages whatsoever or howsoever caused arising directly or indirectly in connection with or arising out of the use of this material. -

Chapter 7 Lasers

Chapter 7 Lasers After having derived the quantum mechanically correct suszeptibility for an inverted atomic system that can provide gain, we can use the two-level model to study the laser and its dynamics. After discussing the laser concept briefly we will investigate various types of gain media, gas, liquid and solid-state, that can be used to construct lasers and amplifiers. Then the dynamics of lasers, threshold behavior, steady state behavior and relaxation oscillations are discussed. A short introduction in the generation of high energy and ultrashort laser pulses using Q-switching and mode locking will be given at the end. 7.1 The Laser (Oscillator) Concept Since the invention of the vacuum amplifier tube by Robert von Lieben and Lee de Forest in 1905/06 it was known how to amplify electromagnetic waves over a broad wavelength range and how to build oscillator with which such waves could be generated. This was extended into the millimeter wave re gion with advances in amplifier tubes and later solid-state devices such as transistors. Until the 1950’s thermal radiation sources were mostly used to generate electromagnetic waves in the optical frequency range. The gener ation of coherent optical waves was only made possible by the Laser. The first amplifier based on discrete energy levels (quantum amplifier) was the MASER (Microwave Amplification by Stimulated Emission of Radiation), which was invented by Gordon, Townes and Zeiger 1954. In 1958 Schawlow and Townes proposed to extend the MASER principle to the optical regime. 293 294 CHAPTER 7. LASERS The amplification should arise from stimulated emission between discrete en ergy levels that must be inverted, as discussed in the last section. -

80 Years of Computer History Lorrin R

80 Years of Computer History Lorrin R. Garson Lifetime Learning Institute of Northern Virginia Summer 2019 Lecture 1 of 3 August 22, 2019 © 2019 Lorrin R. Garson Course Outline • Why 80 years? • Events presented chronologically • Prominent contributing individuals • A little rudimentary math • Relevant contemporaneous historical events • Often “the first” is difficult to determine • Conflicting dates are sometimes reported • My apologies for the inevitable errors! 2 Before Computers — There Were Computers active hypertext link 3 Before Computers — There Were Computers 4 Harvard’s Computers (~1919) Williamina Fleming 5 Before Computers — There Were Computers 6 Human Computers at NASA 1950s & 60s 7 8 What is a Computer? (As We Know It Today) An electronic_________ device for ____storing and ______processing data,___ typically in binary______ form, according to instructions______ given to it in a variable program _________ 9 Types of Computers • PCs • Workstations • Tablets • Servers • Smartphones • Mainframes • Hand-held • Supercomputers Calculators • Internet of Things • Minicomputers (IoT) 10 PCs • Used by individuals • $200 to $3,000 • Used for: – E-mail – “Surfing” the Web – Office automation (Word, PowerPoint, Excel, etc.) – Photo/video editing – Gaming 11 Minicomputers • Midrange machines PC < Mini < Mainframe • Multiuser • $20,000 to $100,000 • Attached to other devices – CAT scanners – X-ray refractormeters – Mass spectrometers • Replaced by workstations 12 Workstations • "Super" PCs • $5,000 to $20,000 • Individual users • Networked -

Vacuum Tube (Edited from Wikipedia)

Vacuum Tube (Edited from Wikipedia) SUMMARY In electronics, a vacuum tube, an electron tube, or just a tube (North America), or valve (Britain and some other regions) is a device that controls electric current between electrodes in an evacuated container [a glass jar with all the air removed]. Vacuum tubes mostly rely on “thermionic emission” of electrons from a hot filament or a cathode heated by the filament. This type is called a thermionic tube or thermionic valve. The simplest vacuum tube, the diode, contains a hot electron-emitting filament (cathode), and a cold plate (anode). Current can only flow in one direction through the device between the two electrodes, as electrons emitted by the cathode travel through the tube and are collected by the anode. Adding one or more control grids within the tube allows the current between the cathode and anode to be controlled by the voltage on the grid or grids. Tubes with grids can be used for many purposes, including amplification, rectification, switching, oscillation, and display. Invented in 1904 by John Ambrose Fleming, vacuum tubes were a basic component for electronics throughout the first half of the twentieth century, which saw the diffusion of radio, television, radar, sound reinforcement, sound recording and reproduction, large telephone networks, analog and digital computers, and industrial process control. Although some applications had counterparts using earlier technologies such as the spark gap transmitter or mechanical computers, it was the invention of the vacuum tube that made these technologies widespread and practical. In the 1940s the invention of semiconductor devices made it possible to produce solid-state devices, which are smaller, more efficient, more reliable, more durable, and cheaper than tubes.