Tensorflow and Onednn in Partnership

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Intel® Architecture Instruction Set Extensions and Future Features Programming Reference

Intel® Architecture Instruction Set Extensions and Future Features Programming Reference 319433-037 MAY 2019 Intel technologies features and benefits depend on system configuration and may require enabled hardware, software, or service activation. Learn more at intel.com, or from the OEM or retailer. No computer system can be absolutely secure. Intel does not assume any liability for lost or stolen data or systems or any damages resulting from such losses. You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein. No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document. The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifica- tions. Current characterized errata are available on request. This document contains information on products, services and/or processes in development. All information provided here is subject to change without notice. Intel does not guarantee the availability of these interfaces in any future product. Contact your Intel representative to obtain the latest Intel product specifications and roadmaps. Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1- 800-548-4725, or by visiting http://www.intel.com/design/literature.htm. Intel, the Intel logo, Intel Deep Learning Boost, Intel DL Boost, Intel Atom, Intel Core, Intel SpeedStep, MMX, Pentium, VTune, and Xeon are trademarks of Intel Corporation in the U.S. -

Motherboards, Processors, and Memory

220-1001 COPYRIGHTED MATERIAL c01.indd 03/23/2019 Page 1 Chapter Motherboards, Processors, and Memory THE FOLLOWING COMPTIA A+ 220-1001 OBJECTIVES ARE COVERED IN THIS CHAPTER: ✓ 3.3 Given a scenario, install RAM types. ■ RAM types ■ SODIMM ■ DDR2 ■ DDR3 ■ DDR4 ■ Single channel ■ Dual channel ■ Triple channel ■ Error correcting ■ Parity vs. non-parity ✓ 3.5 Given a scenario, install and configure motherboards, CPUs, and add-on cards. ■ Motherboard form factor ■ ATX ■ mATX ■ ITX ■ mITX ■ Motherboard connectors types ■ PCI ■ PCIe ■ Riser card ■ Socket types c01.indd 03/23/2019 Page 3 ■ SATA ■ IDE ■ Front panel connector ■ Internal USB connector ■ BIOS/UEFI settings ■ Boot options ■ Firmware upgrades ■ Security settings ■ Interface configurations ■ Security ■ Passwords ■ Drive encryption ■ TPM ■ LoJack ■ Secure boot ■ CMOS battery ■ CPU features ■ Single-core ■ Multicore ■ Virtual technology ■ Hyperthreading ■ Speeds ■ Overclocking ■ Integrated GPU ■ Compatibility ■ AMD ■ Intel ■ Cooling mechanism ■ Fans ■ Heat sink ■ Liquid ■ Thermal paste c01.indd 03/23/2019 Page 4 A personal computer (PC) is a computing device made up of many distinct electronic components that all function together in order to accomplish some useful task, such as adding up the numbers in a spreadsheet or helping you to write a letter. Note that this defi nition describes a computer as having many distinct parts that work together. Most PCs today are modular. That is, they have components that can be removed and replaced with another component of the same function but with different specifi cations in order to improve performance. Each component has a specifi c function. Much of the computing industry today is focused on smaller devices, such as laptops, tablets, and smartphones. -

Intel® Architecture Instruction Set Extensions and Future Features Programming Reference

Intel® Architecture Instruction Set Extensions and Future Features Programming Reference 319433-041 OCTOBER 2020 Intel technologies may require enabled hardware, software or service activation. No product or component can be absolutely secure. Your costs and results may vary. You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein. No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document. All product plans and roadmaps are subject to change without notice. The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request. Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade. Code names are used by Intel to identify products, technologies, or services that are in development and not publicly available. These are not “commercial” names and not intended to function as trademarks. Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be ob- tained by calling 1-800-548-4725, or by visiting http://www.intel.com/design/literature.htm. Copyright © 2020, Intel Corporation. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. -

EARNINGS Presentation Disclosures

Q2 2020 EARNINGS Presentation Disclosures This presentation contains non-GAAP financial measures. Earnings per share (EPS), gross margin, and operating margin are presented on a non- GAAP basis unless otherwise indicated, and this presentation also includes a non-GAAP free cash flow (FCF) measure. The Appendix provides a reconciliation of these measures to the most directly comparable GAAP financial measure. The non-GAAP financial measures disclosed by Intel should not be considered a substitute for, or superior to, the financial measures prepared in accordance with GAAP. Please refer to “Explanation of Non-GAAP Measures” in Intel's quarterly earnings release for a detailed explanation of the adjustments made to the comparable GAAP measures, the ways management uses the non-GAAP measures, and the reasons why management believes the non-GAAP measures provide investors with useful supplemental information. Statements in this presentation that refer to business outlook, future plans, and expectations are forward-looking statements that involve a number of risks and uncertainties. Words such as "anticipate," "expect," "intend," "goals," "plans," "believe," "seek," "estimate," "continue,“ “committed,” “on-track,” ”positioned,” “launching,” "may," "will," “would,” "should," “could,” and variations of such words and similar expressions are intended to identify such forward-looking statements. Statements that refer to or are based on estimates, forecasts, projections, uncertain events or assumptions, including statements relating to total addressable market (TAM) or market opportunity, future products and technology and the expected availability and benefits of such products and technology, including our 10nm and 7nm process technologies, products, and product designs, and anticipated trends in our businesses or the markets relevant to them, also identify forward-looking statements. -

Die Meilensteine Der Computer-, Elek

Das Poster der digitalen Evolution – Die Meilensteine der Computer-, Elektronik- und Telekommunikations-Geschichte bis 1977 1977 1978 1979 1980 1981 1982 1983 1984 1985 1986 1987 1988 1989 1990 1991 1992 1993 1994 1995 1996 1997 1998 1999 2000 2001 2002 2003 2004 2005 2006 2007 2008 2009 2010 2011 2012 2013 2014 2015 2016 2017 2018 2019 2020 und ... Von den Anfängen bis zu den Geburtswehen des PCs PC-Geburt Evolution einer neuen Industrie Business-Start PC-Etablierungsphase Benutzerfreundlichkeit wird gross geschrieben Durchbruch in der Geschäftswelt Das Zeitalter der Fensterdarstellung Online-Zeitalter Internet-Hype Wireless-Zeitalter Web 2.0/Start Cloud Computing Start des Tablet-Zeitalters AI (CC, Deep- und Machine-Learning), Internet der Dinge (IoT) und Augmented Reality (AR) Zukunftsvisionen Phasen aber A. Bowyer Cloud Wichtig Zählhilfsmittel der Frühzeit Logarithmische Rechenhilfsmittel Einzelanfertigungen von Rechenmaschinen Start der EDV Die 2. Computergeneration setzte ab 1955 auf die revolutionäre Transistor-Technik Der PC kommt Jobs mel- All-in-One- NAS-Konzept OLPC-Projekt: Dass Computer und Bausteine immer kleiner, det sich Konzepte Start der entwickelt Computing für die AI- schneller, billiger und energieoptimierter werden, Hardware Hände und Finger sind die ersten Wichtige "PC-Vorläufer" finden wir mit dem werden Massenpro- den ersten Akzeptanz: ist bekannt. Bei diesen Visionen geht es um die Symbole für die Mengendarstel- schon sehr früh bei Lernsystemen. iMac und inter- duktion des Open Source Unterstüt- möglichen zukünftigen Anwendungen, die mit 3D-Drucker zung und lung. Ägyptische Illustration des Beispiele sind: Berkley Enterprice mit neuem essant: XO-1-Laptops: neuen Technologien und Konzepte ermöglicht Veriton RepRap nicht Ersatz werden. -

Intel® Architecture Instruction Set Extensions and Future Features

Intel® Architecture Instruction Set Extensions and Future Features Programming Reference May 2021 319433-044 Intel technologies may require enabled hardware, software or service activation. No product or component can be absolutely secure. Your costs and results may vary. You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein. No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document. All product plans and roadmaps are subject to change without notice. The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request. Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade. Code names are used by Intel to identify products, technologies, or services that are in development and not publicly available. These are not “commercial” names and not intended to function as trademarks. Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be ob- tained by calling 1-800-548-4725, or by visiting http://www.intel.com/design/literature.htm. Copyright © 2021, Intel Corporation. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. -

3Rd Gen Intel Xeon Scalable Processors Press Deck

INDUSTRY INFLECTIONS ARE FUELING THE GROWTH OF DATA 5G Network Transformation, Artificial Intelligence, Intelligent Edge, Cloudification AI & ANALYTICS ARE THE DEFINING WORKLOADS OF THE NEXT DECADE UNMATCHED PORTFOLIO BREADTH AND ECOSYSTEM SUPPORT Intel delivers a silicon & software foundation designed for the diverse range of use cases from the cloud to the edge To create world-changing technology that enriches the lives of every person on earth 5G Network Artificial Intelligent Transformation Intelligence Edge Cloudification MOVE STORE PROCESS ETHERNET SILICON PHOTONICS SOFTWARE & SYSTEM LEVEL Pandemic Response Technology Initiative DIAGNOSE & TREAT RESEARCH & VACCINES LOCAL COMMUNITY International Red Cross SERVE CRITICALLY ILL COVID PATIENTS ILLUMINATE VIRUS AND SUPPORT GLOBAL THROUGH VIRTUAL CARE DNA REPLICATION TASKS RELIEF EFFORTS RAPIDLY EXPAND REMOTE ICUs SPEED DISCOVERY OF SANITIZE ROOMS AND EQUIPMENT TO 100 US HOSPITALS NEW PHARMACEUTICALS WITH AUTONOMOUS ROBOTS PREDICT PATIENTS WHO WILL DEVELOP ACCELERATE GENOMIC ANALYSIS LEARNING SOLUTION FOR STUDENTS ACUTE RESPIRATORY DISTRESS SYNDROME AND DECODE COVID-19 WITHOUT COMPUTERS OR INTERNET Ecosystem BUILD THRIVING DELIVER INNOVATE & INVEST ECOSYSTEM SOLUTIONS IN THE FUTURE Software OPTIMIZED EMPOWER UNIFY SOFTWARE DEVELOPERS APIS Hardware INFUSE AI LEADERSHIP DISCRETE OPTIMIZE AT THE INTO THE CPU ACCELERATORS PLATFORM LEVEL Intel Optane Persistent Memory 200 Series 3rd Gen Intel Gen 3 Habana Intel Xeon Scalable GPU Stratix 10 NX Intel Movidius VPU Gaudi & Goya IN DEVELOPMENT -

Intel 正式发布第三代xeon Cooper Lake

Intel Xeon Cooper Lake CPU 正式发布第三代 Intel 5 OCP Virtual Summit 2020 Intel 正如 在 月份的 上宣布的那样,在一个月后的今天, 正式 Cooper Lake” Xeon CPU 发布了代号为“ 的第三代 可扩展 。 Cedar Island CPU Cooper Lake Cascade Lake CPU 作为 平台下的唯一一款 , 即延续了 的一些 Cooper Lake CPU Socket P+ Socket CPU 特性,又增加了不少新的功能。 使用了命名为 的新 ,每个 UPI 3 6 CPU 14nm CPU 对外出的 ;<= 组增加到了 组。新 @'34 工艺制程,每个 的最大核心数仍 28 CPU TDP 205W 250W Bfloat 16 然维持在 个,但 EF 从上一代的 增加到了 ,从而提供如 这样的新 Cooper Lake CPU 4.5TB 1DPC DIMM Per 功能。 每个 可以支持的最大内存容量仍然为 ,但在 Y Channel DDR4-3200 Cooper Lake CPU Intel )模式下可以使用 内存。 也可以与 第二代奥腾持久内存 Intel Optane DC Persistent Memory Module 200 App Direct Y )配合使用,但只能用在 模式下。 Intel Cooper Lake CPU Intel Xeon CPU 在详细分析 的主要特性之前,还是让我们先来看看 E0 Roadmap Intel 2018Q3 Roadmap 14nm Cooper Lake CPU 的 。按照 在 给出的 ,基于 的 应该在 2019 2020 10nm Ice Lake CPU Intel 年推向市场,紧随其后的是在 年推出基于全新 工艺的 。但由于 Cascade Lake CPU 2019 Cooper Lake CPU 内部的各种原因, 的发布时间推迟到了 年, 也对应地延 2020 后到 年上半年发布。 2018Q3 Intel Xeon Roadmap Xeon Purley CPU 2 /4 /8 Intel 不同于第二代 !Y )用一款 覆盖 路 路 路服务器设计, 第三代 Xeon Cooper Lake CPU 4 /8 Ice Lake CPU 平台的 主要针对 路 路服务器设计,在今年底推出的 才是针 /2 2021 Eagle Stream Intel 对单路 路服务器应用。直到 年发布的 平台, 才会继续回到常规的节奏,用 Sapphire Rapids CPU 8 新一代 覆盖从单路到 路的服务器设计。 2020Q2 Intel Xeon Roadmap Intel Ice Lake CPU 38 2 ¤¥ 透露的信息,今年底将要推出的 E«¬ 个核心,这意味着 路服务 76 /152 Ice Lake CPU 8 DDR4 256GB 器系统可以提供 个核心 线程。同时, TM 个 通道,当混合配置 DDR4 DIMM 512GB Intel Optane DCPMM 200 CPU 6TB ¸ 系列内存时,单 可支持最大 内存,双路 12TB Ice Lake Intel Xeon PCIe 服务器则最多可以提供 内存。除此之外, 将会是 系列里面首款支持 Gen4 CPU 速率的 。 Cooper Lake CPU 4 112 /244 18TB 相对而言,使用 的 路服务器最多可以提供 个核心 <DÅEF CPU 4.5TB Intel Cascade Lake CPU 内存容量(单 -

Intel's Tiger Lake 11Th Gen Core I7-1185G7 Review and Deep Dive

Intel’s Tiger Lake 11th Gen Core i7-1185G7 Review and Deep Dive: Baskin’ for the Exotic by Dr. Ian Cutress & Andrei Frumusanu on September 17, 2020 Contents 1. Tiger Lake: Playing with Toe Beans 2. 10nm Superfin, Willow Cove, Xe, and new SoC 3. New Instructions and Updated Security 4. Cache Architecture: The effect of increasing L2 and L3 5. Power Consumption: Intel’s TDP Shenanigans Hurts Everyone 6. Power Consumption: Comparing 15 W TGL to 28 W TGL 7. Power Consumption: Comparing 15 W TGL to 15 W ICL to15 W Renoir 8. CPU ST Performance: SPEC 2006, SPEC 2017 9. CPU MT Performance: SPEC 2006, SPEC 2017 10. CPU Performance: Office and Web 11. CPU Performance: Simulation and Science 12. CPU Performance: Encoding and Rendering 13. Xe-LP GPU Performance: Civilization 6 14. Xe-LP GPU Performance: Deus Ex Mankind Divided 15. Xe-LP GPU Performance: Final Fantasy XIV 16. Xe-LP GPU Performance: Final Fantasy XV 17. Xe-LP GPU Performance: World of Tanks 18. Xe-LP GPU Performance: F1 2019 19. Conclusion: Is Intel Smothering AMD in Sardine Oil? The big notebook launch for Intel this year is Tiger Lake, its upcoming 10nm platform designed to pair a new graphics architecture with a nice high frequency for the performance that customers in this space require. Over the past few weeks, we’ve covered the microarchitecture as presented by Intel at its latest Intel Architecture Day 2020, as well as the formal launch of the new platform in early September. The missing piece of the puzzle was actually testing it, to see if it can match the very progressive platform currently offered by AMD’s Ryzen Mobile. -

ECE 574 – Cluster Computing Lecture 21

ECE 574 { Cluster Computing Lecture 21 Vince Weaver http://web.eece.maine.edu/~vweaver [email protected] 22 April 2021 Announcements • Projects (I'll send out presentation order) • Attend Faculty Interviews if you can • Midterms not graded yet • Reminder: no final 1 HW #7 notes • Fine grained parallelism • Running on the Pi-cluster ◦ Test with np=7, some code failed that worked with 2 9d4b6548fa8c6ff66602ef5993aca90f common seems to be not gathering in the extra lines ◦ Reading from each core rather than Bcast doesn't help anything. ◦ Some analysis of pi-cluster results Only scale up to 4. 2 cores load bcast convolve combine gather tail store total 1 1.0 0 12.8 3.8 0.1 0 3.4 21.2 2 1.0 0.1 6.4 1.9 1.8 0 2.4 13.7 4 1.0 0.3 3.2 0.9 3.0 0 2.4 10.9 8 1.0 5.6 1.7 0.5 4.6 0 2.4 15.8 16 1.0 7.3 0.7 0.2 6.5 0 2.4 18.2 32 1.0 8.0 0.3 0.1 6.4 0 2.4 18.3 64 1.0 8.8 0.1 0.06 6.9 0 2.4 19.5 3 HW #8 notes • Be careful memory copying, if copying an array of 9 ints need to copy 36 bytes (not 9) • Also, you can pass in ints as parameters (no need to allocate space and then memcpy in. Or you could, but if you do you would use points and allocate space properly) • Be sure you are using *unsigned char* for the image data, not signed char. -

Whitley-Mow-575523-Ww19-2020.Pdf

Whitley/Cedar Island Platform Message of the Week [MoW] Update Intel Corporation Data Center Platform Application Engineering WW19 2020 Document ID: 575523 Intel Confidential Legal Disclaimer Notice: This document contains information on products in the design phase of development. The information here is subject to change without notice. Do not finalize a design with this information. Intel technologies’ features and benefits depend on system configuration and may require enabled hardware, software or service activation. Learn more at Intel.com, or from the OEM or retailer. No computer system can be absolutely secure. Intel does not assume any liability for lost or stolen data or systems or any damages resulting from such losses. You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein. No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document. The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request. This document contains information on products, services and/or processes in development. All information provided here is subject to change without notice. Contact your Intel representative to obtain the latest Intel product specifications and roadmaps. Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade. -

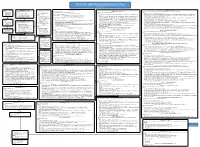

The Intel X86 Microarchitectures Map Version 3.2

The Intel x86 Microarchitectures Map Version 3.2 8086 (1978, 3 µm) 80386 (1985, 1.5 to 1 µm) P6 (1995, 0.50 to 0.35 μm) Skylake (2015, 14 nm) NetBurst (2000 , 180 to 130 nm) Series: Alternative Names: iAPX 386, 386, i386 Alternative Names: i686 Alternative Names: SKL (Desktop and Mobile), SKX (Server) (Note : all U and Y processors are MCPs) P5 (1993, 0.80 to 0.35 μm) Alternative Names: Pentium 4, Pentium IV, P4 • 16-bit data bus: Series: Series: Pentium Pro (used in desktops and servers) Series: Alternative Names: Pentium, Series: 8086 (iAPX 86) • Desktop/Server: i386DX Variant: Klamath (1997, 0.35 μm) • Desktop: Desktop 6th Generation Core i5 (i5-6xxx, S-H) 80586, 586, i586 • Desktop: Pentium 4 1.x (except those with a suffix, Willamette, 180 nm), Pentium 4 2.0 (Willamette, 180 • 8-bit data bus: • Desktop lower-performance: i386SX Alternative Names: Pentium II, PII • Desktop higher-performance: Desktop 6th Generation Core i7 (i7-6xxx, S-H), Desktop 7th Generation Core i7 X (i7-7xxxX, X), Desktop 7th Series: nm) 8088 (iAPX 88) • Mobile: i386SL, 80376, i386EX, Series: Pentium II 233/266/300 steppings C0 and C1 (Klamath, used in desktops) Generation Core i9 X (i7-7xxxXE, i7-7xxxX, X), Desktop 9th Generation Core i7 X (i7-9xxxX, X, 14 nm++?), Desktop 9th Generation Core i9 X • Desktop/Server: P5, P54C • Desktop higher-performance: Pentium 4 1.xA (Northwood, 130 nm), Pentium 4 2.x (except 2.0, 2.40A, i386CXSA, i386SXSA, i386CXSB New instructions: Deschutes (1998, 0.25 to 0.18 μm) (i7-9xxxXE, i7-9xxxX, X, 14 nm++?), Xeon W-3175X (W, 14 nm++?)