Small Soft Core up Inventory ©2019 James Brakefield Opencore and Other Soft Core Processors

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Field Programmable Gate Arrays with Hardwired Networks on Chip

Field Programmable Gate Arrays with Hardwired Networks on Chip PROEFSCHRIFT ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus prof. ir. K.C.A.M. Luyben, voorzitter van het College voor Promoties, in het openbaar te verdedigen op dinsdag 6 november 2012 om 15:00 uur door MUHAMMAD AQEEL WAHLAH Master of Science in Information Technology Pakistan Institute of Engineering and Applied Sciences (PIEAS) geboren te Lahore, Pakistan. Dit proefschrift is goedgekeurd door de promotor: Prof. dr. K.G.W. Goossens Copromotor: Dr. ir. J.S.S.M. Wong Samenstelling promotiecommissie: Rector Magnificus voorzitter Prof. dr. K.G.W. Goossens Technische Universiteit Eindhoven, promotor Dr. ir. J.S.S.M. Wong Technische Universiteit Delft, copromotor Prof. dr. S. Pillement Technical University of Nantes, France Prof. dr.-Ing. M. Hubner Ruhr-Universitat-Bochum, Germany Prof. dr. D. Stroobandt University of Gent, Belgium Prof. dr. K.L.M. Bertels Technische Universiteit Delft Prof. dr.ir. A.J. van der Veen Technische Universiteit Delft, reservelid ISBN: 978-94-6186-066-8 Keywords: Field Programmable Gate Arrays, Hardwired, Networks on Chip Copyright ⃝c 2012 Muhammad Aqeel Wahlah All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without permission of the author. Printed in The Netherlands Acknowledgments oday when I look back, I find it a very interesting journey filled with different emotions, i.e., joy and frustration, hope and despair, and T laughter and sadness. -

Debugging System for Openrisc 1000- Based Systems

Debugging System for OpenRisc 1000- based Systems Nathan Yawn [email protected] 05/12/09 Copyright (C) 2008 Nathan Yawn Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.2 or any later version published by the Free Software Foundation; with no Invariant Sections, no Front-Cover Texts, and no Back-Cover Texts. A copy of the license should be included with this document. If not, the license may be obtained from www.gnu.org, or by writing to the Free Software Foundation. This document is distributed in the hope that it will be useful, but WITHOUT ANY WARRANTY; without even the implied warranty of MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. History Rev Date Author Comments 1.0 20/7/2008 Nathan Yawn Initial version Contents 1.Introduction.............................................................................................................................................5 1.1.Overview.........................................................................................................................................5 1.2.Versions...........................................................................................................................................6 1.3.Stub-based methods.........................................................................................................................6 2.System Components................................................................................................................................7 -

Open Source Synthesis and Verification Tool for Fixed-To-Floating and Floating-To-Fixed Points Conversions

Circuits and Systems, 2016, 7, 3874-3885 http://www.scirp.org/journal/cs ISSN Online: 2153-1293 ISSN Print: 2153-1285 Open Source Synthesis and Verification Tool for Fixed-to-Floating and Floating-to-Fixed Points Conversions Semih Aslan1, Ekram Mohammad1, Azim Hassan Salamy2 1Ingram School of Engineering, Electrical Engineering Texas State University, San Marcos, Texas, USA 2School of Engineering, Electrical Engineering University of St. Thomas, St. Paul, Minnesota, USA How to cite this paper: Aslan, S., Mo- Abstract hammad, E. and Salamy, A.H. (2016) Open Source Synthesis and Verification Tool for An open source high level synthesis fixed-to-floating and floating-to-fixed conver- Fixed-to-Floating and Floating-to-Fixed Points sion tool is presented for embedded design, communication systems, and signal Conversions. Circuits and Systems, 7, 3874- processing applications. Many systems use a fixed point number system. Fixed point 3885. http://dx.doi.org/10.4236/cs.2016.711323 numbers often need to be converted to floating point numbers for higher accuracy, dynamic range, fixed-length transmission limitations or end user requirements. A Received: May 18, 2016 similar conversion system is needed to convert floating point numbers to fixed point Accepted: May 30, 2016 numbers due to the advantages that fixed point numbers offer when compared with Published: September 23, 2016 floating point number systems, such as compact hardware, reduced verification time Copyright © 2016 by authors and and design effort. The latest embedded and SoC designs use both number systems Scientific Research Publishing Inc. together to improve accuracy or reduce required hardware in the same design. -

RTEMS CPU Supplement Documentation Release 4.11.3 ©Copyright 2016, RTEMS Project (Built 15Th February 2018)

RTEMS CPU Supplement Documentation Release 4.11.3 ©Copyright 2016, RTEMS Project (built 15th February 2018) CONTENTS I RTEMS CPU Architecture Supplement1 1 Preface 5 2 Port Specific Information7 2.1 CPU Model Dependent Features...........................8 2.1.1 CPU Model Name...............................8 2.1.2 Floating Point Unit..............................8 2.2 Multilibs........................................9 2.3 Calling Conventions.................................. 10 2.3.1 Calling Mechanism.............................. 10 2.3.2 Register Usage................................. 10 2.3.3 Parameter Passing............................... 10 2.3.4 User-Provided Routines............................ 10 2.4 Memory Model..................................... 11 2.4.1 Flat Memory Model.............................. 11 2.5 Interrupt Processing.................................. 12 2.5.1 Vectoring of an Interrupt Handler...................... 12 2.5.2 Interrupt Levels................................ 12 2.5.3 Disabling of Interrupts by RTEMS...................... 12 2.6 Default Fatal Error Processing............................. 14 2.7 Symmetric Multiprocessing.............................. 15 2.8 Thread-Local Storage................................. 16 2.9 CPU counter...................................... 17 2.10 Interrupt Profiling................................... 18 2.11 Board Support Packages................................ 19 2.11.1 System Reset................................. 19 3 ARM Specific Information 21 3.1 CPU Model Dependent Features.......................... -

Xilinx Vivado Design Suite User Guide: Release Notes, Installation, And

Vivado Design Suite User Guide Release Notes, Installation, and Licensing UG973 (v2013.3) October 23, 2013 Notice of Disclaimer The information disclosed to you hereunder (the “Materials”) is provided solely for the selection and use of Xilinx products. To the maximum extent permitted by applicable law: (1) Materials are made available "AS IS" and with all faults, Xilinx hereby DISCLAIMS ALL WARRANTIES AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, NON-INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and (2) Xilinx shall not be liable (whether in contract or tort, including negligence, or under any other theory of liability) for any loss or damage of any kind or nature related to, arising under, or in connection with, the Materials (including your use of the Materials), including for any direct, indirect, special, incidental, or consequential loss or damage (including loss of data, profits, goodwill, or any type of loss or damage suffered as a result of any action brought by a third party) even if such damage or loss was reasonably foreseeable or Xilinx had been advised of the possibility of the same. Xilinx assumes no obligation to correct any errors contained in the Materials or to notify you of updates to the Materials or to product specifications. You may not reproduce, modify, distribute, or publicly display the Materials without prior written consent. Certain products are subject to the terms and conditions of the Limited Warranties which can be viewed at http://www.xilinx.com/warranty.htm; IP cores may be subject to warranty and support terms contained in a license issued to you by Xilinx. -

Openpiton: an Open Source Manycore Research Framework

OpenPiton: An Open Source Manycore Research Framework Jonathan Balkind Michael McKeown Yaosheng Fu Tri Nguyen Yanqi Zhou Alexey Lavrov Mohammad Shahrad Adi Fuchs Samuel Payne ∗ Xiaohua Liang Matthew Matl David Wentzlaff Princeton University fjbalkind,mmckeown,yfu,trin,yanqiz,alavrov,mshahrad,[email protected], [email protected], fxiaohua,mmatl,[email protected] Abstract chipset Industry is building larger, more complex, manycore proces- sors on the back of strong institutional knowledge, but aca- demic projects face difficulties in replicating that scale. To Tile alleviate these difficulties and to develop and share knowl- edge, the community needs open architecture frameworks for simulation, synthesis, and software exploration which Chip support extensibility, scalability, and configurability, along- side an established base of verification tools and supported software. In this paper we present OpenPiton, an open source framework for building scalable architecture research proto- types from 1 core to 500 million cores. OpenPiton is the world’s first open source, general-purpose, multithreaded manycore processor and framework. OpenPiton leverages the industry hardened OpenSPARC T1 core with modifica- Figure 1: OpenPiton Architecture. Multiple manycore chips tions and builds upon it with a scratch-built, scalable uncore are connected together with chipset logic and networks to creating a flexible, modern manycore design. In addition, build large scalable manycore systems. OpenPiton’s cache OpenPiton provides synthesis and backend scripts for ASIC coherence protocol extends off chip. and FPGA to enable other researchers to bring their designs to implementation. OpenPiton provides a complete verifica- tion infrastructure of over 8000 tests, is supported by mature software tools, runs full-stack multiuser Debian Linux, and has been widespread across the industry with manycore pro- is written in industry standard Verilog. -

A Pythonic Approach for Rapid Hardware Prototyping and Instrumentation

A Pythonic Approach for Rapid Hardware Prototyping and Instrumentation John Clow, Georgios Tzimpragos, Deeksha Dangwal, Sammy Guo, Joseph McMahan and Timothy Sherwood University of California, Santa Barbara, CA, 93106 USA Email: fjclow, gtzimpragos, deeksha, sguo, jmcmahan, [email protected] Abstract—We introduce PyRTL, a Python embedded hardware To achieve these goals, PyRTL intentionally restricts users design language that helps concisely and precisely describe to a set of reasonable digital design practices. PyRTL’s small digital hardware structures. Rather than attempt to infer a and well-defined internal core structure makes it easy to add good design via HLS, PyRTL provides a wrapper over a well- defined “core” set of primitives in a way that empowers digital new functionality that works across every design, including hardware design teaching and research. The proposed system logic transforms, static analysis, and optimizations. Features takes advantage of the programming language features of Python such as elaboration-through-execution (e.g. introspection), de- to allow interesting design patterns to be expressed succinctly, and sign and simulation without leaving Python, and the option encourage the rapid generation of tooling and transforms over to export to, or import from, common HDLs (Verilog-in via a custom intermediate representation. We describe PyRTL as a language, its core semantics, the transform generation interface, Yosys [1] and BLIF-in, Verilog-out) are also supported. More and explore its application to several different design patterns and information about PyRTL’s high level flow can be found in analysis tools. Also, we demonstrate the integration of PyRTL- Figure 1. generated hardware overlays into Xilinx PYNQ platform. -

IT Acronyms.Docx

List of computing and IT abbreviations /.—Slashdot 1GL—First-Generation Programming Language 1NF—First Normal Form 10B2—10BASE-2 10B5—10BASE-5 10B-F—10BASE-F 10B-FB—10BASE-FB 10B-FL—10BASE-FL 10B-FP—10BASE-FP 10B-T—10BASE-T 100B-FX—100BASE-FX 100B-T—100BASE-T 100B-TX—100BASE-TX 100BVG—100BASE-VG 286—Intel 80286 processor 2B1Q—2 Binary 1 Quaternary 2GL—Second-Generation Programming Language 2NF—Second Normal Form 3GL—Third-Generation Programming Language 3NF—Third Normal Form 386—Intel 80386 processor 1 486—Intel 80486 processor 4B5BLF—4 Byte 5 Byte Local Fiber 4GL—Fourth-Generation Programming Language 4NF—Fourth Normal Form 5GL—Fifth-Generation Programming Language 5NF—Fifth Normal Form 6NF—Sixth Normal Form 8B10BLF—8 Byte 10 Byte Local Fiber A AAT—Average Access Time AA—Anti-Aliasing AAA—Authentication Authorization, Accounting AABB—Axis Aligned Bounding Box AAC—Advanced Audio Coding AAL—ATM Adaptation Layer AALC—ATM Adaptation Layer Connection AARP—AppleTalk Address Resolution Protocol ABCL—Actor-Based Concurrent Language ABI—Application Binary Interface ABM—Asynchronous Balanced Mode ABR—Area Border Router ABR—Auto Baud-Rate detection ABR—Available Bitrate 2 ABR—Average Bitrate AC—Acoustic Coupler AC—Alternating Current ACD—Automatic Call Distributor ACE—Advanced Computing Environment ACF NCP—Advanced Communications Function—Network Control Program ACID—Atomicity Consistency Isolation Durability ACK—ACKnowledgement ACK—Amsterdam Compiler Kit ACL—Access Control List ACL—Active Current -

Latticemico8 Soft Core 8-Bit Microcontroller Optimized for Lattice Programmable Devices

O P E N S O U R C E S O F T C O R E M I C R O C ont R O LL E R LatticeMico8 Soft Core 8-Bit Microcontroller Optimized for Lattice Programmable Devices The LatticeMico8™ is an 8-bit “soft” microcontroller core for the LatticeECP™, LatticeEC™ and LatticeXP™ families of Field Programmable Gate Arrays (FPGAs), as well as the MachXO™ family of Crossover Programmable Logic Devices. Combining a full 18-bit wide instruction set with 32 general purpose registers, the LatticeMico8 is a flexible reference design suitable for a wide variety of markets, including com- munications, consumer, computer, medical, industrial, and automotive. The core consumes minimal device resources, less than 200 Look Up Tables (LUTs) in the smallest configu- ration, while maintaining a broad feature set. In order to encourage user experimentation, development and contributions, Lattice is providing a new open intellec- tual property (IP) core license, the first such license offered Key Features and Benefits by any FPGA supplier. The license applies many of the concepts of the successful open source movement to IP cores Optimized for LatticeECP, LatticeEC, LatticeXP, and MachXO Families targeted for programmable logic applications. Efficient Architecture – Utilizes <200 LUTs Broad Feature Set LatticeMico8 Block Diagram • 8-bit data path • 18-bit wide instructions • 32 general purpose registers 16 Deep Call Stack • 32 bytes of internal scratch pad memory Program Interrupt Ack • Input/Output is performed using ports (up to 256 port Address Program Flow Control & PC -

The Cortex-M Series: Hardware and Software

The Cortex-M Chapter Series: Hardware 2 and Software Introduction In this chapter the real-time DSP platform of primary focus for the course, the Cortex M4, will be introduced and explained. in terms of hardware, software, and development environments. Beginning topics include: • ARM Architectures and Processors – What is ARM Architecture – ARM Processor Families – ARM Cortex-M Series – Cortex-M4 Processor – ARM Processor vs. ARM Architectures • ARM Cortex-M4 Processor – Cortex-M4 Processor Overview – Cortex-M4 Block Diagram – Cortex-M4 Registers ECE 5655/4655 Real-Time DSP 2–1 Chapter 2 • The Cortex-M Series: Hardware and Software What is ARM Architecture • ARM architecture is a family of RISC-based processor archi- tectures – Well-known for its power efficiency; – Hence widely used in mobile devices, such as smart phones and tablets – Designed and licensed to a wide eco-system by ARM • ARM Holdings – The company designs ARM-based processors; – Does not manufacture, but licenses designs to semiconduc- tor partners who add their own Intellectual Property (IP) on top of ARM’s IP, fabricate and sell to customers; – Also offer other IP apart from processors, such as physical IPs, interconnect IPs, graphics cores, and development tools 2–2 ECE 5655/4655 Real-Time DSP ARM Processor Families ARM Processor Families • Cortex-A series (Application) Cortex-A57 Cortex-A53 – High performance processors Cortex-A15 Cortex-A9 Cortex-A Cortex-A8 capable of full Operating Sys- Cortex-A7 Cortex-A5 tem (OS) support; Cortex-R7 Cortex-R5 Cortex-R – Applications include smart- Cortex-R4 Cortex-M4 New!: Cortex-M7, Cortex-M33 phones, digital TV, smart Cortex-M3 Cortex-M1 Cortex-M Cortex-M0+ books, home gateways etc. -

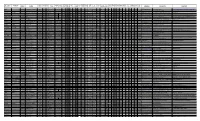

Up Cores T Est Folder Opencores Name Status Author Style / Clone

_uP_cores_t opencores style / data inst repor com LUTs blk F tool MIPS clks/ KIPS src # src tool fltg Ha max max byte # # pipe start last status author FPGA top file doc reference note worthy comments date LUT? est folder name clone size size ter ment ALUT mults ram max ver /clk inst /LUT code files chain pt vd data inst adrs inst reg len year revis cray1 alpha Christopher Fenton cray1 64 16 kintex-7-3 James Brakefield13463 6 19 10 127 ## 14.7 6.00 1.0 56.6 verilog 46 cray_sys_topyes yes Y N 4M 4M N 512 2010 CRAY data sheets homebrew Cray1 www.chrisfenton.com/homebrew-cray-1a/ fpgammix stable Tommy Thorn MMIX 64 32 arria-2 James Brakefield11605 A 8 10 94 ## q13.1 1.50 4.0 3.0 system verilog2 core yes yes Y Y 4G 4G Y 256 288 2006 2008 clone of Knuth's MMIX micro-coded s1_core S1 Core stable Fabrizio Fazzino etal SPARC 64 32 kintex-7-3 James Brakefield52845 6 8 59 56 ## v14.1 2.00 1.0 2.1 verilog 136 s1_top yes yes Y N 4G 4G Y 32 2007 2012 SPARC data sheets reduced version of OpenSPARC T1 Vivado run microblaze proprietaryXilinx uBlaze 32 32 kintex-7 Xilinx 546 6 1 320 1.03 1.0 603.7 not avail yes yes opt 4G 4G Y 86 32 3 2002 www.xilinx.com/tools/microblaze.htmMicroBlaze MCS, smallest configuration70 configuration options, MMU optional ARM_Cortex_A9 ASIC ARM ARM a9 32 16 arria V altera 4500 A 1050 2.50 1.0 583.3 asic yes yes Y 4G 4G Y 80 16 10 2012 altera data sheets uses pro-rated LC area dual issue, includes fltg-pt & MMU & caches nios2 proprietaryAltera Nios II 32 32 stratix-5 Altera 895 A 310 1.13 1.0 389.7 not avail yes yes opt 4G 4G -

FPGA Design Guide

FPGA Design Guide Lattice Semiconductor Corporation 5555 NE Moore Court Hillsboro, OR 97124 (503) 268-8000 September 16, 2008 Copyright Copyright © 2008 Lattice Semiconductor Corporation. This document may not, in whole or part, be copied, photocopied, reproduced, translated, or reduced to any electronic medium or machine- readable form without prior written consent from Lattice Semiconductor Corporation. Trademarks Lattice Semiconductor Corporation, L Lattice Semiconductor Corporation (logo), L (stylized), L (design), Lattice (design), LSC, E2CMOS, Extreme Performance, FlashBAK, flexiFlash, flexiMAC, flexiPCS, FreedomChip, GAL, GDX, Generic Array Logic, HDL Explorer, IPexpress, ISP, ispATE, ispClock, ispDOWNLOAD, ispGAL, ispGDS, ispGDX, ispGDXV, ispGDX2, ispGENERATOR, ispJTAG, ispLEVER, ispLeverCORE, ispLSI, ispMACH, ispPAC, ispTRACY, ispTURBO, ispVIRTUAL MACHINE, ispVM, ispXP, ispXPGA, ispXPLD, LatticeEC, LatticeECP, LatticeECP-DSP, LatticeECP2, LatticeECP2M, LatticeMico8, LatticeMico32, LatticeSC, LatticeSCM, LatticeXP, LatticeXP2, MACH, MachXO, MACO, ORCA, PAC, PAC-Designer, PAL, Performance Analyst, PURESPEED, Reveal, Silicon Forest, Speedlocked, Speed Locking, SuperBIG, SuperCOOL, SuperFAST, SuperWIDE, sysCLOCK, sysCONFIG, sysDSP, sysHSI, sysI/O, sysMEM, The Simple Machine for Complex Design, TransFR, UltraMOS, and specific product designations are either registered trademarks or trademarks of Lattice Semiconductor Corporation or its subsidiaries in the United States and/or other countries. ISP, Bringing the Best Together, and More