Ipug35 05.0 Table of Contents

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Configuring and Using DDR3 Memory with HP Proliant Gen8 Servers Best Practice Guidelines for Proliant Servers with Intel® Xeon® Processors

Engineering white paper, 2nd Edition Configuring and using DDR3 memory with HP ProLiant Gen8 Servers Best Practice Guidelines for ProLiant servers with Intel® Xeon® processors Table of contents Introduction 3 Overview of DDR3 memory technology 3 Basics of DDR3 memory technology 3 Basics of DIMMs 4 DDR3 DIMM types 5 HP SmartMemory 6 HP Advanced Memory Error Detection 6 ProLiant Gen8 memory architecture for servers with Intel® Xeon® E5-2600 series processors 6 Overview 6 ProLiant Gen8 servers using the Intel® Xeon® E5-2600 series processors 7 ProLiant Gen8 Intel® Xeon® E5-2600 series processors 7 ProLiant Gen8 memory architecture for servers using Intel® Xeon® E5-2400 series processors 8 Overview 8 ProLiant Gen8 servers using Intel® Xeon® E5-2400 series processors 9 ProLiant Gen8 Intel® Xeon® E5-2400 series processors 9 DDR3 DIMMs for ProLiant Gen8 servers 10 Populating memory in ProLiant Gen8 servers 11 ProLiant Gen8 memory slot configurations 11 Population rules for ProLiant Gen8 servers 11 DIMM Population Order 12 Memory system operating speeds 14 General population guidelines 14 Optimizing memory configurations 15 Optimizing for capacity 15 Optimizing for performance 15 Optimizing for lowest power consumption 20 Optimizing for Resiliency 22 Understanding unbalanced memory configurations 23 Memory configurations that are unbalanced across channels 23 Memory configurations that are unbalanced across Processors 23 BIOS Settings for memory 24 Controlling Memory Speed 24 Setting Memory Interleave 25 For more information 26 Appendix A - Sample Configurations for 2P ProLiant Gen8 servers 27 24 DIMM slot servers using Intel® Xeon® E5-2600 processor series 27 16 DIMM Slot Servers using Intel® Xeon® E5-2600 series processors 28 12 DIMM Slot Servers using Intel® Xeon® E5-2400 series processors 29 2 Introduction This paper provides an overview of the new DDR3 memory and its use in the 2 socket HP ProLiant Gen8 servers using the latest Intel® Xeon® E5-2600 series processor family. -

Non-ECC Unbuffered DIMM Non-ECC Vs

Quick Guide to DRAM for Industrial Applications 2019 by SQRAM What’s the difference between DRAM & Flash? DRAM (Dynamic Random Access Memory) and Flash are key components in PC systems, but they are different types of semiconductor products with different speeds/capacity/power-off data storage. High Small Type DRAM Flash Cache data transfer through Location close to CPU PCIe BUS Speed/Cost IC Density low high SRAM Capacity Module 32~64GB 2~8TB Capacity DRAM by ns Speed by ms (faster than flash) non-volatile memory: Power-Off volatile memory: data can be stored if NAND Flash data will lost if powered off Status powered off Low Large What are the features of DRAM? High Data Processing Speed Volatile Memory Extremely fast with low latency by RAM is a type of volatile memory. nanoseconds(10-9) access time. Much faster than It retains its data while powered on, but the data will HDD or SSD data speeds. vanish once the power is off. CPU DRAM HDD Extremely Fast Transfer Higher Capacity, Better Performance DRAM is closely connected to the CPU with short DRAM of higher capacity can process more data to access time. The system performance will drop if increase system performance. The more data data is processed directly by storage without DRAM. processed by DRAM, the less HDD processing time. What are the DDR specifications (DDR, DDR2, DDR3, DDR4)? The prefetch length of DDR SDRAM is 2 bits. On DDR2 the prefetch length is increased to 4 bits, and on DDR3 and on DDR DDR 4 it was raised to 8 bits and 16 bits respectively. -

"Low-Power Support Using Texas Instruments SN74SSTV16857 and SN74SSTV16859"

Application Report SCEA020 - February 2001 Low-Power Support Using Texas Instruments SN74SSTV16857 and SN74SSTV16859 DDR-DIMM Registers Stephen M. Nolan Standard Linear & Logic ABSTRACT The Texas Instruments SN74SSTV16857 and SN74SSTV16859 registers support the low-power mode of the DDR-DIMM. This application report explains the low-power mode and the features of the registers that support the low-power mode. Also, the considerations that the system designer must be aware of when implementing the low-power state of a registered memory module are explained. The sequence that must be followed to utilize the register properly is detailed, including the interpretation of the associated register timing specifications. Finally, the different static- and dynamic-current specifications are analyzed, along with examples of how to calculate the dynamic operating current requirement of the registers. Contents Introduction . 2 Background and Features of Registers. 5 Sequence of Entering and Exiting the Low-Power State. 6 Considerations of Register. 6 How tinact and tact Are Characterized. 9 Dynamic- and Static-Current Specifications. 9 ICC Static Standby Current. 9 ICC Static Operating Current. 10 ICCD Dynamic Operating Current – Clock Only. 10 ICCD Dynamic Operating Current – Each Data Input. 11 Calculating Power Consumption in the Application. 11 Summary . 12 Glossary . 12 List of Figures 1 SN74SSTV16857 . 3 2 SN74SSTV16859 . 4 3 Parameter Measurement Information (VDD = 2.5 V ± 0.2 V). 9 1 SCEA020 Introduction The widespread demand for more main-memory capacity and bandwidth in computer systems has lead to the development of the JEDEC standard for DDR-SDRAM-based, 184-pin, registered memory modules. These DDR DIMMs provide twice the data-bus bandwidth of previous-generation single-data-rate (SDR) memory systems. -

Double Data Rate (DDR3) SDRAM Controller IP Core User Guide

Double Data Rate (DDR3) SDRAM Controller IP Core User Guide FPGA-IPUG-02047-2.2 September 2020 Double Data Rate (DDR3) SDRAM Controller IP Core User Guide Disclaimers Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS and with all faults, and all risk associated with such information is entirely with Buyer. Buyer shall not rely on any data and performance specifications or parameters provided herein. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. No Lattice products should be used in conjunction with mission- or safety-critical or any other application in which the failure of Lattice’s product could create a situation where personal injury, death, severe property or environmental damage may occur. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice. © 2010-2020 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice. 2 FPGA-IPUG-02047-2.2 Double Data Rate (DDR3) SDRAM Controller IP Core User Guide Contents Acronyms in This Document ................................................................................................................................................ -

Memory Expert Knowledge

Memory Expert Knowledge As the density increased throughout the 1970’s and in the Memory Experts 1980’s, Japanese DRAM manufacturers, who could sell The friendly team of Memory Experts at Mr Memory higher quality modules at lower prices, overtook IBM. 9 y have on average ears experience. They are fully Traditionally DRAM modules have an asynchronous knowledgeable on all things memory. interface, which means that they respond as quickly as Have a read through just some of that knowledge... possible to changes In control inputs. What is DRAM? SDRAM History DRAM stands for Dynamic Random Access Memory. This is the memory that you use in Desktops, Laptops, Synchronous Dynamic Random Access Memory Servers and other devices. A computer stores quickly (SDRAM) is memory that is synchronised with the System accessible data in the form of 0’s and 1’s. It is dynamic Bus (which connects all the major components of a because it refreshes its capacitor charge periodically computer system). Unlike DRAM, SDRAM waits for a with new electricity, compared to the older SRAM (Static clock signal before responding to control inputs. Random Access Memory). Data is stored in the SDRAM is organised into a grid structure (Banks) with capacitors within an integrated circuit (also known as a rows (Word lines) and columns (Bit lines). Data stored is Chip). in blocks and are defined by the coordinates of the row DRAM memory is a volatile memory – which means it and column of the specific information. loses its data very quickly once the power is removed. SDRAM was universally accepted in 1993, with the This is different from NAND Flash Memory used in invention of the Samsung KM48SL2000. -

Dynamic Rams from Asynchrounos to DDR4

Dynamic RAMs From Asynchrounos to DDR4 PDF generated using the open source mwlib toolkit. See http://code.pediapress.com/ for more information. PDF generated at: Sun, 10 Feb 2013 17:59:42 UTC Contents Articles Dynamic random-access memory 1 Synchronous dynamic random-access memory 14 DDR SDRAM 27 DDR2 SDRAM 33 DDR3 SDRAM 37 DDR4 SDRAM 43 References Article Sources and Contributors 48 Image Sources, Licenses and Contributors 49 Article Licenses License 50 Dynamic random-access memory 1 Dynamic random-access memory Dynamic random-access memory (DRAM) is a type of random-access memory that stores each bit of data in a separate capacitor within an integrated circuit. The capacitor can be either charged or discharged; these two states are taken to represent the two values of a bit, conventionally called 0 and 1. Since capacitors leak charge, the information eventually fades unless the capacitor charge is refreshed periodically. Because of this refresh requirement, it is a dynamic memory as opposed to SRAM and other static memory. The main memory (the "RAM") in personal computers is dynamic RAM (DRAM). It is the RAM in laptop and workstation computers as well as some of the RAM of video game consoles. The advantage of DRAM is its structural simplicity: only one transistor and a capacitor are required per bit, compared to four or six transistors in SRAM. This allows DRAM to reach very high densities. Unlike flash memory, DRAM is volatile memory (cf. non-volatile memory), since it loses its data quickly when power is removed. The transistors and capacitors used are extremely small; billions can fit on a single memory chip. -

A+ Guide to Managing & Maintaining Your PC, 8Th Edition

A+ Guide to Managing & Maintaining Your PC, 8th Edition Chapter 5 Supporting Processors and Upgrading Memory Part II Objectives • Learn about the characteristics and purposes of Intel and AMD processors used for personal computers • Learn how to install and upgrade a processor • Learn about the different kinds of physical memory and how they work • Learn how to upgrade memory A+ Guide to Managing & Maintaining 2 Your PC, 8th Edition © Cengage Learning 2014 Memory Technologies • Random access memory (RAM) – Holds data and instructions used by CPU – Static RAM (SRAM) and dynamic RAM (DRAM) • Both volatile memory Figure 5-34 RAM on motherboards today is stored in DIMMs A+ Guide to Managing & Maintaining 3 Your PC, 8th Edition © Cengage Learning 2014 Random Access Memory • Random access: – Means that memory addresses are dynamically allocated. – Different from ROM in which memory addresses are pre-assigned to specifically coded functions. • What role does RAM play? – Provides CPU with data to process: • Keyboard entries are sent to RAM addresses. • Hard drive programs are sent to RAM addresses. • Network data (web pages) are sent to RAM addresses. • RAM is faster than other storage, such as hard drives and USB memory. • Installing more RAM is often the easiest way to improve system performance without investing in a new system. © Cengage Learning 2014 A+ Guide to Managing & Maintaining 5 Your PC, 8th Edition © Cengage Learning 2014 © Cengage Learning 2014 Memory Technologies • Variations of DRAM – DIMM – dual inline memory module – small outline -

A+ Guide to Managing and Maintaining Your PC, 7E

A+ Guide to Managing and Maintaining Your PC, 7e Chapter 7 Upgrading Memory Objectives • Learn about the different kinds of physical memory and how they work • Learn how to upgrade memory • Learn how to troubleshoot problems with memory A+ Guide to Managing and Maintaining Your PC, 7e 2 Memory Technologies • Random access memory (RAM) – Holds data and instructions used by CPU – Static RAM (SRAM) and dynamic RAM (DRAM) • Both volatile memory Figure 7-1 RAM on motherboards today is stored on DIMMs Courtesy: Course Technology/Cengage Learning A+ Guide to Managing and Maintaining Your PC, 7e 3 Memory Technologies (cont’d.) • Versions – DIMM, small outline DIMM (SO-DIMM), microDIMMs – RIMM and SIMM (outdated) • Differences among DIMM, RIMM, SIMM modules – Data path width each module accommodates – How data moves from system bus to module A+ Guide to Managing and Maintaining Your PC, 7e 4 Table 7-1 Types of memory modules Courtesy: Course Technology/Cengage Learning A+ Guide to Managing and Maintaining Your PC, 7e 5 Memory Technologies (cont’d.) • JEDEC – Standards organization • Goal of new technology – Increase overall throughput while retaining accuracy – RAM manufacturers continue to produce older RAM Figure 7-2 Timeline of memory technologies Courtesy: Course Technology/Cengage Learning A+ Guide to Managing and Maintaining Your PC, 7e 6 DIMM Technologies • DIMM (dual inline memory module) – 64-bit data path – Independent pins on opposite sides of module – Older DIMMs • Asynchronous with system bus – Synchronous DRAM (SDRAM) • Runs synchronously -

Annex L: Serial Presence Detect (SPD) for DDR4 SDRAM Modules DDR4 SPD Document Release 3 UDIMM Revision 1.1 RDIMM Revision 1.1 LRDIMM Revision 1.1 NVDIMM Revision 1.0

JEDEC Standard No. 21-C Page 4.1.2.12.3 – 1 Annex L: Serial Presence Detect (SPD) for DDR4 SDRAM Modules DDR4 SPD Document Release 3 UDIMM Revision 1.1 RDIMM Revision 1.1 LRDIMM Revision 1.1 NVDIMM Revision 1.0 1.0 Introduction This annex describes the serial presence detect (SPD) values for all DDR4 modules. The SPD data provides critical information about all modules on the memory channel and is intended to be used by the system's BIOS in order to properly initialize and optimize the system memory channels. The storage capacity of the SPD EEPROMs is limited, so a number of techniques are employed to optimize the use of these bytes, including overlays and run length limited coding. All unused entries will be coded as 0x00. All unused bits in defined bytes will be coded as 0 except where noted. Timing parameters in the SPD represent the operation of the module including all DRAMs and support devices at the lowest supported supply voltage (see SPD byte 11), and are valid from tCKAVGmin to tCKAVGmax (see SPD bytes 18 and 19). To allow for maximum flexibility as devices evolve, SPD fields described in this document may support device configuration and timing options that are not included in the JEDEC DDR4 SDRAM data sheet (JESD79-4). Please refer to DRAM supplier data sheets or JESD79-4 to determine the compatibility of components. 2.0 History Computer main memory buses have traditionally been defined by the generation of memory attached to the bus, e.g., EDO, SDRAM, DDR1, etc. -

(X72, ECC, PLL) 200-PIN DDR SDRAM SODIMM Table of Contents

1GB (x72, ECC, PLL) 200-PIN DDR SODIMM PC3200 Features Small-Outline DDR SDRAM DIMM MT18VDDT12872PH(I) – 1GB For the latest data sheet, please refer to the MicronWeb site: www.micron.com/module. Features Figure 1: 200-Pin SODIMM (MO-224) • 200-pin, small-outline, dual in-line memory Height 1.25in. (31.75mm) module (SODIMM) • Supports ECC error detection and correction • Fast data transfer rate: PC3200 • Utilizes 267 MT/s and 333 MT/s DDR SDRAM components • 1GB (128 Meg x 72, stacked) •VDD = VDDQ = +2.6V •VDDSPD = +2.3V to +3.6V • 2.5V I/O (SSTL_2 compatible) • Commands entered on each positive CK edge • DQS edge-aligned with data for READs; center- aligned with data for WRITEs Options Marking • Internal, pipelined double data rate (DDR) • Operating Temperature Range architecture; two data accesses per clock cycle Commercial (0°C T +70°C) None • Bidirectional data strobe (DQS) transmitted/re- A Industrial (-40°C T +85°C) I2 ceived with data—i.e., source-synchronous data A •Package capture 200-pin SODIMM (standard) G • Differential clock inputs CK and CK# 200-pin SODIMM (lead-free) Y • Four internal device banks for concurrent operation • Clock Frequency/CAS Latency • Programmable burst lengths: 2, 4, or 8 200 MHz (400 MT/s) CL = 31 -40B • Auto precharge option •PCB Height • Auto Refresh and Self Refresh Modes Standard 1.25in. (31.75mm) • 7.8125µs maximum average periodic refresh interval Notes: 1. CL = Device CAS (READ) Latency. • Serial Presence Detect (SPD) with EEPROM 2. Consult Micron for product availability. • Programmable READ CAS latency • Gold edge contacts pdf: 09005aef81697898/source: 09005aef8169786e Micron Technology, Inc., reserves the right to change products or specifications without notice. -

Facebook Server Intel Motherboard V3.1 Rev 1.00

Facebook Server Intel Motherboard V3.1 Rev 1.00 Author: Jia Ning, Hardware Engineer, Facebook 1 Revision History Table 1 Date Name Description 10/24/2014 Jia Ning -Version 0.70 1/6/2016 Jia Ning -Version 1.00 - Table 8-3: Add MSMI logging requirement to CATERR sensor - Table 8-3: Add Network Status Event Only Sensor - Add section 8.22 for BMC Network Status logging requirement - Table 10-8: Correct typo in description column - Section 10.11: Correct P/N from 91911-31515 to lead free version 91911-31515LF - Change "silk screen" to "silkscreen" - Correct typo of year in reversion history 1st entry - Section 11.3: remove 2 duplicate paragraph - Table 11-5: Remove PWM1 since there is no PWM1 and only PWM0 - Section 8.16 and Table 8-3 Sensor#0xE9: Update BMC SEL logging conditional around NTP related events - Table 11-5: Correct PMBus to midplane from 5V_Aux to 3.3V_AUX - Change spec name from V3.0 to V3.1 and update name in content 2 Jan 6th, 2016 Open Compute Project Intel Motherboard v3.1 © 2014 Facebook. As of Oct 24, 2014, the following persons or entities have made this Specification available under the Open Web Foundation Final Specification Agreement (OWFa 1.0), which is available at: http://www.openwebfoundation.org/legal/the-owf-1-0-agreements/owfa-1-0: Facebook, Inc. You can review the signed copies of the Open Web Foundation Agreement Version 1.0 for this Specification at http://opencompute.org/licensing/, which may also include additional parties to those listed above. -

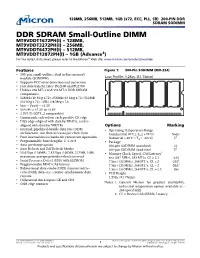

DDR SDRAM Small-Outline DIMM

128MB, 256MB, 512MB, 1GB (x72, ECC, PLL, SR) 200-PIN DDR SDRAM SODIMM DDR SDRAM Small-Outline DIMM MT9VDDT1672PH(I) – 128MB, MT9VDDT3272PH(I) – 256MB, MT9VDDT6472PH(I) – 512MB, MT9VDDT12872PH(I) – 1GB (Advance‡) For the lastest data sheet, please refer to the Micron® Web site: www.micron.com/products/modules Features Figure 1: 200-Pin SODIMM (MO-224) • 200-pin, small-outline, dual in-line memory module (SODIMM) Low Profile: 1.25in. (31.75mm) • Supports ECC error detection and correction • Fast data transfer rates: PC2100 and PC2700 • Utilizes 266 MT/s and 333 MT/s DDR SDRAM components • 128MB (16 Meg x 72); 256MB (32 Meg x 72); 512MB (64 Meg x 72); 1GB (128 Meg x 72) •VDD = VDDQ = +2.5V •VDDSPD = +2.3V to +3.6V • 2.5V I/O (SSTL_2 compatible) • Commands entered on each positive CK edge • DQS edge-aligned with data for READs; center- aligned with data for WRITEs Options Marking • Internal, pipelined double data rate (DDR) • Operating Temperature Range architecture; two data accesses per clock cycle Commercial (0°C ≤ TA ≤ +70°C) None • Four internal device banks for concurrent operation 1 Industrial (-40°C ≤ TA ≤ +85°C) I • Programmable burst lengths: 2, 4, or 8 •Package • Auto precharge option 200-pin SODIMM (standard) G • Auto Refresh and Self Refresh Modes 200-pin SODIMM (lead-free) Y1 • 15.625µs (128MB), 7.8125µs (256MB, 512MB, 1GB) • Memory Clock, Speed, CAS Latency2 maximum average periodic refresh interval 6ns (267 MHz), 333 MT/s, CL = 2.5 -335 • Serial Presence Detect (SPD) with EEPROM 7.5ns (133 MHz), 266 MT/s, CL = 2 -2621 • Programmable READ CAS latency 7.5ns (133 MHz), 266 MT/s, CL = 2 -26A1 • Bidirectional data strobe (DQS) transmitted/re- 7.5ns (133 MHz), 266 MT/s, CL = 2.5 -265 ceived with data—i.e., source-synchronous data •PCB Height capture 1.25in.