DDR SDRAM Small-Outline DIMM

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

2GB DDR3 SDRAM 72Bit SO-DIMM

Apacer Memory Product Specification 2GB DDR3 SDRAM 72bit SO-DIMM Speed Max CAS Component Number of Part Number Bandwidth Density Organization Grade Frequency Latency Composition Rank 0C 78.A2GCB.AF10C 8.5GB/sec 1066Mbps 533MHz CL7 2GB 256Mx72 256Mx8 * 9 1 Specifications z Support ECC error detection and correction z On DIMM Thermal Sensor: YES z Density:2GB z Organization – 256 word x 72 bits, 1rank z Mounting 9 pieces of 2G bits DDR3 SDRAM sealed FBGA z Package: 204-pin socket type small outline dual in line memory module (SO-DIMM) --- PCB height: 30.0mm --- Lead pitch: 0.6mm (pin) --- Lead-free (RoHS compliant) z Power supply: VDD = 1.5V + 0.075V z Eight internal banks for concurrent operation ( components) z Interface: SSTL_15 z Burst lengths (BL): 8 and 4 with Burst Chop (BC) z /CAS Latency (CL): 6,7,8,9 z /CAS Write latency (CWL): 5,6,7 z Precharge: Auto precharge option for each burst access z Refresh: Auto-refresh, self-refresh z Refresh cycles --- Average refresh period 7.8㎲ at 0℃ < TC < +85℃ 3.9㎲ at +85℃ < TC < +95℃ z Operating case temperature range --- TC = 0℃ to +95℃ z Serial presence detect (SPD) z VDDSPD = 3.0V to 3.6V Apacer Memory Product Specification Features z Double-data-rate architecture; two data transfers per clock cycle. z The high-speed data transfer is realized by the 8 bits prefetch pipelined architecture. z Bi-directional differential data strobe (DQS and /DQS) is transmitted/received with data for capturing data at the receiver. z DQS is edge-aligned with data for READs; center aligned with data for WRITEs. -

Different Types of RAM RAM RAM Stands for Random Access Memory. It Is Place Where Computer Stores Its Operating System. Applicat

Different types of RAM RAM RAM stands for Random Access Memory. It is place where computer stores its Operating System. Application Program and current data. when you refer to computer memory they mostly it mean RAM. The two main forms of modern RAM are Static RAM (SRAM) and Dynamic RAM (DRAM). DRAM memories (Dynamic Random Access Module), which are inexpensive . They are used essentially for the computer's main memory SRAM memories(Static Random Access Module), which are fast and costly. SRAM memories are used in particular for the processer's cache memory. Early memories existed in the form of chips called DIP (Dual Inline Package). Nowaday's memories generally exist in the form of modules, which are cards that can be plugged into connectors for this purpose. They are generally three types of RAM module they are 1. DIP 2. SIMM 3. DIMM 4. SDRAM 1. DIP(Dual In Line Package) Older computer systems used DIP memory directely, either soldering it to the motherboard or placing it in sockets that had been soldered to the motherboard. Most memory chips are packaged into small plastic or ceramic packages called dual inline packages or DIPs . A DIP is a rectangular package with rows of pins running along its two longer edges. These are the small black boxes you see on SIMMs, DIMMs or other larger packaging styles. However , this arrangment caused many problems. Chips inserted into sockets suffered reliability problems as the chips would (over time) tend to work their way out of the sockets. 2. SIMM A SIMM, or single in-line memory module, is a type of memory module containing random access memory used in computers from the early 1980s to the late 1990s . -

Product Guide SAMSUNG ELECTRONICS RESERVES the RIGHT to CHANGE PRODUCTS, INFORMATION and SPECIFICATIONS WITHOUT NOTICE

May. 2018 DDR4 SDRAM Memory Product Guide SAMSUNG ELECTRONICS RESERVES THE RIGHT TO CHANGE PRODUCTS, INFORMATION AND SPECIFICATIONS WITHOUT NOTICE. Products and specifications discussed herein are for reference purposes only. All information discussed herein is provided on an "AS IS" basis, without warranties of any kind. This document and all information discussed herein remain the sole and exclusive property of Samsung Electronics. No license of any patent, copyright, mask work, trademark or any other intellectual property right is granted by one party to the other party under this document, by implication, estoppel or other- wise. Samsung products are not intended for use in life support, critical care, medical, safety equipment, or similar applications where product failure could result in loss of life or personal or physical harm, or any military or defense application, or any governmental procurement to which special terms or provisions may apply. For updates or additional information about Samsung products, contact your nearest Samsung office. All brand names, trademarks and registered trademarks belong to their respective owners. © 2018 Samsung Electronics Co., Ltd. All rights reserved. - 1 - May. 2018 Product Guide DDR4 SDRAM Memory 1. DDR4 SDRAM MEMORY ORDERING INFORMATION 1 2 3 4 5 6 7 8 9 10 11 K 4 A X X X X X X X - X X X X SAMSUNG Memory Speed DRAM Temp & Power DRAM Type Package Type Density Revision Bit Organization Interface (VDD, VDDQ) # of Internal Banks 1. SAMSUNG Memory : K 8. Revision M: 1st Gen. A: 2nd Gen. 2. DRAM : 4 B: 3rd Gen. C: 4th Gen. D: 5th Gen. -

Dual-DIMM DDR2 and DDR3 SDRAM Board Design Guidelines, External

5. Dual-DIMM DDR2 and DDR3 SDRAM Board Design Guidelines June 2012 EMI_DG_005-4.1 EMI_DG_005-4.1 This chapter describes guidelines for implementing dual unbuffered DIMM (UDIMM) DDR2 and DDR3 SDRAM interfaces. This chapter discusses the impact on signal integrity of the data signal with the following conditions in a dual-DIMM configuration: ■ Populating just one slot versus populating both slots ■ Populating slot 1 versus slot 2 when only one DIMM is used ■ On-die termination (ODT) setting of 75 Ω versus an ODT setting of 150 Ω f For detailed information about a single-DIMM DDR2 SDRAM interface, refer to the DDR2 and DDR3 SDRAM Board Design Guidelines chapter. DDR2 SDRAM This section describes guidelines for implementing a dual slot unbuffered DDR2 SDRAM interface, operating at up to 400-MHz and 800-Mbps data rates. Figure 5–1 shows a typical DQS, DQ, and DM signal topology for a dual-DIMM interface configuration using the ODT feature of the DDR2 SDRAM components. Figure 5–1. Dual-DIMM DDR2 SDRAM Interface Configuration (1) VTT Ω RT = 54 DDR2 SDRAM DIMMs (Receiver) Board Trace FPGA Slot 1 Slot 2 (Driver) Board Trace Board Trace Note to Figure 5–1: (1) The parallel termination resistor RT = 54 Ω to VTT at the FPGA end of the line is optional for devices that support dynamic on-chip termination (OCT). © 2012 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. -

Configuring and Using DDR3 Memory with HP Proliant Gen8 Servers Best Practice Guidelines for Proliant Servers with Intel® Xeon® Processors

Engineering white paper, 2nd Edition Configuring and using DDR3 memory with HP ProLiant Gen8 Servers Best Practice Guidelines for ProLiant servers with Intel® Xeon® processors Table of contents Introduction 3 Overview of DDR3 memory technology 3 Basics of DDR3 memory technology 3 Basics of DIMMs 4 DDR3 DIMM types 5 HP SmartMemory 6 HP Advanced Memory Error Detection 6 ProLiant Gen8 memory architecture for servers with Intel® Xeon® E5-2600 series processors 6 Overview 6 ProLiant Gen8 servers using the Intel® Xeon® E5-2600 series processors 7 ProLiant Gen8 Intel® Xeon® E5-2600 series processors 7 ProLiant Gen8 memory architecture for servers using Intel® Xeon® E5-2400 series processors 8 Overview 8 ProLiant Gen8 servers using Intel® Xeon® E5-2400 series processors 9 ProLiant Gen8 Intel® Xeon® E5-2400 series processors 9 DDR3 DIMMs for ProLiant Gen8 servers 10 Populating memory in ProLiant Gen8 servers 11 ProLiant Gen8 memory slot configurations 11 Population rules for ProLiant Gen8 servers 11 DIMM Population Order 12 Memory system operating speeds 14 General population guidelines 14 Optimizing memory configurations 15 Optimizing for capacity 15 Optimizing for performance 15 Optimizing for lowest power consumption 20 Optimizing for Resiliency 22 Understanding unbalanced memory configurations 23 Memory configurations that are unbalanced across channels 23 Memory configurations that are unbalanced across Processors 23 BIOS Settings for memory 24 Controlling Memory Speed 24 Setting Memory Interleave 25 For more information 26 Appendix A - Sample Configurations for 2P ProLiant Gen8 servers 27 24 DIMM slot servers using Intel® Xeon® E5-2600 processor series 27 16 DIMM Slot Servers using Intel® Xeon® E5-2600 series processors 28 12 DIMM Slot Servers using Intel® Xeon® E5-2400 series processors 29 2 Introduction This paper provides an overview of the new DDR3 memory and its use in the 2 socket HP ProLiant Gen8 servers using the latest Intel® Xeon® E5-2600 series processor family. -

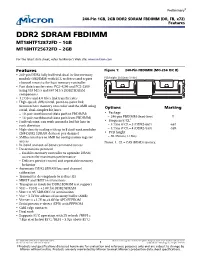

DDR2 SDRAM FBDIMM (DR, FB, X72) Features DDR2 SDRAM FBDIMM MT18HTF12872FD – 1GB MT18HTF25672FD – 2GB

Preliminary‡ 240-Pin 1GB, 2GB DDR2 SDRAM FBDIMM (DR, FB, x72) Features DDR2 SDRAM FBDIMM MT18HTF12872FD – 1GB MT18HTF25672FD – 2GB For the latest data sheet, refer to Micron’s Web site: www.micron.com Features Figure 1: 240-Pin FBDIMM (MO-256 R/C B) • 240-pin DDR2 fully buffered, dual in-line memory module (FBDIMM) with ECC to detect and report PCB height: 30.35mm (1.19in) channel errors to the host memory controller • Fast data transfer rates: PC2-4200 and PC2-5300 using 533 MT/s and 667 MT/s DDR2 SDRAM components • 3.2 Gb/s and 4.0 Gb/s link transfer rates • High-speed, differential, point-to-point link between host memory controller and the AMB using Options Marking serial, dual-simplex bit lanes – 10-pair southbound (data path to FBDIMM) •Package – 240-pin FBDIMM (lead-free) Y – 14-pair northbound (data path from FBDIMM) 1 • Fault tolerant; can work around a bad bit lane in •Frequency/CL each direction – 3.75ns @ CL = 5 (DDR2-667) -667 • High-density scaling with up to 8 dual-rank modules – 3.75ns @ CL = 4 (DDR2-533) -53E (288 DDR2 SDRAM devices) per channel •PCB height • SMBus interface to AMB for configuration register – 30.35mm (1.19in) access Notes: 1. CL = CAS (READ) latency. • In-band and out-of-band command access • Deterministic protocol – Enables memory controller to optimize DRAM accesses for maximum performance – Delivers precise control and repeatable memory behavior •Automatic DDR2 SDRAM bus and channel calibration • Transmitter de-emphasis to reduce ISI • MBIST and IBIST test functions • Transparent mode for DDR2 SDRAM test support •VDD = VDDQ = +1.8V for DDR2 SDRAM •VREF = 0 .9V SDRAM C/A termination •VCC = 1.5V for advanced memory buffer (AMB) •VDDSPD = +1.7V to +3.6V for SPD EEPROM • Serial presence-detect (SPD) with EEPROM • Gold edge contacts •Dual rank • Supports 95°C operation with 2X refresh (tREFI = 7.8µs at or below 85°C; tREFI = 3.9µs above 85°C) PDF: 09005aef81a2f20c/Source: 09005aef81a2f25b Micron Technology, Inc., reserves the right to change products or specifications without notice. -

Non-ECC Unbuffered DIMM Non-ECC Vs

Quick Guide to DRAM for Industrial Applications 2019 by SQRAM What’s the difference between DRAM & Flash? DRAM (Dynamic Random Access Memory) and Flash are key components in PC systems, but they are different types of semiconductor products with different speeds/capacity/power-off data storage. High Small Type DRAM Flash Cache data transfer through Location close to CPU PCIe BUS Speed/Cost IC Density low high SRAM Capacity Module 32~64GB 2~8TB Capacity DRAM by ns Speed by ms (faster than flash) non-volatile memory: Power-Off volatile memory: data can be stored if NAND Flash data will lost if powered off Status powered off Low Large What are the features of DRAM? High Data Processing Speed Volatile Memory Extremely fast with low latency by RAM is a type of volatile memory. nanoseconds(10-9) access time. Much faster than It retains its data while powered on, but the data will HDD or SSD data speeds. vanish once the power is off. CPU DRAM HDD Extremely Fast Transfer Higher Capacity, Better Performance DRAM is closely connected to the CPU with short DRAM of higher capacity can process more data to access time. The system performance will drop if increase system performance. The more data data is processed directly by storage without DRAM. processed by DRAM, the less HDD processing time. What are the DDR specifications (DDR, DDR2, DDR3, DDR4)? The prefetch length of DDR SDRAM is 2 bits. On DDR2 the prefetch length is increased to 4 bits, and on DDR3 and on DDR DDR 4 it was raised to 8 bits and 16 bits respectively. -

Intel® NUC Products NUC7CJY/NUC7PJY Technical Product Specification

Intel® NUC Products NUC7CJY/NUC7PJY Technical Product Specification Regulatory Models: NUC7JY (Kit/Mini PC) NUC7JYB (Board) February 2018 Order Number: J96982-002 Intel NUC Products NUC7CJY/NUC7PJY Technical Product Specification The Intel NUC Products NUC7CJY/NUC7PJY may contain design defects or errors known as errata that may cause the product to deviate from published specifications. Current characterized errata are documented in the Intel NUC Products NUC7CJY/NUC7PJY Specification Update. ii Revision History Revision Revision History Date 001 First release of Intel NUC Products NUC7CJY/NUC7PJY Technical Product January 2018 Specification 002 Spec Change February 2018 Disclaimer This product specification applies to only the standard Intel® NUC Boards, Kits and Mini PCs with BIOS identifier JYGLKCPX.86A. INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL’S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. UNLESS OTHERWISE AGREED IN WRITING BY INTEL, THE INTEL PRODUCTS ARE NOT DESIGNED NOR INTENDED FOR ANY APPLICATION IN WHICH THE FAILURE OF THE INTEL PRODUCT COULD CREATE A SITUATION WHERE PERSONAL INJURY OR DEATH MAY OCCUR. All Intel® NUC Boards are evaluated as Information Technology Equipment (I.T.E.) for use in personal computers (PC) for installation in homes, offices, schools, computer rooms, and similar locations. -

ECE 571 – Advanced Microprocessor-Based Design Lecture 16

ECE 571 { Advanced Microprocessor-Based Design Lecture 16 Vince Weaver http://web.eece.maine.edu/~vweaver [email protected] 4 April 2017 Announcements • HW8 was assigned, read about Newer Intel chips for Thursday • Slow getting back to you about project ideas • Sorry about voice, mild cold 1 How to save Energy in TLB? • Turn off Virtual Memory completely (aside about ARM1176 manual and caches). Can you run Linux without VM? ucLinux • TLB is similar to cache, can make similar optimizations (drowsy, sizing, etc) • Assume in current page (i.e. 1-entry 0-level TLB) (Kadayif, Sivasubramaniam, Kandemir, Kandiraju, Chen. TODAES 2005). 2 (Kadayif,Sivasubramaniam, Kandemir, Kandiraju, Chen. Micro 2002) • Use virtual cache (Ekman and Stenstr¨om,ISLPED 2002) • Switch virtual to physical cache on fly (hybrid) (Basu, Hill, Swift. ISCA 2012) • Dynamically resize the TLB (Delaluz, Kandemir, Sivasubramaniam, Irwin, Vijaykrishnan. ICCD 2013) • Try to keep as much in one page as possible via compiler. (Jeyapaul, Marathe, Shrivastava, VLSI'09) 3 (Lee, Ballapuram. ISLPED'03) 4 DRAM • Single transistor/capacitor pair. (can improve behavior with more transistors, but then less dense) • Compare to SRAM that has 6 transistors (or 4 plus hard-to make resistors with high static power) • In 90nm process, 30fF capacitor, leakage in transistor 1fA. Can hold charge from milliseconds to seconds. • DRAMs gradually lose charge, need to be refreshed. Need to be conservative. Refresh every 32 or 64ms 5 • DRAM read is destructive, always have to write back 6 Diagram DRAM Column Decoder Sense Amps word line bit line Memory Array Row Decoder SRAM WL WL !BL BL !BL BL 7 Low Level • Trench Capacitors • Stacked Capacitors 8 SIMMs/DIMMS • How many chips on DIMM? 8? 9? 9 usually means ECC/parity • Chips x1 x4 x8 bits, how many get output at a time. -

DDR3 SODIMM Product Datasheet

DDR3 SODIMM Product Datasheet 廣 穎 電 通 股 份 有 限 公 司 Silicon Power Computer & Communications Inc. TEL: 886-2 8797-8833 FAX: 886-2 8751-6595 台北市114內湖區洲子街106號7樓 7F, No.106, ZHO-Z ST. NEIHU DIST, 114, TAIPEI, TAIWAN, R.O.C This document is a general product description and is subject to change without notice DDR3 SODIMM Product Datasheet Index Index...................................................................................................................................................................... 2 Revision History ................................................................................................................................................ 3 Description .......................................................................................................................................................... 4 Features ............................................................................................................................................................... 5 Pin Assignments................................................................................................................................................ 7 Pin Description................................................................................................................................................... 8 Environmental Requirements......................................................................................................................... 9 Absolute Maximum DC Ratings.................................................................................................................... -

"Low-Power Support Using Texas Instruments SN74SSTV16857 and SN74SSTV16859"

Application Report SCEA020 - February 2001 Low-Power Support Using Texas Instruments SN74SSTV16857 and SN74SSTV16859 DDR-DIMM Registers Stephen M. Nolan Standard Linear & Logic ABSTRACT The Texas Instruments SN74SSTV16857 and SN74SSTV16859 registers support the low-power mode of the DDR-DIMM. This application report explains the low-power mode and the features of the registers that support the low-power mode. Also, the considerations that the system designer must be aware of when implementing the low-power state of a registered memory module are explained. The sequence that must be followed to utilize the register properly is detailed, including the interpretation of the associated register timing specifications. Finally, the different static- and dynamic-current specifications are analyzed, along with examples of how to calculate the dynamic operating current requirement of the registers. Contents Introduction . 2 Background and Features of Registers. 5 Sequence of Entering and Exiting the Low-Power State. 6 Considerations of Register. 6 How tinact and tact Are Characterized. 9 Dynamic- and Static-Current Specifications. 9 ICC Static Standby Current. 9 ICC Static Operating Current. 10 ICCD Dynamic Operating Current – Clock Only. 10 ICCD Dynamic Operating Current – Each Data Input. 11 Calculating Power Consumption in the Application. 11 Summary . 12 Glossary . 12 List of Figures 1 SN74SSTV16857 . 3 2 SN74SSTV16859 . 4 3 Parameter Measurement Information (VDD = 2.5 V ± 0.2 V). 9 1 SCEA020 Introduction The widespread demand for more main-memory capacity and bandwidth in computer systems has lead to the development of the JEDEC standard for DDR-SDRAM-based, 184-pin, registered memory modules. These DDR DIMMs provide twice the data-bus bandwidth of previous-generation single-data-rate (SDR) memory systems. -

DDR4 2400 R-DIMM / VLP R-DIMM / ECC U-DIMM / ECC SO-DIMM Features

DDR4 2400 R-DIMM / VLP R-DIMM / ECC U-DIMM / ECC SO-DIMM Available in densities ranging from 4GB to 16GB per module and clocked up to 2400MHz for a maximum 17GB/s bandwidth, ADATA DDR4 server memory modules are all certified Intel® Haswell-EP compatible to ensure superior performance. Products ship in four convenient form factors to accommodate diverse needs and applications: R-DIMM and ECC U-DIMM for servers and enterprises, VLP R-DIMM for high-end blade servers, and ECC SO-SIMM for micro servers. Running at a mere 1.2V, ADATA DDR4 memory modules use 20% less energy than conventional lower-performance DDR3 modules, in effect delivering more computational power for less energy draw. ADATA DDR4 server memory modules are an excellent choice for users looking to balance performance, environmental responsibility, and cost effectiveness. Features ECC U-DIMM High speed up to 2400MHz Transfer bandwidths up to 17GB/s Energy efficient: save up to 20% compared to DDR3 8-layer PCB provides improved signal transfer R-DIMM and system stability PCB gold plating: 30u and up Intel Haswell-EP compatible for extreme performance VLP R-DIMM ECC SO-DIMM Specifications Type ECC-DIMM R-DIMM VLP R-DIMM ECC SO-DIMM Standard Standard Very low profile Standard Form factor (1.18" height) (1.18" height) (0.7" height) (1.18" height) Enterprise servers / Enterprise servers / Suitable for Blade servers Micro servers data centers data centers Interface 288-pin 288-pin 288-pin 260-pin Capacity 4GB / 8GB / 16GB 4GB / 8GB / 16GB 4GB / 8GB /16GB 4GB / 8GB / 16GB Rank