Lect 1617 P.Pptx

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Engineering Transcriptional Control and Synthetic Gene Circuits in Cell Free Systems

University of Tennessee, Knoxville TRACE: Tennessee Research and Creative Exchange Doctoral Dissertations Graduate School 12-2012 Engineering Transcriptional Control and Synthetic Gene Circuits in Cell Free systems Sukanya Iyer University of Tennessee, [email protected] Follow this and additional works at: https://trace.tennessee.edu/utk_graddiss Part of the Biotechnology Commons Recommended Citation Iyer, Sukanya, "Engineering Transcriptional Control and Synthetic Gene Circuits in Cell Free systems. " PhD diss., University of Tennessee, 2012. https://trace.tennessee.edu/utk_graddiss/1586 This Dissertation is brought to you for free and open access by the Graduate School at TRACE: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of TRACE: Tennessee Research and Creative Exchange. For more information, please contact [email protected]. To the Graduate Council: I am submitting herewith a dissertation written by Sukanya Iyer entitled "Engineering Transcriptional Control and Synthetic Gene Circuits in Cell Free systems." I have examined the final electronic copy of this dissertation for form and content and recommend that it be accepted in partial fulfillment of the equirr ements for the degree of Doctor of Philosophy, with a major in Life Sciences. Mitchel J. Doktycz, Major Professor We have read this dissertation and recommend its acceptance: Michael L. Simpson, Albrecht G. von Arnim, Barry D. Bruce, Jennifer L. Morrell-Falvey Accepted for the Council: Carolyn R. Hodges Vice Provost and Dean of the Graduate School (Original signatures are on file with official studentecor r ds.) Engineering Transcriptional Control and Synthetic Gene Circuits in Cell Free systems A Dissertation Presented for the Doctor of Philosophy Degree The University of Tennessee, Knoxville Sukanya Iyer December 2012 Copyright © 2012 by Sukanya Iyer. -

CSE Yet, Please Do Well! Logical Connectives

administrivia Course web: http://www.cs.washington.edu/311 Office hours: 12 office hours each week Me/James: MW 10:30-11:30/2:30-3:30pm or by appointment TA Section: Start next week Call me: Shayan Don’t: Actually call me. Homework #1: Will be posted today, due next Friday by midnight (Oct 9th) Gradescope! (stay tuned) Extra credit: Not required to get a 4.0. Counts separately. In total, may raise grade by ~0.1 Don’t be shy (raise your hand in the back)! Do space out your participation. If you are not CSE yet, please do well! logical connectives p q p q p p T T T T F T F F F T F T F NOT F F F AND p q p q p q p q T T T T T F T F T T F T F T T F T T F F F F F F OR XOR 푝 → 푞 • “If p, then q” is a promise: p q p q F F T • Whenever p is true, then q is true F T T • Ask “has the promise been broken” T F F T T T If it’s raining, then I have my umbrella. related implications • Implication: p q • Converse: q p • Contrapositive: q p • Inverse: p q How do these relate to each other? How to see this? 푝 ↔ 푞 • p iff q • p is equivalent to q • p implies q and q implies p p q p q Let’s think about fruits A fruit is an apple only if it is either red or green and a fruit is not red and green. -

Digital IC Listing

BELS Digital IC Report Package BELS Unit PartName Type Location ID # Price Type CMOS 74HC00, Quad 2-Input NAND Gate DIP-14 3 - A 500 0.24 74HCT00, Quad 2-Input NAND Gate DIP-14 3 - A 501 0.36 74HC02, Quad 2 Input NOR DIP-14 3 - A 417 0.24 74HC04, Hex Inverter, buffered DIP-14 3 - A 418 0.24 74HC04, Hex Inverter (buffered) DIP-14 3 - A 511 0.24 74HCT04, Hex Inverter (Open Collector) DIP-14 3 - A 512 0.36 74HC08, Quad 2 Input AND Gate DIP-14 3 - A 408 0.24 74HC10, Triple 3-Input NAND DIP-14 3 - A 419 0.31 74HC32, Quad OR DIP-14 3 - B 409 0.24 74HC32, Quad 2-Input OR Gates DIP-14 3 - B 543 0.24 74HC138, 3-line to 8-line decoder / demultiplexer DIP-16 3 - C 603 1.05 74HCT139, Dual 2-line to 4-line decoders / demultiplexers DIP-16 3 - C 605 0.86 74HC154, 4-16 line decoder/demulitplexer, 0.3 wide DIP - Small none 445 1.49 74HC154W, 4-16 line decoder/demultiplexer, 0.6wide DIP none 446 1.86 74HC190, Synchronous 4-Bit Up/Down Decade and Binary Counters DIP-16 3 - D 637 74HCT240, Octal Buffers and Line Drivers w/ 3-State outputs DIP-20 3 - D 643 1.04 74HC244, Octal Buffers And Line Drivers w/ 3-State outputs DIP-20 3 - D 647 1.43 74HCT245, Octal Bus Transceivers w/ 3-State outputs DIP-20 3 - D 649 1.13 74HCT273, Octal D-Type Flip-Flops w/ Clear DIP-20 3 - D 658 1.35 74HCT373, Octal Transparent D-Type Latches w/ 3-State outputs DIP-20 3 - E 666 1.35 74HCT377, Octal D-Type Flip-Flops w/ Clock Enable DIP-20 3 - E 669 1.50 74HCT573, Octal Transparent D-Type Latches w/ 3-State outputs DIP-20 3 - E 674 0.88 Type CMOS CD4000 Series CD4001, Quad 2-input -

The Equation for the 3-Input XOR Gate Is Derived As Follows

The equation for the 3-input XOR gate is derived as follows The last four product terms in the above derivation are the four 1-minterms in the 3-input XOR truth table. For 3 or more inputs, the XOR gate has a value of 1when there is an odd number of 1’s in the inputs, otherwise, it is a 0. Notice also that the truth tables for the 3-input XOR and XNOR gates are identical. It turns out that for an even number of inputs, XOR is the inverse of XNOR, but for an odd number of inputs, XOR is equal to XNOR. All these gates can be interconnected together to form large complex circuits which we call networks. These networks can be described graphically using circuit diagrams, with Boolean expressions or with truth tables. 3.2 Describing Logic Circuits Algebraically Any logic circuit, no matter how complex, may be completely described using the Boolean operations previously defined, because of the OR gate, AND gate, and NOT circuit are the basic building blocks of digital systems. For example consider the circuit shown in Figure 1.3(c). The circuit has three inputs, A, B, and C, and a single output, x. Utilizing the Boolean expression for each gate, we can easily determine the expression for the output. The expression for the AND gate output is written A B. This AND output is connected as an input to the OR gate along with C, another input. The OR gate operates on its inputs such that its output is the OR sum of the inputs. -

Hardware Abstract the Logic Gates References Results Transistors Through the Years Acknowledgements

The Practical Applications of Logic Gates in Computer Science Courses Presenters: Arash Mahmoudian, Ashley Moser Sponsored by Prof. Heda Samimi ABSTRACT THE LOGIC GATES Logic gates are binary operators used to simulate electronic gates for design of circuits virtually before building them with-real components. These gates are used as an instrumental foundation for digital computers; They help the user control a computer or similar device by controlling the decision making for the hardware. A gate takes in OR GATE AND GATE NOT GATE an input, then it produces an algorithm as to how The OR gate is a logic gate with at least two An AND gate is a consists of at least two A NOT gate, also known as an inverter, has to handle the output. This process prevents the inputs and only one output that performs what inputs and one output that performs what is just a single input with rather simple behavior. user from having to include a microprocessor for is known as logical disjunction, meaning that known as logical conjunction, meaning that A NOT gate performs what is known as logical negation, which means that if its input is true, decision this making. Six of the logic gates used the output of this gate is true when any of its the output of this gate is false if one or more of inputs are true. If all the inputs are false, the an AND gate's inputs are false. Otherwise, if then the output will be false. Likewise, are: the OR gate, AND gate, NOT gate, XOR gate, output of the gate will also be false. -

Solving Logic Problems with a Twist

Transformations Volume 6 Issue 1 Winter 2020 Article 6 11-30-2020 Solving Logic Problems with a Twist Angie Su Nova Southeastern University, [email protected] Bhagi Phuel Chloe Johnson Dylan Mandolini Shawlyn Fleming Follow this and additional works at: https://nsuworks.nova.edu/transformations Part of the Science and Mathematics Education Commons, and the Teacher Education and Professional Development Commons Recommended Citation Su, Angie; Bhagi Phuel; Chloe Johnson; Dylan Mandolini; and Shawlyn Fleming (2020) "Solving Logic Problems with a Twist," Transformations: Vol. 6 : Iss. 1 , Article 6. Available at: https://nsuworks.nova.edu/transformations/vol6/iss1/6 This Article is brought to you for free and open access by the Abraham S. Fischler College of Education at NSUWorks. It has been accepted for inclusion in Transformations by an authorized editor of NSUWorks. For more information, please contact [email protected]. Solving Logic Problems with a Twist Cover Page Footnote This article was originally published in the Dimensions Journal, A publication of the Florida Council of Teachers of Mathematics Journal. This article is available in Transformations: https://nsuworks.nova.edu/transformations/vol6/iss1/6 Su, Hui Fang Huang, Bhagi Phuel, Chloe Johnson, Dylan Mandolini, and Shawlyn Fleming Solving Logic Problems with a Twist Solving Logic Problems with a Twist Hui Fang Huang Su, Bhagi Phuel, Chloe Johnson, Dylan Mandolini, and Shawlyn Fleming Review of Symbolic Logic Aristotle, Greek philosopher and scientist, was a pupil of Plato and asserted that any logical argument is reducible to two premises and a conclusion (Gullberg, 1997). According to classical (Aristotelian) logic, arguments are governed by three fundamental laws: the principle of identity, the principle of the excluded middle, and the principle of contradiction. -

Designing Combinational Logic Gates in Cmos

CHAPTER 6 DESIGNING COMBINATIONAL LOGIC GATES IN CMOS In-depth discussion of logic families in CMOS—static and dynamic, pass-transistor, nonra- tioed and ratioed logic n Optimizing a logic gate for area, speed, energy, or robustness n Low-power and high-performance circuit-design techniques 6.1 Introduction 6.3.2 Speed and Power Dissipation of Dynamic Logic 6.2 Static CMOS Design 6.3.3 Issues in Dynamic Design 6.2.1 Complementary CMOS 6.3.4 Cascading Dynamic Gates 6.5 Leakage in Low Voltage Systems 6.2.2 Ratioed Logic 6.4 Perspective: How to Choose a Logic Style 6.2.3 Pass-Transistor Logic 6.6 Summary 6.3 Dynamic CMOS Design 6.7 To Probe Further 6.3.1 Dynamic Logic: Basic Principles 6.8 Exercises and Design Problems 197 198 DESIGNING COMBINATIONAL LOGIC GATES IN CMOS Chapter 6 6.1Introduction The design considerations for a simple inverter circuit were presented in the previous chapter. In this chapter, the design of the inverter will be extended to address the synthesis of arbitrary digital gates such as NOR, NAND and XOR. The focus will be on combina- tional logic (or non-regenerative) circuits that have the property that at any point in time, the output of the circuit is related to its current input signals by some Boolean expression (assuming that the transients through the logic gates have settled). No intentional connec- tion between outputs and inputs is present. In another class of circuits, known as sequential or regenerative circuits —to be dis- cussed in a later chapter—, the output is not only a function of the current input data, but also of previous values of the input signals (Figure 6.1). -

8-Bit Adder and Subtractor with Domain Label Based on DNA Strand Displacement

Article 8-Bit Adder and Subtractor with Domain Label Based on DNA Strand Displacement Weixuan Han 1,2 and Changjun Zhou 1,3,* 1 College of Mathematics and Computer Science, Zhejiang Normal University, Jinhua 321004, China; [email protected] 2 College of Nuclear Science and Engineering, Sanmen Institute of technicians, Sanmen 317100, China 3 Key Laboratory of Advanced Design and Intelligent Computing (Dalian University) Ministry of Education, Dalian 116622, China * Correspondence: [email protected] Academic Editor: Xiangxiang Zeng Received: 16 October 2018; Accepted: 13 November 2018; Published: 15 November 2018 Abstract: DNA strand displacement, which plays a fundamental role in DNA computing, has been widely applied to many biological computing problems, including biological logic circuits. However, there are many biological cascade logic circuits with domain labels based on DNA strand displacement that have not yet been designed. Thus, in this paper, cascade 8-bit adder/subtractor with a domain label is designed based on DNA strand displacement; domain t and domain f represent signal 1 and signal 0, respectively, instead of domain t and domain f are applied to representing signal 1 and signal 0 respectively instead of high concentration and low concentration high concentration and low concentration. Basic logic gates, an amplification gate, a fan-out gate and a reporter gate are correspondingly reconstructed as domain label gates. The simulation results of Visual DSD show the feasibility and accuracy of the logic calculation model of the adder/subtractor designed in this paper. It is a useful exploration that may expand the application of the molecular logic circuit. Keywords: DNA strand displacement; cascade; 8-bit adder/subtractor; domain label 1. -

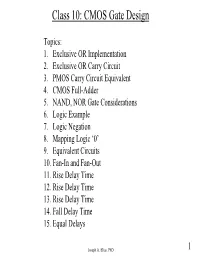

Class 10: CMOS Gate Design

Class 10: CMOS Gate Design Topics: 1. Exclusive OR Implementation 2. Exclusive OR Carry Circuit 3. PMOS Carry Circuit Equivalent 4. CMOS Full-Adder 5. NAND, NOR Gate Considerations 6. Logic Example 7. Logic Negation 8. Mapping Logic ‘0’ 9. Equivalent Circuits 10. Fan-In and Fan-Out 11. Rise Delay Time 12. Rise Delay Time 13. Rise Delay Time 14. Fall Delay Time 15. Equal Delays Joseph A. Elias, PhD 1 Class 10: CMOS Gate Design Exclusive OR Design (Martin c4.5) 3-input XOR Truth Table Similar to how one derives a 2-input XOR (Martin, p.183) using (a’+b’)=(ab)’ (a’b’)=(a+b)’ a XOR b = a’b + ab’ = a’a + a’b + ab’ + bb’ = a’(a+b) + b’(a+b) = (a’+b’)(a+b) = (ab)’(a+b) = (ab + (a’b’) )’ = (ab + (a + b)’ )’ Joseph A. Elias, PhD 2 Class 10: CMOS Gate Design Exclusive OR Carry Circuit (Martin c4.5) NMOS realization PMOS equivalent •A in parallel with B •A in series with B •A||B in series with C •AB in parallel with C •AB in parallel with (A||B)C •A||B in series with (AB)||C Vout = Joseph A. Elias, PhD 3 Class 10: CMOS Gate Design PMOS Carry Circuit Equivalent (Martin c4.5) •Martin indicates equivalency between these circuits •Is this true? (AB+C)(A+B) = (A+B)C + (AB) ABA + ABB + AC + BC = AC +BC +AB AB + AB + AC + BC = AC + BC + AB AB + AC + BC = AB + AC + BC equivalent Joseph A. Elias, PhD 4 Class 10: CMOS Gate Design CMOS Full-Adder (Martin c4.5) Sum: (A+B+C) Carry + ABC Carry: (A+B)C + AB Joseph A. -

–Not –And –Or –Xor –Nand –Nor

Gates Six types of gates –NOT –AND –OR –XOR –NAND –NOR 1 NOT Gate A NOT gate accepts one input signal (0 or 1) and returns the complementary (opposite) signal as output 2 AND Gate An AND gate accepts two input signals If both are 1, the output is 1; otherwise, the output is 0 3 OR Gate An OR gate accepts two input signals If both are 0, the output is 0; otherwise, the output is 1 4 XOR Gate An XOR gate accepts two input signals If both are the same, the output is 0; otherwise, the output is 1 5 XOR Gate Note the difference between the XOR gate and the OR gate; they differ only in one input situation When both input signals are 1, the OR gate produces a 1 and the XOR produces a 0 XOR is called the exclusive OR because its output is 1 if (and only if): • either one input or the other is 1, • excluding the case that they both are 6 NAND Gate The NAND (“NOT of AND”) gate accepts two input signals If both are 1, the output is 0; otherwise, the output is 1 NOR Gate The NOR (“NOT of OR”) gate accepts two inputs If both are 0, the output is 1; otherwise, the output is 0 8 AND OR XOR NAND NOR 9 Review of Gate Processing Gate Behavior NOT Inverts its single input AND Produces 1 if all input values are 1 OR Produces 0 if all input values are 0 XOR Produces 0 if both input values are the same NAND Produces 0 if all input values are 1 NOR Produces 1 if all input values are 0 10 Combinational Circuits Gates are combined into circuits by using the output of one gate as the input for another This same circuit using a Boolean expression is AB + AC 11 Combinational Circuits Three inputs require eight rows to describe all possible input combinations 12 Combinational Circuits Consider the following Boolean expression A(B + C) Does this truth table look familiar? Compare it with previous table 13. -

Exclusive Or from Wikipedia, the Free Encyclopedia

New features Log in / create account Article Discussion Read Edit View history Exclusive or From Wikipedia, the free encyclopedia "XOR" redirects here. For other uses, see XOR (disambiguation), XOR gate. Navigation "Either or" redirects here. For Kierkegaard's philosophical work, see Either/Or. Main page The logical operation exclusive disjunction, also called exclusive or (symbolized XOR, EOR, Contents EXOR, ⊻ or ⊕, pronounced either / ks / or /z /), is a type of logical disjunction on two Featured content operands that results in a value of true if exactly one of the operands has a value of true.[1] A Current events simple way to state this is "one or the other but not both." Random article Donate Put differently, exclusive disjunction is a logical operation on two logical values, typically the values of two propositions, that produces a value of true only in cases where the truth value of the operands differ. Interaction Contents About Wikipedia Venn diagram of Community portal 1 Truth table Recent changes 2 Equivalencies, elimination, and introduction but not is Contact Wikipedia 3 Relation to modern algebra Help 4 Exclusive “or” in natural language 5 Alternative symbols Toolbox 6 Properties 6.1 Associativity and commutativity What links here 6.2 Other properties Related changes 7 Computer science Upload file 7.1 Bitwise operation Special pages 8 See also Permanent link 9 Notes Cite this page 10 External links 4, 2010 November Print/export Truth table on [edit] archived The truth table of (also written as or ) is as follows: Venn diagram of Create a book 08-17094 Download as PDF No. -

Combinational Logic Circuits

CHAPTER 4 COMBINATIONAL LOGIC CIRCUITS ■ OUTLINE 4-1 Sum-of-Products Form 4-10 Troubleshooting Digital 4-2 Simplifying Logic Circuits Systems 4-3 Algebraic Simplification 4-11 Internal Digital IC Faults 4-4 Designing Combinational 4-12 External Faults Logic Circuits 4-13 Troubleshooting Prototyped 4-5 Karnaugh Map Method Circuits 4-6 Exclusive-OR and 4-14 Programmable Logic Devices Exclusive-NOR Circuits 4-15 Representing Data in HDL 4-7 Parity Generator and Checker 4-16 Truth Tables Using HDL 4-8 Enable/Disable Circuits 4-17 Decision Control Structures 4-9 Basic Characteristics of in HDL Digital ICs M04_WIDM0130_12_SE_C04.indd 136 1/8/16 8:38 PM ■ CHAPTER OUTCOMES Upon completion of this chapter, you will be able to: ■■ Convert a logic expression into a sum-of-products expression. ■■ Perform the necessary steps to reduce a sum-of-products expression to its simplest form. ■■ Use Boolean algebra and the Karnaugh map as tools to simplify and design logic circuits. ■■ Explain the operation of both exclusive-OR and exclusive-NOR circuits. ■■ Design simple logic circuits without the help of a truth table. ■■ Describe how to implement enable circuits. ■■ Cite the basic characteristics of TTL and CMOS digital ICs. ■■ Use the basic troubleshooting rules of digital systems. ■■ Deduce from observed results the faults of malfunctioning combina- tional logic circuits. ■■ Describe the fundamental idea of programmable logic devices (PLDs). ■■ Describe the steps involved in programming a PLD to perform a simple combinational logic function. ■■ Describe hierarchical design methods. ■■ Identify proper data types for single-bit, bit array, and numeric value variables.