3 FPGA Fabrics

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Monolithic Integration of a Novel Microfluidic Device with Silicon Light Emitting Diode-Antifuse and Photodetector

ESSDERC 2002 Monolithic Integration of a Novel Microfluidic Device with Silicon Light Emitting Diode-Antifuse and Photodetector P. LeMinh, J. Holleman, J.W.Berenschot,N.R.Tas,A.vandenBerg MESA+ Research Institute, University of Twente, the Netherlands E-mail [email protected] Abstract developing an CMOS compatible etching recipe using Tetra Methyl Ammonium Hydroxide (TMAH). Light emitting diode antifuse has been integrated into In the next sections of the paper, fabrication process, a microfluidic device that is realized with extended some critical technological design parameters, electrical standard CMOS technological steps. The device and optical properties, few results on first applications comprises of a microchannel sandwiched between a will be described respectively. photodiode detector and a nanometer-scale diode antifuse light emitter. Within this contribution, the 2. Device realization device fabrication process, working principle and properties will be discussed. Change in the interference The realization of the device (figure 1) is a 10-mask fringe of the antifuse spectra has been measured due to process. The starting material is a 3-in silicon n-type the filling of the channel. Preliminary applications are wafer with standard doping. First of all, junction electroosmotic flow speed measurement, detection of photodiode areas were fabricated by implantation of absorptivity of liquids in the channel… boron. So as not to make any step height difference at the junction between n-type and p-type region, thick resist 1. Introduction was used as masking layer for the implantation. This is important to the evenness of the channel. The shape of Silicon is well-known as an electronic and mechanical the channel was then produced by shaping a layer of material but hardly ever used as an active optoelectronic 500nm thick LPCVD polysilicon deposited on top of the element, due to its inefficient radiative recombination first silicon rich nitride (SiRN) layer. -

Intel Quartus Prime Pro Edition User Guide: Partial Reconfiguration Send Feedback

Intel® Quartus® Prime Pro Edition User Guide Partial Reconfiguration Updated for Intel® Quartus® Prime Design Suite: 19.3 Subscribe UG-20136 | 2019.11.18 Send Feedback Latest document on the web: PDF | HTML Contents Contents 1. Creating a Partial Reconfiguration Design.......................................................................4 1.1. Partial Reconfiguration Terminology..........................................................................5 1.2. Partial Reconfiguration Process Sequence..................................................................6 1.3. Internal Host Partial Reconfiguration........................................................................ 7 1.4. External Host Partial Reconfiguration........................................................................ 9 1.5. Partial Reconfiguration Design Considerations............................................................9 1.5.1. Partial Reconfiguration Design Guidelines.................................................... 11 1.5.2. PR File Management.................................................................................12 1.5.3. Evaluating PR Region Initial Conditions....................................................... 16 1.5.4. Creating Wrapper Logic for PR Regions........................................................16 1.5.5. Creating Freeze Logic for PR Regions.......................................................... 17 1.5.6. Resetting the PR Region Registers.............................................................. 18 1.5.7. Promoting -

CHAPTER 3: Combinational Logic Design with Plds

CHAPTER 3: Combinational Logic Design with PLDs LSI chips that can be programmed to perform a specific function have largely supplanted discrete SSI and MSI chips in board-level designs. A programmable logic device (PLD), is an LSI chip that contains a “regular” circuit structure, but that allows the designer to customize it for a specific application. PLDs sold in the market is not customized with specific functions. Instead, it is programmed by the purchaser to perform a function required by a particular application. PLD-based board-level designs often cost less than SSI/MSI designs for a number of reasons. Since PLDs provide more functionality per chip, the total chip and printed- circuit-board (PCB) area are less. Manufacturing costs are reduced in other ways too. A PLD-based board manufacturer needs to keep samples of few, “generic” PLD types, instead of many different MSI part types. This reduces overall inventory requirements and simplifies handling. PLD-type structures also appear as logic elements embedded in LSI chips, where chip count and board areas are not an issue. Despite the fact that a PLD may “waste” a certain number of gates, a PLD structure can actually reduce circuit cost because its “regular” physical structure may use less chip area than a “random logic” circuit. More importantly, the logic function performed by the PLD structure can often be “tweaked” in successive chip revisions by changing just one or a few metal mask layers that define signal connections in the array, instead of requiring a wholesale addition of gates and gate inputs and subsequent re-layout of a “random logic” design. -

PPBI for OTP Fpgas Final Report

ESA UNCLASSIFIED – For Official Use estec European Space Research and Technology Centre Keplerlaan 1 2201 AZ Noordwijk The Netherlands Tel. (31) 71 5656565 Fax (31) 71 5656040 www.esa.int PPBI for OTP FPGAs Final Report Prepared by: Ken Hernan Reference: ESCC WG 01/13 Issue: 1 Revision: 9 Date of Issue: 23rd May 2014 Status: Final Document Type: WG Report ESA UNCLASSIFIED – For Official Use ESA UNCLASSIFIED – For Official Use Table of contents: 1 INTRODUCTION ...................................................................................................................................................... 5 1.1 SCOPE OF THE DOCUMENT ..................................................................................................................................... 5 1.2 APPLICABLE AND REFERENCE DOCUMENTS ........................................................................................................... 5 1.2.1 Reference Documents (RDs) .......................................................................................................................... 5 1.3 ACRONYMS AND ABBREVIATIONS .......................................................................................................................... 6 2 EXECUTIVE SUMMARY ........................................................................................................................................ 9 3 WOKRING GROUP ACTIVITIES ........................................................................................................................ 15 4 BACKGROUND -

Semiconductor Devices

H01L CPC COOPERATIVE PATENT CLASSIFICATION H ELECTRICITY (NOTE omitted) H01 BASIC ELECTRIC ELEMENTS (NOTES omitted) H01L SEMICONDUCTOR DEVICES; ELECTRIC SOLID STATE DEVICES NOT OTHERWISE PROVIDED FOR (use of semiconductor devices for measuring G01; resistors in general H01C; magnets, inductors, transformers H01F; capacitors in general H01G; electrolytic devices H01G 9/00; batteries, accumulators H01M; waveguides, resonators, or lines of the waveguide type H01P; line connectors, current collectors H01R; stimulated-emission devices H01S; electromechanical resonators H03H; loudspeakers, microphones, gramophone pick-ups or like acoustic electromechanical transducers H04R; electric light sources in general H05B; printed circuits, hybrid circuits, casings or constructional details of electrical apparatus, manufacture of assemblages of electrical components H05K; use of semiconductor devices in circuits having a particular application, see the subclass for the application) NOTES 1. This subclass covers: • electric solid state devices which are not covered by any other subclass and details thereof, and includes: semiconductor devices adapted for rectifying, amplifying, oscillating or switching; semiconductor devices sensitive to radiation; electric solid state devices using thermoelectric, superconductive, piezo-electric, electrostrictive, magnetostrictive, galvano- magnetic or bulk negative resistance effects and integrated circuit devices; • photoresistors, magnetic field dependent resistors, field effect resistors, capacitors with potential-jump -

Recent Advancement in the Memristor Memory Development Ravikumar K

International Journal of Innovative Technology and Exploring Engineering (IJITEE) ISSN: 2278-3075, Volume-9 Issue-7, May 2020 Recent Advancement in the Memristor Memory Development Ravikumar K. I, Sukumar R voltages as referred to in [19]) and d) manufacturing methods Abstract: Meritor is a newly-created tool and because of its compliant with CMOS relative to other NVM systems. nanometer scale and different electrical properties it has received Relative to other MRM (Resistive random access memory) much interest from advanced electronics designers since it was there are specific advantages. The RRAM is combined with discovered. The memory capacity of a memrist is one of the most significant features. In this paper, about 50 papers on designing the SRAM cell in past works such as [20–23], but each of memristor, optimization rules for reducing power, area for configuration either contributes to substantial deterioration of storing the data into memristor and implemented the full adders the fundamental SRAM reading process or absorbs a huge using memristor using the Pspice simulator. The paper ultimately amount of energy for the storage / restoration of data to / from addresses the complex study lapses and obstacles in constructing RRAM as described further in depth in section 4. In our paper the memorial that will enable scholars and thinkers lead to more analysis. we give a new NV-SRAM 8T1R that is similar to a standard Keywords: memristor, optimization. SRAM 6 T device with reading power, delay and noise tolerance. In turn, since only one RRAM cell is required for I. INTRODUCTION the off-time storage of SRAM data, energy used for processing RRAM data is reduced by more than 60% relative The resistive memory of the Crossbar has recently gained to the lowest energy density of previous RRAM NV-SRAM tremendous publicity owing to its amazing high density and designs. -

Reliability of the Amorphous Silicon Antifuse

Reliability of the Amorphous Silicon Antifuse • • • • • • QuickLogic® White Paper Abstract Development processes at QuickLogic control the reliability of the QuickLogic ViaLink® antifuse. ViaLink reliability is built into the silicon at every step, beginning with design rules and device characterization. But unlike other fab processes, the reliability work continues with the layout rules, test methodology, place and route software, ViaLink programming sequence, programming algorithm, qualification plans, and quality assurance process. All these factors come together to create the reliable QuickLogic ViaLink. Introduction Semiconductor reliability has been studied and characterized [1]. The initial failure rate, also called infant mortality, is high due to defects. The midterm life of a semiconductor component has a low failure rate. Most of the defects have already failed, and the wear out failure for mechanisms has not started. At the end of the semiconductor component life, many elements of the semiconductor begin to wear out. Physical changes to the metals, semiconductor, and dielectrics cause the component to no longer meet the original specification. These failures are predictable and increase with time. This high-low-high failure rate is known as the bathtub curve and is shown in Figure 1. Figure 1: Bathtub curve for semiconductor failure rate. Semiconductor manufacturers have reduced the infant mortality by decreasing the number of defects and screening for the remaining defects. Defects have been reduced with improved and automated wafer handling, improved equipment and improved processes. Automatic inspections have been added during wafer fabrication for the purpose of detecting wafers with defects. Wafers that cannot be reworked are scrapped. After fabrication, wafers are tested for correct electrical parameters. -

Ice40 Ultraplus Family Data Sheet

iCE40 UltraPlus™ Family Data Sheet FPGA-DS-02008 Version 1.4 August 2017 iCE40 UltraPlus™ Family Data Sheet Copyright Notice Copyright © 2017 Lattice Semiconductor Corporation. All rights reserved. The contents of these materials contain proprietary and confidential information (including trade secrets, copyright, and other Intellectual Property interests) of Lattice Semiconductor Corporation and/or its affiliates. All rights are reserved. You are permitted to use this document and any information contained therein expressly and only for bona fide non-commercial evaluation of products and/or services from Lattice Semiconductor Corporation or its affiliates; and only in connection with your bona fide consideration of purchase or license of products or services from Lattice Semiconductor Corporation or its affiliates, and only in accordance with the terms and conditions stipulated. Contents, (in whole or in part) may not be reproduced, downloaded, disseminated, published, or transferred in any form or by any means, except with the prior written permission of Lattice Semiconductor Corporation and/or its affiliates. Copyright infringement is a violation of federal law subject to criminal and civil penalties. You have no right to copy, modify, create derivative works of, transfer, sublicense, publicly display, distribute or otherwise make these materials available, in whole or in part, to any third party. You are not permitted to reverse engineer, disassemble, or decompile any device or object code provided herewith. Lattice Semiconductor Corporation reserves the right to revoke these permissions and require the destruction or return of any and all Lattice Semiconductor Corporation proprietary materials and/or data. Patents The subject matter described herein may contain one or more inventions claimed in patents or patents pending owned by Lattice Semiconductor Corporation and/or its affiliates. -

Architecture Description and Packing for Logic Blocks with Hierarchy, Modes and Complex Interconnect

Architecture Description and Packing for Logic Blocks with Hierarchy, Modes and Complex Interconnect Jason Luu, Jason Anderson, and Jonathan Rose The Edward S. Rogers Sr. Department of Electrical and Computer Engineering University of Toronto, Toronto, ON, Canada jluu|janders|[email protected] SRHI D SRLO Reset Type INIT1 Q CE Sync/Async ABSTRACT COUT INIT0 CK SR FF/LAT DX The development of future FPGA fabrics with more sophis- DMUX DI2 D6:1 A6:A1 W6:W1 D ticated and complex logic blocks requires a new CAD flow D O6 FF/LAT O5 DX INIT1 Q DQ D INIT0 CK DI1 SRHI that permits the expression of that complexity and the abil- CE SRLO WEN MC31 SRHI D SRLO CK Q SR DI INIT1 CE INIT0 ity to synthesize to it. In this paper, we present a new logic CK SR CX CMUX block description language that can depict complex intra- DI2 C6:1 A6:A1 W6:W1 C C O6 block interconnect, hierarchy and modes of operation. These FF/LAT O5 CX INIT1 Q CQ D INIT0 CK DI1 CE SRHI SRLO features are necessary to support modern and future FPGA WEN MC31 SRHI CK D SRLO SR CI INIT1 Q CE INIT0 complex soft logic blocks, memory and hard blocks. The key CK SR BX BMUX part of the CAD flow associated with this complexity is the DI2 B6:1 A6:A1 W6:W1 B B O6 packer, which takes the logical atomic pieces of the complex O5 FF/LAT BX INIT1 Q BQ D DI1 INIT0 CK CE SRHI SRLO WEN MC31 SRHI CK blocks and groups them into whole physical entities. -

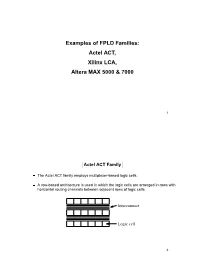

Examples of FPLD Families: Actel ACT, Xilinx LCA, Altera MAX 5000 & 7000

Examples of FPLD Families: Actel ACT, Xilinx LCA, Altera MAX 5000 & 7000 1 Actel ACT Family ¯ The Actel ACT family employs multiplexer-based logic cells. ¯ A row-based architecture is used in which the logic cells are arranged in rows with horizontal routing channels between adjacent rows of logic cells. Interconnect Logic cell 2 ACT 1 Logic Modules ¯ ACT 1 FPGAs use a single type of logic module. Logic Module Logic Module Logic Module M1 A0 F A0 D Actel ACT 0 F1 A1 0 M3 F1 A1 1 '1' 1 SA F1 S F SA 0 F F2 C 0 M2 1 B0 1 B0 S D 0 B1 0 F2 B1 1 F2 '1' 1 SB (a) S SB S3 A S0 S3 S0 '0' S1 O1 S1 O1 B F=(A·B)+(B'·C)+D (b) (c) (d) (a) An Actel FPGA. (b) An ACT 1 logic module. (c) An implementation of an ACT 1 logic module using pass transistors. (d) An example of function implementation by an ACT 1 logic module. 3 ACT 2 and ACT 3 Logic Modules ¯ Both ACT 2 and ACT 3 FPGAs use two types of logic module. C-Module S-Module (ACT 2) S-Module (ACT 3) D00 D00 SED00 SE D01 D01 D01 D10 YOUTD10 YQD10 YQ D11 D11 D11 A1 A1 A1 B1 S1 B1 S1 B1 S1 A0 A0 A0 B0 S0 CLR S0 B0 S0 CLR CLK CLK (a) (b) (c) SE (sequential element) SE 1 1 D D Q Q Z Z D 0 0 Q CLK C2 S S C1 master slave C2 latch latch CLR CLR C1 CLR combinational logic for clock flip-flop macro and clear D 1D Q CLK C1 (d) (e) (a) The C-module used by both ACT 2 and ACT 3 FPGAs. -

Efpgas : Architectural Explorations, System Integration & a Visionary Industrial Survey of Programmable Technologies Syed Zahid Ahmed

eFPGAs : Architectural Explorations, System Integration & a Visionary Industrial Survey of Programmable Technologies Syed Zahid Ahmed To cite this version: Syed Zahid Ahmed. eFPGAs : Architectural Explorations, System Integration & a Visionary Indus- trial Survey of Programmable Technologies. Micro and nanotechnologies/Microelectronics. Université Montpellier II - Sciences et Techniques du Languedoc, 2011. English. tel-00624418 HAL Id: tel-00624418 https://tel.archives-ouvertes.fr/tel-00624418 Submitted on 16 Sep 2011 HAL is a multi-disciplinary open access L’archive ouverte pluridisciplinaire HAL, est archive for the deposit and dissemination of sci- destinée au dépôt et à la diffusion de documents entific research documents, whether they are pub- scientifiques de niveau recherche, publiés ou non, lished or not. The documents may come from émanant des établissements d’enseignement et de teaching and research institutions in France or recherche français ou étrangers, des laboratoires abroad, or from public or private research centers. publics ou privés. Université Montpellier 2 (UM2) École Doctorale I2S LIRMM (Laboratoire d'Informatique, de Robotique et de Microélectronique de Montpellier) Domain: Microelectronics PhD thesis report for partial fulfillment of requirements of Doctorate degree of UM2 Thesis conducted in French Industrial PhD (CIFRE) framework between: Menta & LIRMM lab (Dec.2007 – Feb. 2011) in Montpellier, FRANCE “eFPGAs: Architectural Explorations, System Integration & a Visionary Industrial Survey of Programmable Technologies” eFPGAs: Explorations architecturales, integration système, et une enquête visionnaire industriel des technologies programmable by Syed Zahid AHMED Presented and defended publically on: 22 June 2011 Jury: Mr. Guy GOGNIAT Prof. at STICC/UBS (Lorient, FRANCE) President Mr. Habib MEHREZ Prof. at LIP6/UPMC (Paris, FRANCE) Reviewer Mr. -

Spartan-II FPGA Family Data Sheet

R Spartan-II FPGA Family Data Sheet DS001 March 12, 2021 Product Specification This document includes all four modules of the Spartan®-II FPGA data sheet. Module 1: Module 3: Introduction and Ordering Information DC and Switching Characteristics DS001-1 (v2.9) March 12, 2021 DS001-3 (v2.9) March 12, 2021 • Introduction • DC Specifications •Features - Absolute Maximum Ratings • General Overview - Recommended Operating Conditions • Product Availability - DC Characteristics • User I/O Chart - Power-On Requirements - DC Input and Output Levels • Ordering Information • Switching Characteristics Module 2: - Pin-to-Pin Parameters Functional Description - IOB Switching Characteristics - Clock Distribution Characteristics DS001-2 (v2.9) March 12, 2021 - DLL Timing Parameters • Architectural Description - CLB Switching Characteristics - Spartan-II Array - Block RAM Switching Characteristics - Input/Output Block - TBUF Switching Characteristics - Configurable Logic Block - JTAG Switching Characteristics - Block RAM - Clock Distribution: Delay-Locked Loop Module 4: - Boundary Scan Pinout Tables • Development System DS001-4 (v2.9) March 12, 2021 • Configuration • Pin Definitions - Configuration Timing • Pinout Tables • Design Considerations IMPORTANT NOTE: This Spartan-II FPGA data sheet is in four modules. Each module has its own Revision History at the end. Use the PDF "Bookmarks" for easy navigation in this volume. © 2000-2021 Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, the Brand Window, and other designated brands included herein