Pin Information for the Intel® Stratix®10 1SG10M Device Version: 2020-10-22

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

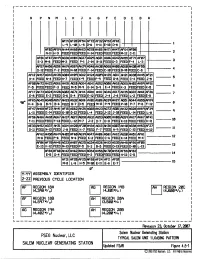

Salem Generating Station, Units 1 & 2, Revision 29 to Updated Final Safety Analysis Report, Chapter 4, Figures 4.5-1 to 4.5

r------------------------------------------- 1 I p M J B I R N L K H G F E D c A I I I I I Af'Jq AF20 AF54 AF72 32 AF52 AF18 I L-q L-10 L-15 D-6 -11 E-10 D-8 l I AF03 Af't;qAH44 AH60 AH63 AG70 AH65 AH7l AH47 AFS4 AF08 I N-ll H-3 FEED FEED FEED H-14 FEED FEED FEED M-12 C-11 2 I AF67 AH4q AH04 AG27 AG2<i' AG21 AG16 AG42 AF71 AF07 AF01 AG36 AH!5!5 3 I E-3 M-6 FEED M-3 FEED P-1 J-14 B-11 FEED D-3 FEED F-4 L-3 I AF67 AH5S AG56 Atflq AGsq AH2<1' AG48 AH30 AG68 AH08 AG60 AH30 AF55 I D-12 FEED F-2 FEED N-11 FEED F-14 FEED C-11 FEED B-11 FEED C-8 4 I AF12 AH57 AG43 AH38 AHtiJq AG12 AH24 AGfR AH25 AGil AG31 AH45 AF21 AGlM AH21 5 I H~4 FEED N-4 FEED H-7 FEED K~q FEED F-q FEED G-8 FEED C-4 FEED J-15 I AF50 AH72 AH22 AGS6 AH15 AGll.lAG64 AG41 AG52 AG88 AH18 AG65 AHIJ2 AH5q AF51 I F-5 FEED FEED F-3 FEED M-5 r+q G-14 o-q E-4 FEED K-3 FEED FEED K-5 6 I f:Fl7 AH73 AG24 AH28 AG82 AG71 AH14 AG18 AHil AG46 AG17 AH35 AG22 AH61 AF26 7 I E-8 FEED E-2 FEED G-6 G-4 FEED E-12 FEED J-4 J-6 FEED L-2 FEED E-5 I Af&q I qeo AF65 AG45 AtM0 AG57 AH33 AG32 AG16 AH01 AGI6 AG3<1' AH27 AG51 AG44 AG55 K-4 B-8 e-q B-6 FEED B-7 P-5 FEEC M-11 P-q FEED P-11 P-7 P-8 F-12 8 I AF47 AH68 AF23 AH41 AF1!5 AG62 AH26 AG03 AH23 AH32 AG28 AHsq AF3<1' q I L-U FEED E-14 FEED G-10 G-12 FEED L-4 FEED FEED L-14 FEED L-8 I ~~ AF66 AH66 AH10 AG67 AH37 AGJq AG68 AG3l AG63 AG05 AH08 AG5q AH17 AH67 AF41 I F-11 FEED FEED F-13 FEED L-12 M-7 J-2 D-7 D-11 FEED K-13 FEED FEED K-11 10 I AE33 AH!52 AG37 AH31 AG14 AH20 AF20 AH34 AG13 AH36 AG07 AH40 AG38 AH!53 AF27 I G-ll FEED N-12 FEED J-8 FEED K-7 FEED -

Statement by Mr. Abduvohid Karimov, Chairman of The

EF.DEL/39/06 22 May 2006 ENGLISH Original: RUSSIAN STATEMENT BY MR. ABDUVOHID KARIMOV, CHAIRMAN OF THE STATE COMMITTEE FOR ENVIRONMENTAL PROTECTION AND FORESTRY OF THE REPUBLIC OF TAJIKISTAN, AT THE FOURTEENTH MEETING OF THE OSCE ECONOMIC FORUM Prague, 22 to 24 May 2006 Transport development and the environment in the Republic of Tajikistan Mr. Chairman, Ladies and Gentlemen, Allow me on behalf of the Government of the Republic of Tajikistan to express our sincere gratitude to the Organization for Security and Co-operation in Europe for the invitation to this meeting and to the OSCE Centre in Dushanbe in particular for helping us to participate in the work of the Fourteenth Meeting of the OSCE Economic Forum to examine transport development with a view to enhancing regional economic co-operation and stability and its impact on the environment. Regional and international environmental co-operation is one of the main focuses of the Government of the Republic of Tajikistan, increasing the effectiveness of many decisions adopted and helping in the implementation of practical measures to improve the state of the environment in our country and in the region. As you are aware, the Republic of Tajikistan played an active role in the preparation of the international conference held in Dushanbe on 7 and 8 November 2005, and representatives from Tajikistan also took part in the first stage of the Forum in Vienna in January of this year. This once again confirms Tajikistan’s desire to support an international policy of development and to create favourable conditions for its implementation in our country and in the region. -

Pin Information for the Stratix IV GT EP4S40G2 Device

Pin Information for the Stratix® IV GT EP4S40G2 Device Version 1.2 Note (1) Dynamic Bank Configuration Dedicated Tx/Rx Emulated LVDS OCT DQS for X4 for DQS for X8/X9 for DQS for X16/ X18 for Number VREF Pin Name/Function Optional Function(s) Function Channel Output Channel F1517 Support F1517 F1517 F1517 1A TDI TDI J29 No 1A TMS TMS N27 No 1A TRST TRST A32 No 1A TCK TCK G30 No 1A TDO TDO F30 No 1A VREFB1AN0 IO DIFFIO_TX_L1n DIFFOUT_L1n K29 Yes 1A VREFB1AN0 IO DIFFIO_TX_L1p DIFFOUT_L1p L29 Yes 1A VREFB1AN0 IO RDN1A DIFFIO_RX_L1n DIFFOUT_L2n C34 Yes 1A VREFB1AN0 IO RUP1A DIFFIO_RX_L1p DIFFOUT_L2p D34 Yes 1A VREFB1AN0 IO DIFFIO_TX_L2n DIFFOUT_L3n J30 Yes DQ1L DQ1L DQ1L 1A VREFB1AN0 IO DIFFIO_TX_L2p DIFFOUT_L3p K30 Yes DQ1L DQ1L DQ1L 1A VREFB1AN0 IO DIFFIO_RX_L2n DIFFOUT_L4n C31 Yes DQSn1L DQ1L DQ1L 1A VREFB1AN0 IO DIFFIO_RX_L2p DIFFOUT_L4p D31 Yes DQS1L DQ1L/CQn1L DQ1L 1A VREFB1AN0 IO DIFFIO_TX_L3n DIFFOUT_L5n M28 Yes DQ1L DQ1L DQ1L 1A VREFB1AN0 IO DIFFIO_TX_L3p DIFFOUT_L5p N28 Yes DQ1L DQ1L DQ1L NC C35 Yes NC D35 Yes 1A VREFB1AN0 IO DIFFIO_TX_L4n DIFFOUT_L7n H32 Yes DQ2L DQ1L DQ1L 1A VREFB1AN0 IO DIFFIO_TX_L4p DIFFOUT_L7p J32 Yes DQ2L DQ1L DQ1L 1A VREFB1AN0 IO DIFFIO_RX_L4n DIFFOUT_L8n B32 Yes DQ2L DQ1L DQ1L 1A VREFB1AN0 IO DIFFIO_RX_L4p DIFFOUT_L8p C32 Yes DQ2L DQ1L DQ1L 1A VREFB1AN0 IO DIFFIO_TX_L5n DIFFOUT_L9n M31 Yes DQ3L DQ2L DQ1L 1A VREFB1AN0 IO DIFFIO_TX_L5p DIFFOUT_L9p N31 Yes DQ3L DQ2L DQ1L 1A VREFB1AN0 IO DIFFIO_RX_L5n DIFFOUT_L10n C33 Yes DQSn3L DQ2L DQSn1L/DQ1L 1A VREFB1AN0 IO DIFFIO_RX_L5p DIFFOUT_L10p D33 Yes DQS3L DQ2L/CQn2L -

Policy & Governance Committee

AGENDA BOG Policy & Governance Committee Meeting Date: February 12, 2021 Location: Videoconference Chair: Kamron Graham Vice-Chair: Kate Denning Members: Gabriel Chase, Kate Denning, John Grant, Rob Milesnick, Curtis Peterson, Joe Piucci, David Rosen Staff Liaison: Helen M. Hierschbiel Charge: Develops and monitors the governing rules and policies relating to the structure and organization of the bar; ensures that all bar programs and services comply with organizational mandates and achieve desired outcomes. Identifies and brings emerging issues to the BOG for discussion and action. 2021 PGC Work Plan 1. Wellness Task Force Report. Review report and decide whether to pursue any Exhibit Action 10 recommendations. 2. Evidence-Based Decision-Making Policy. Review Futures Task Force recommendation regarding evidence-based decision-making To Be Posted Action 10 policy and consider whether to adopt the recommended policy. 3. HOD Authority. Discuss whether to pursue changes to limits of HOD authority either Exhibit Action 10 through amendments to HOD Rules or Bar Act. 4. OSB Bylaw Overhaul. Review draft of OSB bylaw overhaul, splitting between policies and Exhibit Discussion 20 bylaws. 5. Bar Sponsorship of Lawyer Referral Services. Review issue presented by Legal Ethics Exhibit Discussion 20 Committee. February 12, 2021 Policy & Governance Committee Agenda Page 2 6. Section Program Review. Review feedback Exhibit Discussion 20 regarding proposed changes to bylaws. 7. Approve minutes of January 8, 2021 meeting. Exhibit Action 1 2021 POLICY & GOVERNANCE WORK PLAN February 12, 2021 draft 2021 AREAS OF TO DO TASKS IN PROCESS (PGC) PGC TASKS DONE IN PROCESS (BOG) BOG TASKS FOCUS 1. Identify information needed 1. -

Asia-Europe Connectivity Vision 2025

Asia–Europe Connectivity Vision 2025 Challenges and Opportunities The Asia–Europe Meeting (ASEM) enters into its third decade with commitments for a renewed and deepened engagement between Asia and Europe. After 20 years, and with tremendous global and regional changes behind it, there is a consensus that ASEM must bring out a new road map of Asia–Europe connectivity and cooperation. It is commonly understood that improved connectivity and increased cooperation between Europe and Asia require plans that are both sustainable and that can be upscaled. Asia–Europe Connectivity Vision 2025: Challenges and Opportunities, a joint work of ERIA and the Government of Mongolia for the 11th ASEM Summit 2016 in Ulaanbaatar, provides the ideas for an ASEM connectivity road map for the next decade which can give ASEM a unity of purpose comparable to, if not more advanced than, the integration and cooperation efforts in other regional groups. ASEM has the platform to create a connectivity blueprint for Asia and Europe. This ASEM Connectivity Vision Document provides the template for this blueprint. About ERIA The Economic Research Institute for ASEAN and East Asia (ERIA) was established at the Third East Asia Summit (EAS) in Singapore on 21 November 2007. It is an international organisation providing research and policy support to the East Asia region, and the ASEAN and EAS summit process. The 16 member countries of EAS—Brunei Darussalam, Cambodia, Indonesia, Lao PDR, Malaysia, Myanmar, Philippines, Singapore, Thailand, Viet Nam, Australia, China, India, Japan, Republic of Korea, and New Zealand—are members of ERIA. Anita Prakash is the Director General of Policy Department at ERIA. -

Athens County Communities

51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 C GM JOHNSON C GM JOHNSON D HILL-BUCHTEL RD y R ODNR RD Sunda 33 W L O CARBON L A L U D O E H R A E B A K OLD A AR 278 DU SW O WATERWORKS HILL RD M C RD A P N K S RD BUCHTEL T-624A R D 13 T-622 D HOCKING COUNTY D KL 78 R Creek N A EY T N 31 E D O DR S T-35 O W HOCKING COUNTY R T N ILLIAMS ST ATHENS COUNTY W S H S U O Y J RD GLOUSTER CEMETERY O Sunday ATHENS COUNTY C J DEW T BUCHTEL UNITED H A 5 O EDWARDS ST CEMETERY S CEMETERY T-315 M 7 H K METHODIST CHURCH R 6 A O M C N I K D R W R R D E E M Y R AMO N D E O E I I CONNER M D o W D W E L E V n N P ST S O T-567 FRANK ST R T BESSEMER RDELM ST S L F d A B L ELM T B S A N T B T RD R K a W LOVE T T O A S y M V r E A S V ANKLI T R N T-675 I F S a 78 Y T-22 A T-1276 T SYCAMORE ST A R O A PINE ST EA T-1276 R n O D T L IETTA c L GROVER DOVER T P 685 h A WHITMORE T-22 S K GROVER ST T Nelsonville LID E AV EUC A D D FAIRVIEWSCOS V GROVE DR ST VERITY ST FR-3 u A V R D - York n COLLEGE ST RD L A O P E d E N I R DOVER VILLAGE OF GLOUSTER a G N CROSS ST y S R E E DR BUCHTEL MOUND R LAN Nelsonville - York H Buchtel MAYOR’S C R W O O D Park DIAMOND O AV r ST U V E Nelsonville Community OFFICE IO E E H T N Park C O D Y 33B BRICK RD R T-22A S R E C W ST D T K TWELFTH ST DR ST BUCK E E S YE WATERLOO r C B BUCHTEL e A D APARTMENTS N EARL ST OAK ST OAK MILL ST Wayne National Forest TRIMBLSYLVANIAE AV BROAD T-1305 U K PINE GROVE PINE H C e C ELIZABETH MT ST MARY DR B ST MARY OF RD T EMBRY ST GLOUSTER FORT ST FORT k ADAMS -

Radiation, Protection of the Public and the Environment (Poster Session 1) Origin and Migration of Cs-137 in Jordanian Soils

Major scientific thematic areas: TA6 – Radiation, Protection of the Public and the Environment (Poster session 1) Origin and Migration of Cs-137 in Jordanian Soils Ahmed Qwasmeh, Helmut W. Fischer IUP- Institute for Environmental Physics, Bremen University, Germany Abstract Whilst some research and publication has been done and published about natural radioactivity in Jordan, only one paper has been published about artificial radioactivity in Jordanian soils (Al Hamarneh 2003). It reveals high concentrations of 137Cs and 90Sr in some regions in the northwest section of Jordan. The origin of this contamination was not determined. Two sets of soil samples were collected and brought from northwest section of Jordan for two reasons, namely; the comparable high concentration of 137Cs in this region according to the above-mentioned paper and because most of the population concentrates in this region. The first set of samples was collected in April 2004 from eleven different sites of this region of Jordan. The second set of samples has been brought in July 2005 from six of the previous sites where we had found higher 137Cs contamination. The second set was collected as thinner sliced soil samples for further studying and to apply a suitable model for 137Cs migration in soil. Activity of 137Cs was measured using a HpGe detector of 50% relative efficiency and having resolution of 2keV at 1.33MeV. Activity of 90Sr was measured for the samples of four sites of the first set of samples, using a gas-filled proportional detector with efficiency of 21.3% cps/Bq. The total inventory of 137Cs in Bq/m2 has been calculated and the correlation between 137Cs inventory and annual rainfall and site Altitude has been studied. -

1St IRF Asia Regional Congress & Exhibition

1st IRF Asia Regional Congress & Exhibition Bali, Indonesia November 17–19 , 2014 For Professionals. By Professionals. "Building the Trans-Asia Highway" Bali’s Mandara toll road Executive Summary International Road Federation Better Roads. Better World. 1 International Road Federation | Washington, D.C. ogether with the Ministry of Public Works Indonesia, we chose the theme “Building the Trans-Asia Highway” to bring new emphasis to a visionary project Tthat traces its roots back to 1959. This Congress brought the region’s stakeholders together to identify new and innovative resources to bridge the current financing gap, while also sharing case studies, best practices and new technologies that can all contribute to making the Trans-Asia Highway a reality. This Congress was a direct result of the IRF’s strategic vision to become the world’s leading industry knowledge platform to help countries everywhere progress towards safer, cleaner, more resilient and better connected transportation systems. The Congress was also a reflection of Indonesia’s rising global stature. Already the largest economy in Southeast Asia, Indonesia aims to be one of world’s leading economies, an achievement that will require the continued development of not just its own transportation network, but also that of its neighbors. Thank you for joining us in Bali for this landmark regional event. H.E. Eng. Abdullah A. Al-Mogbel IRF Chairman Minister of Transport, Kingdom of Saudi Arabia Indonesia Hosts the Region’s Premier Transportation Meeting Indonesia was the proud host to the 1st IRF Asia Regional Congress & Exhibition, a regional gathering of more than 700 transportation professionals from 52 countries — including Ministers, senior national and local government officials, academics, civil society organizations and industry leaders. -

International Society for Soil Mechanics and Geotechnical Engineering

INTERNATIONAL SOCIETY FOR SOIL MECHANICS AND GEOTECHNICAL ENGINEERING This paper was downloaded from the Online Library of the International Society for Soil Mechanics and Geotechnical Engineering (ISSMGE). The library is available here: https://www.issmge.org/publications/online-library This is an open-access database that archives thousands of papers published under the Auspices of the ISSMGE and maintained by the Innovation and Development Committee of ISSMGE. Dynamic centrifuge model test for performance-based design of grid-form deep mixing walls supporting a tall building Junji Hamada & Tsuyoshi Honda Takenaka Research & Development Institute, Takenaka Corporation, Inzai, Chiba, Japan ABSTRACT Dynamic centrifuge model tests in the 50 g field were conducted to investigate a failure behavior of DMWs in liquefiable sand during large earthquakes. A miniature model of DMWs was made of soil-cement with an unconfined compressive strength of about 4,000 kPa in order to investigate the behavior/toughness of the DMWs after yield and failure on seismic performance. The DMWs model that support the superstructure’s weight of 206 kPa, the natural period of 0.6 second were set in a laminar shear box, and repeatedly tested by increasing the acceleration level of the input motion recorded at TAFT earthquakes. The relationship between shear stress and shear strain of the DMWs, namely the nonlinearity of the DMWs was investigated. No significant settlement of the structure was observed even if the normal and shear stresses in the DMWs were assumed to have locally reached the tensile or shear criteria of soil-cement. 1 INTRODUCTION potential for liquefaction mitigation. However, the local failures of the DMWs are not acceptable in the existing Grid-form DMWs (Deep cement Mixing Walls) which is method of allowable stress design. -

The Eurasec Transport Corridors

Îñíîâíûå âûâîäû îáçîðà The EurAsEC Transport Corridors Sector Report March 2009 The Eurasian Development Bank is an international financial institution established to promote economic growth and integration processes in Eurasia. The Bank was founded by the intergovernmental agreement signed in January 2006 by the Russian Federation and the Republic of Kazakhstan. Negotiations are currently under way with a number of neighbouring countries. Electric power, water and energy, transportation infrastructure and high-tech and innovative industries are the key areas for Bank’s financing activity. The Bank, as part of its mission, provides quality research and analysis of contemporary development issues and trends in the region with particular focus on Eurasian integration. The Bank conducts regular conferences and round tables addressing various aspects of integration. In 2008, the Bank launched quarterly academic and analytical Journal of Eurasian Economic Integration and an annual EDB Eurasian Integration Yearbook. In addition, the Bank publishes regular analytical digests covering regional integration, development banks’ activities and investment projects in the post-Soviet space. The Bank’s Strategy and Research Department publishes detailed Sector and Country Analytical Reports. It also plans to realise a number of research and technical assistance projects. The “System of Indicators of Eurasian Integration” project is the first in the project pipeline. Address: Republic of Kazakhstan 050000, Almaty, Panfilov St. 98 Eurasian Development Bank Tel.: +7 (727) 244 40 44 ext. 6146 Fax: +7 (727) 244 65 70, 291 42 63 E-mail: [email protected] http://www.eabr.org No part of this publication may be reprinted or reproduced or utilized in any form, including reprinting and recording of any kind without due reference to this publication. -

Auction 14A Final Draft.Vp

OUR STAFF Stephen Album Paul Montz Director of Islamic & Early Indian Numismatics Director of World Coins Steve has been serving the Paul joined the staff in January numismatic community since 2011. He attended UC Davis 1960. In 1976 he began dealing from 1975-80, earning bachelor's nearly exclusively in Islamic and and master's degrees in Indian coins. He has authored Agricultural Science & several books including the Management and Agronomy, Catalogue of California Trade respectively. He began working Tokens, Volumes I & II in 1972 in the numismatic field in the and 1974 respectively. 1977 saw 1970's. In 1981, he founded the release of his complete rewrite of Marsden's Olde World Numismatics in Chico, CA, a business he Numismata Orientalia Illustrata, a guide to Islamic ran for 30 years, focusing on A-Z world coins, before and Oriental coins with values. In 1993 he published merging with Stephen Album Rare Coins. He has put A Checklist of Islamic Coins, which now in its second out price lists for many years and has been a fixture edition is the standard for collectors of Islamic coins. at major shows since the 1980's. Paul is a life Mr. Album is currently a senior fellow at the member of the American Numismatic Association Worcester College, Oxford, England, and in this and is a member of other organizations. He has been position has authored three of the ten volumes of the a contributing editor for the Standard Catalog of Sylloge of Islamic Coins in the Ashmolean (Museum) World Coins since 1998. Paul brings experience in beginning in 1999. -

Affordable Housing 7

549 Main Street, Chatham, MA 02633 ph: 5089455100 Chatham Town Office fx: 5089453550 Affordable Housing 7. Affordable Housing Overview When one compares the maximum affordable home purchase prices for an average, locallyemployed Chatham couple or family to the average listing price for Chatham residential properties, it is clear that there is a remarkable affordability gap for locallyemployed Chatham workers and residents who wish to acquire their own home. Affordable Housing Strategies for Chatham, June 1988 After World War II, Chatham experienced both a residential building boom and an unprecedented influx of new residents, primarily of retirement age. The number of housing units has nearly quadrupled since 1945, while the population has more than tripled. The percentage of houses used only seasonally has steadily increased, though figures are elusive. From 1980 to 2000, the percentage of houses used yearround has declined from 53% to 47%, with the result that presently half of Chatham’s housing units are used seasonally and the number of houses now exceeds the yearround census population 6,743 units versus 6,625 people. As land costs increased, inexpensive homes, primarily smaller yearround affordable houses, were sold, enlarged or totally replaced for retirement and/or second homes, depleting the affordable housing stock drastically. A substantial gap exists between mortgage costs and the price which typical area residents can pay. As of 1999, the maximum mortgage affordable by a household with the area’s median income ($44,700) was $117,220 and for a moderate income household (one earning 80% of the median income), the maximum affordable mortgage was $89,400.