Scpc486 2192-09127-000-000

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Printing Machine Computer Based Control System

Printing Machine Computer Based Control System Sayed Haroon Shadad A thesis submitted to University of Khartoum, the Faculty of Engineering, Department of Electrical and Electronic Engineering, in complete fulfillment of the requirements for the degree of Masters of Science In Electrical & Electronic Engineering Supervisor: Dr. Sami Mohamed Sharif 2004 Keywords: printing, machine, computer based, control ﺑﺴﻢ اﷲ اﻟﺮﺣﻤﻦ اﻟﺮﺣﻴﻢ (وءاﺗﺎآﻢ ﻡﻦ آﻞ ﻡﺎ ﺱﺄﻟﺘﻤﻮﻩ وإن ﺗﻌﺪوا ﻧﻌﻤﺖ اﷲ ﻻ ﺗﺤﺼﻮهﺎ إن اﻹﻧﺴﺎن ﻟﻈﻠﻮم آﻔﺎر) اﻵیﺔ (٣٤) ﻡﻦ ﺱﻮرة إﺑﺮاهﻴﻢ i Dedication To my daughters and sons: “A little knowledge is a dangerous thing---incomplete knowledge about a subject is sometimes worse than no knowledge at all” ii AKNOWLEDEMENT First, I would like to express my thanks to Allah for his great help in the completion of this thesis. I would like to express my sincere thanks to my supervisor, Dr Sami Mohamed Sharif for his fruitful efforts, guidance and interest. My thanks to Dr. Ezeldeen Kamil Amin, for his advice and encouragement. I would like to express my deep thanks to all the staff in my company; Sudan Currency printing Press (SCPP) represented by the General Manager Dr. Hassan Omer A/Rahman for his great assistance and encouragement and for taking the burden of the costs of the project. My, deep thanks to the following colleagues for their kind support in the gloomy days: ¾ Mustafa Arena Computer Engineer. ¾ Al Doma Al Bager Electrical Technician. ¾ Tag Al Sir Mohammed Electrical Technician. iii اﻟﺨﻼﺻﺔ ﺗﻤﺘﻠﻚ ﺷﺮآﺔ ﻡﻄﺎﺑﻊ اﻟﺴﻮدان ﻟﻠﻌﻤﻠﺔ اﻟﻮرﻗﻴﺔ ﻋﺪد ﻡﻦ ﻡﺎآﻴﻨﺎت اﻟﻄﺒﺎﻋﺔ و هﻨﺎك ﺱﺘﺔ ﻡﻦ هﺬﻩ اﻟﻤﺎآﻴﻨﺎت ﺗﻌﺘﺒﺮ ﻗﺪیﻤﺔ ﻧﺴﺒﻴﺎ. -

International Standard ISO/IEC 10859 Was Prepared by Joint Technical Committee ISO/IEC JTC1, Information Technology, SC 26: Microprocessor System

This is a preview - click here to buy the full publication INTERNATIONAL ISO/IEC STANDARD 10859 First edition 1997-06 Information technology – 8-bit backplane interface: STEbus and mechanical core specifications for microcomputers Technologies de l'information – Interface de fond de panier 8 bits – Bus STE ISO/IEC 1997 All rights reserved. Unless otherwise specified, no part of this publication may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from the publisher. ISO/IEC Copyright Office • Case postale 56 • CH-1211 Genève 20 • Switzerland This is a preview - click here to buy the full publication – 2 – 10859 © ISO/IEC:1997 CONTENTS Page FOREWORD ................................................................................................................... 3 IEEE STANDARD FOR A 8-BIT BACKPLANE INTERFACE: STEBUS INTRODUCTION ............................................................................................................. 4 Clause 1 General .................................................................................................................... 5 2 Functional description............................................................................................... 9 3 Signal lines............................................................................................................... 10 4 Arbitration................................................................................................................ -

PC Hardware Contents

PC Hardware Contents 1 Computer hardware 1 1.1 Von Neumann architecture ...................................... 1 1.2 Sales .................................................. 1 1.3 Different systems ........................................... 2 1.3.1 Personal computer ...................................... 2 1.3.2 Mainframe computer ..................................... 3 1.3.3 Departmental computing ................................... 4 1.3.4 Supercomputer ........................................ 4 1.4 See also ................................................ 4 1.5 References ............................................... 4 1.6 External links ............................................. 4 2 Central processing unit 5 2.1 History ................................................. 5 2.1.1 Transistor and integrated circuit CPUs ............................ 6 2.1.2 Microprocessors ....................................... 7 2.2 Operation ............................................... 8 2.2.1 Fetch ............................................. 8 2.2.2 Decode ............................................ 8 2.2.3 Execute ............................................ 9 2.3 Design and implementation ...................................... 9 2.3.1 Control unit .......................................... 9 2.3.2 Arithmetic logic unit ..................................... 9 2.3.3 Integer range ......................................... 10 2.3.4 Clock rate ........................................... 10 2.3.5 Parallelism ......................................... -

ISO/IEC JTC 1/SC 25 N 4Chi008 Date: 2004-06-22

ISO/IEC JTC 1/SC 25 N 4Chi008 Date: 2004-06-22 ISO/IEC JTC 1/SC 25 INTERCONNECTION OF INFORMATION TECHNOLOGY EQUIPMENT Secretariat: Germany (DIN) DOC TYPE: Administrative TITLE: Status of projects of SC25/WG 4, Chitose, Japan, 2004-06-22/24. SOURCE: ISO/IEC JTC 1/SC 25/WG 4 Convener PROJECT: All projects of SC 25/WG 4 STATUS: Agenda ACTION ID: FYI DUE DATE: n/a REQUESTED: For information ACTION MEDIUM: Open DISTRIBUTION: ITTF, JTC 1 Secretariat P-, L-, O-Members of SC 25 No of Pages: 08 (including cover) Page 1 of 8 Status of projects of WG 4, Chitose, Japan, 2004-06-22/24 6 Project 1.25.13.01.XX - Channel Interface Specifications: Fibre Distributed Data Interface (FDDI) 6.1. Project 1.25.13.01.03 - FDDI - Part 1: Physical Layer Protocol (PHY) [ISO 9314-1:1989] no action required 6.2. Project 1.25.13.01.04 - FDDI - Part 2: Media Access Control (MAC) [ISO 9314-2:1989] - - no action required 6.3. Project 1.25.13.01.05 - FDDI - Part 3: Physical Layer Medium Dependent (PMD) [ISO/IEC 9314-3:1990] no action required 6.4. Project 1.25.13.01.06 - FDDI - Part 4: Single-Mode Fibre Physical Layer Medium Dependent (SMF-PMD) [ISO/IEC 9314-4:1999] -- no action required 6.5. Project 1.25.13.01.07 - FDDI - Part 5: Hybrid Ring Control (HRC) [ISO/IEC 9314- 5:1995] no action required 6.6. Project 1.25.13.01.08 - FDDI - Part 6: Station Management (SMT) [ISO/IEC 9314- 6:1998] no action required 6.7. -

Solution Microcap 5 Reviewed Nulling Coil Interaction Analogue Filters Alternative Balanced Amplifier Analysing Fm Noise

EW+WW exclusivea0% off virtual instruments ELECTRONICS Denmark DKr. 65.00 Germany DM 15.00 Greece Dra.950 Holland Dfl. 14 Italy L. 8000 IR £3.30 Singapore 5S12.60 WORLD Spain Pts. 750 USA $4.94 A REED BUSINESS PUBLICATION +WIRELESS WORLD SOR DISTRIBUTION September 1995£2.10 New audio power solution MicroCap 5 reviewed Nulling coil interaction Analogue filters Alternative balanced amplifier Analysing fm noise 20% discountumaudio analyser UK launch MICROMASTER LV PROGRAMMER by marl manufActurers111(10611g AMD MICROCHIP ATMEL from only £495 THE ONLY PROGRAMMERS WITH TRUE 3 VOLT SUPPORT The Only True 3V and 5V FEATURES Widest ever device support Universal Programmers including EPROMs, EEPROMs, Flash, Serial PROMs, BPROMs, ce Technology's universal programming solutions are designed with the future in mind. In PALs, MACH, MAX, MAPL, PEELs, addition totheir comprehensive, ever widening device support, they arethe only EPLDs, Microcontrollers etc. programmers ready to correctly programme and verify 3 volt devices NOW. Operating from battery or mains power, they are flexible enough for any programming needs. Correct programming and verification of 3 volt devices. The Speedmaster LV and Micromaster LV have been rigorously tested and approved by some of the most well known names in semiconductor manufacturing today, something that very few Approved by major manufacturers. programmers can claim, especially at this price level! High speed: programmes and Not only that, we give free software upgrades so you can dial up our bulletin board any time for verifies National 27C512 in under the very latest in device support. II seconds. Speedmaster LV and Micromaster LV - they're everything you'll need for programming, chip Full range of adaptors availab e for testing and ROM emulation, now and in the future. -

Portovi Personalnih Računara 50

Elektronski fakultet u Nišu Katedra za elektroniku Portovi i magistrale Student: Mentor: Vladimir Stefanović 11422 prof. dr Mile Stočev Milan Jovanović10236 Sadržaj Uvod 3 1.Magistrale 4 2.Portovi dati alfabetnim redom 36 3.Portovi personalnih računara 50 4.Poređenja i opisi PC interfejsa i portova 59 5.Hardver – mehaničke komponente 126 2 Uvod Sam rad se sastoji iz 5 dela u kojima su detaljno opisani PC portovi, magistrale, kao i razlike i sličnosti koje među njima postoje. U prvom poglavlju data je opšta podela magistrala, ukratko je opisan njihov način funkcionisanja, dati su odgovarajući standardi, generacije, a ukratko su opisane i suerbrze magistrale. U drugom poglavlju dat je alfabetni spisak portova, od kojih je većina obuhvaćena ovim radom. Treće poglavlje odnosi se na portove personalnih računara, kako Pentium tako i Apple i Mackintosh. Četvrti deo odnosi se na opisane portove i interfejse i njihovo međusobno poređenje. U ovom poglavlju date su i detaljne tabele u kojima su navedene i opisane neke od najvažnijih funkcija. I konačno, peto poglavlje se odnosi na hardver – USB portove, memorijske kartice SCSI portove. U Nišu, 03.10.2008. godine 3 1. Magistrale Prilagodljivost personalnog računara - njegova sposobnost da se proširi pomoću više vrsta interfejsa dozvoljavajući priključivanje mnogo različitih klasa dodatnih sastavnih delova i periferijskih uredjaja - bila je jedan od ključnnih razloga njegovog uspeha. U suštini, moderni PC računarski sistem malo se razlikuje od originalne IBM konstrukcije - to je skup komponenata, kako unutrašnjih tako i spoljašnjih, medjusobno povezanih pomoću elektronskih magistrala, preko kojih podaci putuju, dok se obavlja ciklus obrade koji ih pretvara od podataka ulaza u podatke izlaza. -

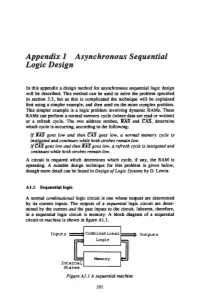

Appendix 1 Asynchronous Sequential Logic Design

Appendix 1 Asynchronous Sequential Logic Design In this appendix a design method for asynchronous sequential logic design will be described. This method can be used to solve the problem specified in section 3.3, but as this is complicated the technique will be explained first using a simpler example, and then used on the more complex problem. This simpler example is a logic problem involving dynamic RAMs. These RAMs can perform a normal memory cycle (where data are read or written) or a refresh cycle. The two address strobes, RAS and CAS", determine which cycle is occurring, according to the following: If RAS goes low and then 'CAJ goes low, a normal memory cycle is instigated and continues while both strobes remain low. If'CAJ goes low and then RAS goes low, a refresh cycle is instigated and continues while both strobes remain low. A circuit is required which determines which cycle, if any, the RAM is operating. A suitable design technique for this problem is given below, though more detail can be found in Design of Logic Systems by D. Lewin. Al.l Sequentiallogic A normal combinational logic circuit is one whose outputs are determined by its current inputs. The outputs of a sequential logic circuit are deter mined by the current and the past inputs to the circuit. Inherent, therefore, in a sequential logic circuit is memory. A block diagram of a sequential circuit or machine is shown in figure Al.l. Inputs ===! Combinational I==:> Outputs Logic Memory Internal States ~----------~ Figure Al.l A sequential machine 191 192 Micro Systems Using the STE Bus There are two forms of sequential logic machines: synchronous and asynchronous. -

Dual Buses for Industrial 110

... L r 7 L v 1 ..r 11. .. M. M `S. r , .. L. T: , r 1iu 4....L ` ../ .. r r , ...... .. sr L L ,_ i i . r r , t 1 r L. V . .. v $ . )1, ` k....L.0' .... 3 - L .0 r, .. r r 4C... --../ v S..or " L. L/ 1/4...,v J ....,0J v v r -,i` v - (,i y II -./ 10 ls . ..r .. -' v r 7 (...4 J .r á., L/ u J ..i v r ' C, t J J - s V_ M r 1/4..J '...1 J J J ,J it r ` . _+' ` i _ ! - 7y Dual buses for industrial 110 Anthony Winter of Arcom Control Systems outlines some of the cost -saving options provided by the use of VN1E/STE mixed -bus architectures It seems that the vast majority of com- a standard hus*. The bus in question is latching circuity to allow very low-cost plementary bus developments over the IEEE -1000 STEhus: a single-Eurocard (STEhus) processors to he used for adding past few years have been aimed at in- scheme which is closely matched to the intelli¢ence to an I/O subsystem. Both these creasing or optimizing overall system needs of the industrial control designer. Its approaches are embodied in Arcom's VME- throughput. Typical examples are buses to limitation' of an 8 -hit data path is. in fact. a bus hoard line. The easiest way to under- provide fast local memory accessing or benefit for industrial I/O applications, be- stand the concept is to consider a CPU hoard message passing between semi-independent cause it makes interfacing both simple and which has dual -bus interfaces. -

T10/01-274R0

T10/01-274r0 : 7 September 2001 To: T10 and T11 From: Gary S. Robinson, IR Subject: Report on ISO/IEC JTC1/SC25 and SC25/WG4 SC25 is comprised of 23 member countries as Principal members and 12 Observing (non-voting) countries. Many countries send more than one representative. The SC25 meeting is formal and is based upon procedural issues. Therefore most of this report is on the work on WG4 which is where T10 and T11 participate. The Scope of SC25 covers: Home electronics (WG1), Premises wiring (WG3), and Device interfaces (WG4). The first two groups, WG1 and WG3 were merged into SC25 from IEC and are different than the work of WG4, Device interfaces. To further complicate things, SC26, Microprocessor System was just merged into WG4. SC26 derived most of its projects from IEEE Computer Society Microprocessor Standards Committee. At this meeting WG4 went over past, current and possible future works as well as changing the name and Scope of WG4 and SC25 to reflect this merge in projects. Jurgen Märgner of IBM took over WG4 as official Convenor at this meeting. He is excellent and a real asset to this group. This SC25/WG4 report includes three documents: Attached below are the Resolutions and Action Points of WG4 (all were approved), the draft minutes, and, from the T10/11 web site, the chart T10/01-275r0 and T11/01-395v2. I have made some remarks (beginning with a ~ and using a red font). The Minutes are interesting but the Resolutions are the only official results of the meeting. -

The Hardware Book by Joakim Ögren

The Hardware Book by Joakim Ögren Visit Cable City at <http://www.cablecity.com> Welcome to the Hardware Book. Your electronic reference guide. Created and maintained by Joakim Ögren. This is the PDF (Adobe Acrobat) version. It's converted from HTML to PDF so the result may sometimes look a bit strange. Please let me know if you find any major visual errors. You will find the online version and the latest PDF version at HwB <http://www.blackdown.org/~hwb/hwb.html>. Current version 1.3 BETA. Converted from HTML 1997-11-23. Contents: Connectors Pinouts for connectors, buses etc. Connectors Top 10 Too many? These are the most common. Cables How to build serial cables and many other cables. Adapters How to build adapters. Circuits Misc circuits (active filters etc). Misc Misc information (encyclopaedia). Tables Misc tables with info. (AWG..) Download Download a WinHelp or HTML version for offline viewing. HwB-News Subscribe to the HwB Newsletter! Info about updates etc. Wanted Information I am currently looking for. About Who did this? And why? Comment Send your comments to the author. Note: This PDF file may NOT be sold in printed form. (C) Joakim Ögren 1996,1997 The Hardware Book is freely distributable but copyrighted to Joakim Ögren. It may not be modified and re-distributed without the authors permission. PRELIMINARY BETA. NOT FOR REDISTRIBUTION. BETA RELEASE Chapter 1 Connector Menu What does the information that is listed for each connector mean? See the tutorial. Buses: - ISA - (Technical) - EISA - (Technical) - PCI - (Technical) - VESA LocalBus (VLB) - (Technical) - CompactPCI - (Technical) - IndustrialPCI - SmallPCI - Miniature Card - (Technical) - NuBus - NuBus 90 - Zorro II - Zorro II/III - CPU-port (A1200) - Ramex (A1000) - Video Expansion (Amiga) - CD32 Expansion - CardBus - PC Card - PC Card ATA - PCMCIA - CompactFlash - C-bus II - SSFDC - PC-104 - Unibus Serial In/Out: The Hardware Book is freely distributable but copyrighted to Joakim Ögren. -

Bus Based Technology9 Listed Atthefootof Thepage

BUS BASED TECHNOLOGY BUS BASED TECHNOLOGY The Circuit Board Division of VERO Electronics offers products to support all internationally defined bus structures including Futurebus+, VMEbus, VME64, VME 64 Extensions, VXIbus, Compact PCI, Multibus and Multibus II, STEbus, G-64 bus and G-96 bus. The backplane range is made available in standard, modified standard and fully customised forms. In addition to the backplanes supporting these bus structures a wide range of extender boards, terminator modules and other accessories are available together with an extensive range of Microrack development systems. Customised versions of the Microracks offer an easy solution to implementation of specialised development systems. Please contact VERO Electronics for further details. MANUFACTURING STANDARDS All VERO Electronics backplanes are manufactured in accordance with quality assurance levels to BS9000, CECC 23000 and IECQ PCQ88, with systems approval in accordance with BS EN ISO9001. 9 Certificate Number Bus Based Technology Technology Bus Based Hedge End FM 14253 BS EN ISO 9001 BS 9761 BS 9762 BS 9763 CECC 23 300-004 CECC 23 300 CECC 23 200 CECC 23 100 Underwriters Laboratories NEW PRODUCTS ▲ In line with its stated policy of constant product development VERO Electronics regularly introduces new or enhanced products. New to this edition of the Product Handbook are a full range of VME2 VME64 Extensions backplanes, a 2U, 3 Slot VMEbus Microrack and CompactPCI Backplanes. CE MARKING CE Marking according to the EMC directive 89/336/EEC became effective as of 1st January 1996. According to the directive, items included in this section are considered sub-assemblies, and as such are not CE marked. -

& Wireless World

THE R ALR PR FEINAL E I EER ELECTRON., :3 & WIRELESS WORLD SEPTEMBER 1988 £1.95 World standard for h.d.tv? IEEE 488 interface for Z80 -based computers P.l.ds and logic probes Flywheel step- upswitching regulator design Alec Reeves and pulse -code modulation Dimensional approach to unified theory Denmark DKr. 63.00 Germany DM 12.10 Greece Dn. 680 Holland DEL 12.50 Italy L 6500 IR 62 86 Main Phis. 700.00 Singapore SS 11.21' Switzerland SFr. 8.50 USA 55.95 The Gould 1604 Digita orage sci oscope Give it a screen test The Gould 1604 digital storage oscilloscope has the memory and performance to tackle any role in low frequency electronics, mechanical or physiological R&D and test enviror ments. I ' With massive 10K word 10101 ,, memories on each of its 4 4. channels the 1604 can examine qt detail with expalsion factors up to 200 times, and resolution down to 5Ons. And it can do so much more. The 1604 has a built-in colour osciu,og_oPE plotter for instart print-outs of displayed traces, and the ability 1604-DicitrALOta to archive up to 50 traces in the MODEL Good) non-volatile memory pods. For 1K tAMoo even more capability, interface "(I WORD the fully programmable 1604 to 10K a a computer; or plug in the NEL CRANK waveform processor. atEN cN010{ FAA, The 1604 DSO has a wide range oN of automatic functions at an opozAn unbeatable price, and it's so easy to drive! Why not let it audition for you? IscAPPlesiL For further details of the 1604 or 0')DMs15 Atqfri,15 the 2 -channel 1602, contact: PAfiA 01-500 1000.