Appendix A: Microprocessor Data Sheets

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Microprocessors History of Computing Nouf Assaid

MICROPROCESSORS HISTORY OF COMPUTING NOUF ASSAID 1 Table of Contents Introduction 2 Brief History 2 Microprocessors 7 Instruction Set Architectures 8 Von Neumann Machine 9 Microprocessor Design 12 Superscalar 13 RISC 16 CISC 20 VLIW 23 Multiprocessor 24 Future Trends in Microprocessor Design 25 2 Introduction If we take a look around us, we would be sure to find a device that uses a microprocessor in some form or the other. Microprocessors have become a part of our daily lives and it would be difficult to imagine life without them today. From digital wrist watches, to pocket calculators, from microwaves, to cars, toys, security systems, navigation, to credit cards, microprocessors are ubiquitous. All this has been made possible by remarkable developments in semiconductor technology enabling in the last 30 years, enabling the implementation of ideas that were previously beyond the average computer architect’s grasp. In this paper, we discuss the various microprocessor technologies, starting with a brief history of computing. This is followed by an in-depth look at processor architecture, design philosophies, current design trends, RISC processors and CISC processors. Finally we discuss trends and directions in microprocessor design. Brief Historical Overview Mechanical Computers A French engineer by the name of Blaise Pascal built the first working mechanical computer. This device was made completely from gears and was operated using hand cranks. This machine was capable of simple addition and subtraction, but a few years later, a German mathematician by the name of Leibniz made a similar machine that could multiply and divide as well. After about 150 years, a mathematician at Cambridge, Charles Babbage made his Difference Engine. -

Historical Perspective and Further Reading 162.E1

2.21 Historical Perspective and Further Reading 162.e1 2.21 Historical Perspective and Further Reading Th is section surveys the history of in struction set architectures over time, and we give a short history of programming languages and compilers. ISAs include accumulator architectures, general-purpose register architectures, stack architectures, and a brief history of ARMv7 and the x86. We also review the controversial subjects of high-level-language computer architectures and reduced instruction set computer architectures. Th e history of programming languages includes Fortran, Lisp, Algol, C, Cobol, Pascal, Simula, Smalltalk, C+ + , and Java, and the history of compilers includes the key milestones and the pioneers who achieved them. Accumulator Architectures Hardware was precious in the earliest stored-program computers. Consequently, computer pioneers could not aff ord the number of registers found in today’s architectures. In fact, these architectures had a single register for arithmetic instructions. Since all operations would accumulate in one register, it was called the accumulator , and this style of instruction set is given the same name. For example, accumulator Archaic EDSAC in 1949 had a single accumulator. term for register. On-line Th e three-operand format of RISC-V suggests that a single register is at least two use of it as a synonym for registers shy of our needs. Having the accumulator as both a source operand and “register” is a fairly reliable indication that the user the destination of the operation fi lls part of the shortfall, but it still leaves us one has been around quite a operand short. Th at fi nal operand is found in memory. -

The Birth, Evolution and Future of Microprocessor

The Birth, Evolution and Future of Microprocessor Swetha Kogatam Computer Science Department San Jose State University San Jose, CA 95192 408-924-1000 [email protected] ABSTRACT timed sequence through the bus system to output devices such as The world's first microprocessor, the 4004, was co-developed by CRT Screens, networks, or printers. In some cases, the terms Busicom, a Japanese manufacturer of calculators, and Intel, a U.S. 'CPU' and 'microprocessor' are used interchangeably to denote the manufacturer of semiconductors. The basic architecture of 4004 same device. was developed in August 1969; a concrete plan for the 4004 The different ways in which microprocessors are categorized are: system was finalized in December 1969; and the first microprocessor was successfully developed in March 1971. a) CISC (Complex Instruction Set Computers) Microprocessors, which became the "technology to open up a new b) RISC (Reduced Instruction Set Computers) era," brought two outstanding impacts, "power of intelligence" and "power of computing". First, microprocessors opened up a new a) VLIW(Very Long Instruction Word Computers) "era of programming" through replacing with software, the b) Super scalar processors hardwired logic based on IC's of the former "era of logic". At the same time, microprocessors allowed young engineers access to "power of computing" for the creative development of personal 2. BIRTH OF THE MICROPROCESSOR computers and computer games, which in turn led to growth in the In 1970, Intel introduced the first dynamic RAM, which increased software industry, and paved the way to the development of high- IC memory by a factor of four. -

Professor Won Woo Ro, School of Electrical and Electronic Engineering Yonsei University the Intel® 4004 Microprocessor, Introdu

Professor Won Woo Ro, School of Electrical and Electronic Engineering Yonsei University The 1st Microprocessor The Intel® 4004 microprocessor, introduced in November 1971 An electronics revolution that changed our world. There were no customer‐ programmable microprocessors on the market before the 4004. It propelled software into the limelight as a key player in the world of digital electronics design. 4004 Microprocessor Display at New Intel Museum A Japanese calculator maker (Busicom) asked to design: A set of 12 custom logic chips for a line of programmable calculators. Marcian E. "Ted" Hoff Recognized the integrated circuit technology (of the day) had advanced enough to build a single chip, general purpose computer. Federico Faggin to turn Hoff's vision into a silicon reality. (In less than one year, Faggin and his team delivered the 4004, which was introduced in November, 1971.) The world's first microprocessor application was this Busicom calculator. (sold about 100,000 calculators.) Measuring 1/8 inch wide by 1/6 inch long, consisting of 2,300 transistors, Intel’s 4004 microprocessor had as much computing power as the first electronic computer, ENIAC. 2 inch 4004 and 12 inch Core™2 Duo wafer ENIAC, built in 1946, filled 3000‐cubic‐ feet of space and contained 18,000 vacuum tubes. The 4004 microprocessor could execute 60,000 operations per second Running frequency: 108 KHz Founders wanted to name their new company Moore Noyce. However the name sounds very much similar to “more noise”. "Only the paranoid survive". Moore received a B.S. degree in Chemistry from the University of California, Berkeley in 1950 and a Ph.D. -

6502 Introduction

6502 Introduction Philipp Koehn 18 September 2019 Philipp Koehn Computer Systems Fundamentals: 6502 Introduction 18 September 2019 1 some history Philipp Koehn Computer Systems Fundamentals: 6502 Introduction 18 September 2019 1971 2 • First microprocessor on an integrated circuit: Intel 4004 • 4-bit central processing unit, 12 bit address space (4KB) Philipp Koehn Computer Systems Fundamentals: 6502 Introduction 18 September 2019 1975 3 • MOS Technology 6502 • Dominant CPU in home computers for a decade (Atari, Apple II, Nintendo Entertainment System, Commodore PET) Philipp Koehn Computer Systems Fundamentals: 6502 Introduction 18 September 2019 1977 4 • Atari 2600 • Video game console: Pong, Pac Man, ... connected to TV Philipp Koehn Computer Systems Fundamentals: 6502 Introduction 18 September 2019 1980 5 • Commodore VIC20 • 1 MHz, 5KB RAM, BASIC, 3.5KB RAM, 176x184 3 bit color video Philipp Koehn Computer Systems Fundamentals: 6502 Introduction 18 September 2019 1982 6 • Commodore C64 • 64KB RAM, 320x200 4 bit color video Philipp Koehn Computer Systems Fundamentals: 6502 Introduction 18 September 2019 Commodore C64 7 • BASIC programming language, but serious programs written in assembly • No fancy stuff like multi-process, user accounts, virtual memory, etc. • Machine itself had no mass storage - had to buy tape drive, then floppy disk drive, machine was obsolete once hard drives came around Philipp Koehn Computer Systems Fundamentals: 6502 Introduction 18 September 2019 BASIC Demo 8 • Commands get executed (just like Python interpreter) -

Oral History Panel on the Development and Promotion of the Zilog Z8000 Microprocessor

Oral History Panel on the Development and Promotion of the Zilog Z8000 Microprocessor Moderator: Michael Slater Panelists: Federico Faggin Bernard Peuto Masatoshi Shima Ralph Ungermann Recorded: April 27, 2007 Mountain View, California CHM Reference number: X4022.2007 © 2007 Computer History Museum Michael Slater: We have with us today [April 27, 2007] four people who were involved in its [Zilog Z8000 microprocessor] creation: Ralph Ungermann, Bernard Peuto, Federico Faggin, and Masatoshi Shima. We’ve heard about the backgrounds from Shima-san, Federico and Ralph in the previous tape [oral history by the Z80 team], so we’ll start with Bernard. Could you tell us about your educational background, your experience before you came to this project? Bernard Peuto: Yes. I was born in France where I got an engineering education in radio and in computers in 1967 and 1968. I came to Berkeley to do a Ph.D. In 1969, I had my Master of Arts from Berkeley in computer science and I passed my prelim. I went back to do my military duties and then I came back and got a Ph.D. in computer science in 1974. My dissertation was about memory protection, which will come back as a subject later. As my first job I joined Amdahl Corporation from 1973 to 1976. The reason I joined Amdahl Corporation was that Charlie Bass was sharing an office with me when he was an assistant professor at Berkeley and I was a Ph.D. student and Charlie Bass had a good friend of his that was working at Fujitsu so through that connection I was hired as a computer architect at Amdahl Corporation. -

Programmable Digital Microcircuits - a Survey with Examples of Use

- 237 - PROGRAMMABLE DIGITAL MICROCIRCUITS - A SURVEY WITH EXAMPLES OF USE C. Verkerk CERN, Geneva, Switzerland 1. Introduction For most readers the title of these lecture notes will evoke microprocessors. The fixed instruction set microprocessors are however not the only programmable digital mi• crocircuits and, although a number of pages will be dedicated to them, the aim of these notes is also to draw attention to other useful microcircuits. A complete survey of programmable circuits would fill several books and a selection had therefore to be made. The choice has rather been to treat a variety of devices than to give an in- depth treatment of a particular circuit. The selected devices have all found useful ap• plications in high-energy physics, or hold promise for future use. The microprocessor is very young : just over eleven years. An advertisement, an• nouncing a new era of integrated electronics, and which appeared in the November 15, 1971 issue of Electronics News, is generally considered its birth-certificate. The adver• tisement was for the Intel 4004 and its three support chips. The history leading to this announcement merits to be recalled. Intel, then a very young company, was working on the design of a chip-set for a high-performance calculator, for and in collaboration with a Japanese firm, Busicom. One of the Intel engineers found the Busicom design of 9 different chips too complicated and tried to find a more general and programmable solu• tion. His design, the 4004 microprocessor, was finally adapted by Busicom, and after further négociation, Intel acquired marketing rights for its new invention. -

Introduction to Cpu

microprocessors and microcontrollers - sadri 1 INTRODUCTION TO CPU Mohammad Sadegh Sadri Session 2 Microprocessor Course Isfahan University of Technology Sep., Oct., 2010 microprocessors and microcontrollers - sadri 2 Agenda • Review of the first session • A tour of silicon world! • Basic definition of CPU • Von Neumann Architecture • Example: Basic ARM7 Architecture • A brief detailed explanation of ARM7 Architecture • Hardvard Architecture • Example: TMS320C25 DSP microprocessors and microcontrollers - sadri 3 Agenda (2) • History of CPUs • 4004 • TMS1000 • 8080 • Z80 • Am2901 • 8051 • PIC16 microprocessors and microcontrollers - sadri 4 Von Neumann Architecture • Same Memory • Program • Data • Single Bus microprocessors and microcontrollers - sadri 5 Sample : ARM7T CPU microprocessors and microcontrollers - sadri 6 Harvard Architecture • Separate memories for program and data microprocessors and microcontrollers - sadri 7 TMS320C25 DSP microprocessors and microcontrollers - sadri 8 Silicon Market Revenue Rank Rank Country of 2009/2008 Company (million Market share 2009 2008 origin changes $ USD) Intel 11 USA 32 410 -4.0% 14.1% Corporation Samsung 22 South Korea 17 496 +3.5% 7.6% Electronics Toshiba 33Semiconduc Japan 10 319 -6.9% 4.5% tors Texas 44 USA 9 617 -12.6% 4.2% Instruments STMicroelec 55 FranceItaly 8 510 -17.6% 3.7% tronics 68Qualcomm USA 6 409 -1.1% 2.8% 79Hynix South Korea 6 246 +3.7% 2.7% 812AMD USA 5 207 -4.6% 2.3% Renesas 96 Japan 5 153 -26.6% 2.2% Technology 10 7 Sony Japan 4 468 -35.7% 1.9% microprocessors and microcontrollers -

2.19 Historical Perspective and Further Reading 2.19

2.19 Historical Perspective and Further Reading 2.19 This section surveys the history of instruction set architraves over time, and we give a short history of programming languages and compilers. ISAs include accu- mulator architectures, general-purpose register architectures, stack architectures, and a brief history of the IA-32. We also review the controversial subjects of high- level-language computer architectures and reduced instruction set computer architectures. The history of programming languages includes Fortran, Lisp, Algol, C, Cobol, Pascal, Simula, Smalltalk, C++, and Java, and the history of com- pilers includes the key milestones and the pioneers who achieved them. Accumulator Architectures accumulator:Archaic term for register. On-line use of it Hardware was precious in the earliest stored-program computers. Consequently, as a synonym for “register” is computer pioneers could not afford the number of registers found in today’s a fairly reliable indication machines. In fact, these machines had a single register for arithmetic instructions. that the user has been Since all operations would accumulate in a single register, it was called the accu- around quite a while. mulator, and this style of instruction set is given the same name. For example, EDSAC in 1949 had a single accumulator. Eric Raymond, The New The three-operand format of MIPS suggests that a single register is at least two Hacker’s Dictionary, 1991 registers shy of our needs. Having the accumulator as both a source operand and as the destination of the operation fills part of the shortfall, but it still leaves us one operand short. That final operand is found in memory. -

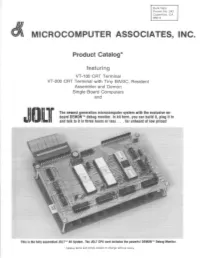

Microcomputer Associates, Inc

Bulk Rate Permit No. 243 Cupertino, CA 95014 MICROCOMPUTER ASSOCIATES, INC. Product Catalog* featuring VT-100 CRT Terminal VT -200 CRT Terminal with Tiny BASIC, Resident Assembler and Demon Single Board Computers and The newest generation microcomputer system with the exclusive on board DEMONTM debug monitor. In kit form, you can build it, plug it in JJOlT and talk to it in three hours or less ... for unheard of low prices! This is the fully assembled JOLpM 4K System. The JOLT CPU card includes the powerful DEMONTM Debug Monitor . • Catalog items and prices subject to change without notice. A READY control line provides for asynchronous operation with JOLT SYSTEM DESCRIPTION slow memory or I/O devices. The JOLT system consists of a set of modular microcomputer The address bus (AO-A 15). the data bus (00-07). the two phase boards which can be used singly or tied together to produce any clock (PIT. P2T). the reset line (·RESET). the interrupt lines ("IRZ. desired microcomputer system configuration. The minimum system AND *NMI). and the ready line (ROY) are all available at the edge is one CPU board. which alone constitutes a viable computer sys connector of the CPU card. The loading restrictions should be con tem complete with central processor. 1/0. interrupts. timer. read sidered when using the signal lines driven by the CPU for external write memory. and a complete software debug monitor in read system expansion. A more detailed description of the CPU inputs and outputs may only-memory. be found in the MCS6500 hardware manual available from MOS Additional boards in the JOLT system include a 4 K byte RAM. -

Hardware Goal: a Motorola 6809 Processor Running on a Board

MC6809/6502 ATX/6U Computer aka COLOSSUS Hardware Goal: A Motorola 6809 processor running on a board which will mount in an ATX case or in a 6U card cage. Board dimensions are 160mm x 233.35mm (6.3” x 9.2”). A Propellor subsystem provides a VGA terminal and PS/2[?] keyboard interface. Timer, parallel ports, and a separate serial port are included. The design is based on the original “6x0x” board which operates as an ECB peripheral. A second CPU socket will be provided for either a 6502 or 6802 CPU chip. This chip may be installed and operated if the 6809 is removed. Software Goal: It looks like NitrOS9 level 2 is the most powerful s/w we could bring up on this board; but a paged MMU is required. This software goal is now driving the hardware design effort. Design Strategy: Recently the project was divided into smaller, more manageable pieces. A master schematic sheet now indexes close to a dozen independent subsystems. If individual subsystems can be handled by persons with expertise in a particular area, this will save passing around one huge schematic. Integration of an update to one subsystem which does not affect other parts of the system will be as simple as replacing one subsystem schematic with an updated version. Kicad facilitates this with the “schematic hierarchy,” and this looks to ease some of the integration headaches. Technical Stuff CPU-1: The design is for a 2Mhz MC68B09 chip. Note this is not the 6809E. The -E suffix chip is electrically different. -

Computer Architectures an Overview

Computer Architectures An Overview PDF generated using the open source mwlib toolkit. See http://code.pediapress.com/ for more information. PDF generated at: Sat, 25 Feb 2012 22:35:32 UTC Contents Articles Microarchitecture 1 x86 7 PowerPC 23 IBM POWER 33 MIPS architecture 39 SPARC 57 ARM architecture 65 DEC Alpha 80 AlphaStation 92 AlphaServer 95 Very long instruction word 103 Instruction-level parallelism 107 Explicitly parallel instruction computing 108 References Article Sources and Contributors 111 Image Sources, Licenses and Contributors 113 Article Licenses License 114 Microarchitecture 1 Microarchitecture In computer engineering, microarchitecture (sometimes abbreviated to µarch or uarch), also called computer organization, is the way a given instruction set architecture (ISA) is implemented on a processor. A given ISA may be implemented with different microarchitectures.[1] Implementations might vary due to different goals of a given design or due to shifts in technology.[2] Computer architecture is the combination of microarchitecture and instruction set design. Relation to instruction set architecture The ISA is roughly the same as the programming model of a processor as seen by an assembly language programmer or compiler writer. The ISA includes the execution model, processor registers, address and data formats among other things. The Intel Core microarchitecture microarchitecture includes the constituent parts of the processor and how these interconnect and interoperate to implement the ISA. The microarchitecture of a machine is usually represented as (more or less detailed) diagrams that describe the interconnections of the various microarchitectural elements of the machine, which may be everything from single gates and registers, to complete arithmetic logic units (ALU)s and even larger elements.