The Birth, Evolution and Future of Microprocessor

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Floating-Point Package for Intel 8008 and 8080 Microprocessors

UCRL-51940 FLOATING-POINT PACKAGE FOR INTEL 8008 AND 8080 MICROPROCESSORS Michael D. Maples October 24, 1975 Prepared for U.S. Energy Research& Development Administration under contract No. W-7405-Eng-48 I_AV~=IENCE I_IVEFIMORE I.ABOFIATOFIY University ol Calilomia ~ Livermore ~ NOTICE .sponsored by tht: United $~ates G~ven~menl.Neilhe~ the United States nor the United ~tates I’:n,~rgy of their employees,IIOr lilly of their eorltl’ilctclrs~ warranty~ express t~r implied, or asstltlleS ~t]y legld liability or responsihilit y fnr the accuracy, apparatus, product or ])rc)eess disclosed, represents that its rise would IIt~l illl’r liege privlttely-owned rights." Printed in the United States of America Avai.] able from National Technical. information Service U.S. Department of Commerce 5285 Port Royal Road Springfield, Virginia 22151 Price: Printed Copy $ *; Microfiche $2.25 NTIS ""Pages _Sellin_.g Price 1-50 $4.00 51-150 $5.45 151-325 $7.60 326-500 $10.60 501.-1000 $13.60 DISCI.AlMBR This documeut was prepared as an account of work sponsored by an agency of the United States Gnvernment.Neither the United States Governmentnor the University of California nor any of their employees,makes any warranty, express or implied, or assumesany legal liability or responsibility for the accuracy, complete.aess, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use wouldnot infrioge privately ownedrights. Refarenceherein to any specific commercialproduct, process, or service by trade name, trademark, manufacturer, or otherwise, does not necessarily constitute or imply its endorsement, recommendation,or favoring by the United States Govermnentor the University of California. -

Build a Swtpc 6800

Southwest Technical Products Corporation 6800 Computer System The Southwest Technical Products 6800 computer system is based upon the Motorola MC6800 microprocessor unit (MPU) and its matching support devices. The 6800 system was chosen for our computer because this set of parts is currently in our opinion the "Benchmark Family" for microprocessor computer systems. It makes it possible for us to provide you with an outstanding computer system having a minimum of parts, but with outstanding versatility and ease of use. In addition to the outstanding hardware system, the Motorola 6800 has without question the most complete set of documentation yet made available for a microprocessor system. The 714 page Applications Manual, for example, contains material on programming techniques, system organization, input/output techniques, hardware characteristics, peripheral control techniques, and more. Also available is a Programmers Manual which details the various types of software available for the system and instructions for programming and using the unique interface system that is part of the 6800 system. The M6800 family of parts minimizes the number of, required components and support parts, provides extremely simple interfacing to external devices and has outstanding documentation. The MC6800 is an eight-bit parallel microprocessor with addressing capability of up to 45,536 words (BYTES) of data. The system is TTL compatible requiring only a single fine-volt power supply. All devices and memory in the 6800 computer family are connected to an 8-bit bi-directional data bus. In addition to this a 16-bit address bus is provided to specify memory location. This later bus is also used as a tool to specify the particular input/ output device to be selected when the 6800 family interface devices are used. -

When Is a Microprocessor Not a Microprocessor? the Industrial Construction of Semiconductor Innovation I

Ross Bassett When is a Microprocessor not a Microprocessor? The Industrial Construction of Semiconductor Innovation I In the early 1990s an integrated circuit first made in 1969 and thus ante dating by two years the chip typically seen as the first microprocessor (Intel's 4004), became a microprocessor for the first time. The stimulus for this piece ofindustrial alchemy was a patent fight. A microprocessor patent had been issued to Texas Instruments, and companies faced with patent infringement lawsuits were looking for prior art with which to challenge it. 2 This old integrated circuit, but new microprocessor, was the ALl, designed by Lee Boysel and used in computers built by his start-up, Four-Phase Systems, established in 1968. In its 1990s reincarnation a demonstration system was built showing that the ALI could have oper ated according to the classic microprocessor model, with ROM (Read Only Memory), RAM (Random Access Memory), and I/O (Input/ Output) forming a basic computer. The operative words here are could have, for it was never used in that configuration during its normal life time. Instead it was used as one-third of a 24-bit CPU (Central Processing Unit) for a series ofcomputers built by Four-Phase.3 Examining the ALl through the lenses of the history of technology and business history puts Intel's microprocessor work into a different per spective. The differences between Four-Phase's and Intel's work were industrially constructed; they owed much to the different industries each saw itselfin.4 While putting a substantial part ofa central processing unit on a chip was not a discrete invention for Four-Phase or the computer industry, it was in the semiconductor industry. -

Exorciser USER's GUIDE

M6809EXOR(D1) ®MOTOROLA M6809 EXORciser User's Guide MICROSYSTEMS M6809EXOR (Dl} SEPTEMBER 1979 M6809 EXORciser USER'S GUIDE The information in this document has been carefully checked and is believed to be entirely reliable. However, no res pons i bi 1ity is assumed for inaccuracies. Furthermore, Motorola reserves the right to make changes to any products herein to improve reliability, function, or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. EXORciser®, EXORdisk, and EXbug are trademarks of Motorola Inc. First Edition ©Copyright 1979 by Motorola Inc. TABLE OF CONTENTS Page CHAPTER 1 GENERAL INFORMATION 1.1 INTRODUCTION 1-1 1.2 FEATURES 1-1 1.3 SPECIFICATIONS 1-2 1.4 EQUIPMENT SUPPLIED 1-2 1.5 GENERAL DESCRIPTION 1-3 1.5.1 EXORciser Memory Parity 1-3 1.5.2 Dual Map Concepts 1-5 1.5.3 Second level Interrupt Feature 1-7 1.5.4 Dynamic System Bus 1-10 CHAPTER 2 INSTALLATION INSTRUCTIONS AND HARDWARE PREPARATION 2.1 INTRODUCTION 2-1 2.2 UNPACKING INSTRUCTIONS 2-1 2.3 INSPECTION 2-1 2.4 INSTALLATION INSTRUCTIONS 2-1 2.5 DATA TERMINAL SELECTION AND CONNECTIONS 2-2 2.5.1 RS-232C Interconnections 2-2 2.5.2 20mA Current loop Interconnections 2-2 2.6 PREPARATION OF SYSTEM MODULES 2-2 CHAPTER 3 OPERATING INSTRUCTIONS 3.1 INTRODUCTION 3-1 3.2 SWITCHES AND INDICATORS 3-1 3.2.1 Front Panel Switches and Indicators 3-1 3.2.2 Switches on the DEbug Module 3-2 3.3 INITIALIZATION 3-3 3.3.1 -

Lecture Note 1

EE586 VLSI Design Partha Pande School of EECS Washington State University [email protected] Lecture 1 (Introduction) Why is designing digital ICs different today than it was before? Will it change in future? The First Computer The Babbage Difference Engine (1832) 25,000 parts cost: £17,470 ENIAC - The first electronic computer (1946) The Transistor Revolution First transistor Bell Labs, 1948 The First Integrated Circuits Bipolar logic 1960’s ECL 3-input Gate Motorola 1966 Intel 4004 Micro-Processor 1971 1000 transistors 1 MHz operation Intel Pentium (IV) microprocessor Moore’s Law In 1965, Gordon Moore noted that the number of transistors on a chip doubled every 18 to 24 months. He made a prediction that semiconductor technology will double its effectiveness every 18 months Moore’s Law 16 15 14 13 12 11 10 9 8 7 6 OF THE NUMBER OF 2 5 4 LOG 3 2 1 COMPONENTS PER INTEGRATED FUNCTION 0 1959 1960 1961 1962 1963 1964 1965 1966 1967 1968 1969 1970 1971 1972 1973 1974 1975 Electronics, April 19, 1965. Evolution in Complexity Transistor Counts 1 Billion K Transistors 1,000,000 100,000 Pentium® III 10,000 Pentium® II Pentium® Pro 1,000 Pentium® i486 100 i386 80286 10 8086 Source: Intel 1 1975 1980 1985 1990 1995 2000 2005 2010 Projected Courtesy, Intel Moore’s law in Microprocessors 1000 2X growth in 1.96 years! 100 10 P6 Pentium® proc 1 486 386 0.1 286 Transistors (MT) Transistors 8086 Transistors8085 on Lead Microprocessors double every 2 years 0.01 8080 8008 4004 0.001 1970 1980 1990 2000 2010 Year Courtesy, Intel Die Size Growth 100 P6 -

Download/Face- Modules/Documents/Face-Modules-Hw-Specifications.Pdf

I PC H “ CompuLab Ltd. Revision 1.2 December 2013 Legal Notice © 2013 CompuLab Ltd. All Rights Reserved. No part of this document may be photocopied, reproduced, stored in a retrieval system, or transmitted, in any form or by any means whether, electronic, mechanical, or otherwise without the prior written permission of CompuLab Ltd. No warranty of accuracy is given concerning the contents of the information contained in this publication. To the extent permitted by law no liability (including liability to any person by reason of negligence) will be accepted by CompuLab Ltd., its subsidiaries or employees for any direct or indirect loss or damage caused by omissions from or inaccuracies in this document. CompuLab Ltd. reserves the right to change details in this publication without notice. Product and company names herein may be the trademarks of their respective owners. CompuLab Ltd. 17 HaYetsira St., Yokneam Elite 20692, P.O.B 687 ISRAEL Tel: +972-4-8290100 http://www.compulab.co.il http://fit-pc.com/web/ Fax: +972-4-8325251 CompuLab Ltd. Intense PC Hardware Specification Page 2 of 74 Revision History Revision Engineer Revision Changes 1.0 Maxim Birger Initial public release 1.1 Maxim Birger Memory Interface updated Super-IO Controller peripheral section added RS232 serial com port info added 1.2 Maxim Birger HDMI Block Diagram updated DP Block Diagram updated CompuLab Ltd. Intense PC Hardware Specification Page 3 of 74 Table of Contents Legal Notice .................................................................................................................................................. -

Intel 8080 Datasheet

infel.. 8080A/8080A-1/8080A-2 8-BIT N-CHANNEL MICROPROCESSOR • TTL Drive Capability • Decimal, Binary, and Double Precision • 2,..,s (-1:1.3,..,s, -2:1.5 ,..,s) Instruction Arithmetic Cycle • Ability to Provide Priority Vectored • Powerful Problem Solving Instruction Interrupts Set • 512 Directly Addressed 110 Ports 6 General Purpose Registers and an Available In EXPRESS • Accumulator • - Standard Temperature Range 16-Blt Program Counter for Directly Available In 4Q-Lead Cerdlp and Plastic • Addressing up to 64K Bytes of Memory • Packages 16-Blt Stack Pointer and Stack (See Packaging Spec. Order #231369) • Manipulation Instructions for Rapid Switching of the Program Environment • The Intel 8080A is a complete 8-bit parallel central processing unit (CPU). It is fabricated on a single LSI chip using Intel's n-channel silicon gate MOS process. This offers the user a high performance solution to control and processing applications. The 8080A contains 6 8-bit general purpose working registers and an accumulator. The 6 general purpose registers may be addressed individually or in pairs providing both single and double precision operators. Arithmetic and logical instructions set or reset 4 testable flags. A fifth flag provides decimal arithmetic opera tion. The 8080A has an external stack feature wherein any portion of memory may be used as a last in/first out stack to store/retrieve the contents of the accumulator, flags, program counter, and all of the 6 general purpose registers. The 16-bit stack pointer controls the addressing of this external stack. This stack gives the 8080A the ability to easily handle multiple level priority interrupts by rapidly storing and restoring processor status. -

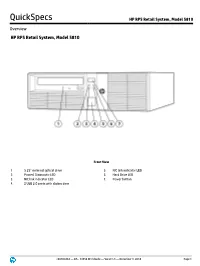

HP RP5810 Retail System, Model 5810

QuickSpecs HP RP5 Retail System, Model 5810 Overview HP RP5 Retail System, Model 5810 Front View 1. 5.25” external optical drive 5. NIC link indicator LED 2. Power/ Diagnostic LED 6. Hard Drive LED 3. NIC link indicator LED 7. Power button 4. 2 USB 2.0 ports with sliding door c04304464 — DA - 14956 Worldwide — Version 8 — December 8, 2014 Page 1 QuickSpecs HP RP5 Retail System, Model 5810 Overview Rear View 1. 24 Volt USB + PWR port 10. PS/2 keyboard port 2. Two (2) Full-Height Slots* 11. VGA port 3. RS232 serial COM3 12. 3 USB 2.0 ports 4. RJ-45 LAN jack 13. 2 USB 3.0 ports 5. RS232 serial (power configurable) COM1 port 14. RS232 serial (power configurable) COM2 port 6. PS/2 mouse port 15. DisplayPort 7. 240W EPA – Active PFC power supply (no line 16. RJ12 cash drawer port switching required) 8. Line in audio jack 17. One (1) PCIe x16 Slot (wired as x16)** – shown is optional three (3) port 12 Volt USB +Power Card 9. Line out audio jack 18. One (1) PCIe x16 Slot (wired as x4)** – shown is optional three (3) port 12 Volt USB + Power Card * Can be configured either as two (2) PCI x1 or two (2) PCIe x1 Full-Height slots. Shown is optional 2 Port RS232 serial (power configurable) Card, COM4 port (left) and COM3 port (right port). **A variety of cards are available to populate slots, dependant on riser choice and connectors utilized. For full details, please contact your HP sales representative for configuration choices. -

GPU Developments 2018

GPU Developments 2018 2018 GPU Developments 2018 © Copyright Jon Peddie Research 2019. All rights reserved. Reproduction in whole or in part is prohibited without written permission from Jon Peddie Research. This report is the property of Jon Peddie Research (JPR) and made available to a restricted number of clients only upon these terms and conditions. Agreement not to copy or disclose. This report and all future reports or other materials provided by JPR pursuant to this subscription (collectively, “Reports”) are protected by: (i) federal copyright, pursuant to the Copyright Act of 1976; and (ii) the nondisclosure provisions set forth immediately following. License, exclusive use, and agreement not to disclose. Reports are the trade secret property exclusively of JPR and are made available to a restricted number of clients, for their exclusive use and only upon the following terms and conditions. JPR grants site-wide license to read and utilize the information in the Reports, exclusively to the initial subscriber to the Reports, its subsidiaries, divisions, and employees (collectively, “Subscriber”). The Reports shall, at all times, be treated by Subscriber as proprietary and confidential documents, for internal use only. Subscriber agrees that it will not reproduce for or share any of the material in the Reports (“Material”) with any entity or individual other than Subscriber (“Shared Third Party”) (collectively, “Share” or “Sharing”), without the advance written permission of JPR. Subscriber shall be liable for any breach of this agreement and shall be subject to cancellation of its subscription to Reports. Without limiting this liability, Subscriber shall be liable for any damages suffered by JPR as a result of any Sharing of any Material, without advance written permission of JPR. -

Computer Organization and Architecture Designing for Performance Ninth Edition

COMPUTER ORGANIZATION AND ARCHITECTURE DESIGNING FOR PERFORMANCE NINTH EDITION William Stallings Boston Columbus Indianapolis New York San Francisco Upper Saddle River Amsterdam Cape Town Dubai London Madrid Milan Munich Paris Montréal Toronto Delhi Mexico City São Paulo Sydney Hong Kong Seoul Singapore Taipei Tokyo Editorial Director: Marcia Horton Designer: Bruce Kenselaar Executive Editor: Tracy Dunkelberger Manager, Visual Research: Karen Sanatar Associate Editor: Carole Snyder Manager, Rights and Permissions: Mike Joyce Director of Marketing: Patrice Jones Text Permission Coordinator: Jen Roach Marketing Manager: Yez Alayan Cover Art: Charles Bowman/Robert Harding Marketing Coordinator: Kathryn Ferranti Lead Media Project Manager: Daniel Sandin Marketing Assistant: Emma Snider Full-Service Project Management: Shiny Rajesh/ Director of Production: Vince O’Brien Integra Software Services Pvt. Ltd. Managing Editor: Jeff Holcomb Composition: Integra Software Services Pvt. Ltd. Production Project Manager: Kayla Smith-Tarbox Printer/Binder: Edward Brothers Production Editor: Pat Brown Cover Printer: Lehigh-Phoenix Color/Hagerstown Manufacturing Buyer: Pat Brown Text Font: Times Ten-Roman Creative Director: Jayne Conte Credits: Figure 2.14: reprinted with permission from The Computer Language Company, Inc. Figure 17.10: Buyya, Rajkumar, High-Performance Cluster Computing: Architectures and Systems, Vol I, 1st edition, ©1999. Reprinted and Electronically reproduced by permission of Pearson Education, Inc. Upper Saddle River, New Jersey, Figure 17.11: Reprinted with permission from Ethernet Alliance. Credits and acknowledgments borrowed from other sources and reproduced, with permission, in this textbook appear on the appropriate page within text. Copyright © 2013, 2010, 2006 by Pearson Education, Inc., publishing as Prentice Hall. All rights reserved. Manufactured in the United States of America. -

Programming Model, Address Mode, HC12 Hardware Introduction

EEL 4744C: Microprocessor Applications Lecture 2 Programming Model, Address Mode, HC12 Hardware Introduction Dr. Tao Li 1 Reading Assignment • Microcontrollers and Microcomputers: Chapter 3, Chapter 4 • Software and Hardware Engineering: Chapter 2 Or • Software and Hardware Engineering: Chapter 4 Plus • CPU12 Reference Manual: Chapter 3 • M68HC12B Family Data Sheet: Chapter 1, 2, 3, 4 Dr. Tao Li 2 EEL 4744C: Microprocessor Applications Lecture 2 Part 1 CPU Registers and Control Codes Dr. Tao Li 3 CPU Registers • Accumulators – Registers that accumulate answers, e.g. the A Register – Can work simultaneously as the source register for one operand and the destination register for ALU operations • General-purpose registers – Registers that hold data, work as source and destination register for data transfers and source for ALU operations • Doubled registers – An N-bit CPU in general uses N-bit data registers – Sometimes 2 of the N-bit registers are used together to double the number of bits, thus “doubled” registers Dr. Tao Li 4 CPU Registers (2) • Pointer registers – Registers that address memory by pointing to specific memory locations that hold the needed data – Contain memory addresses (without offset) • Stack pointer registers – Pointer registers dedicated to variable data and return address storage in subroutine calls • Index registers – Also used to address memory – An effective memory address is found by adding an offset to the content of the involved index register Dr. Tao Li 5 CPU Registers (3) • Segment registers – In some architectures, memory addressing requires that the physical address be specified in 2 parts • Segment part: specifies a memory page • Offset part: specifies a particular place in the page • Condition code registers – Also called flag or status registers – Hold condition code bits generated when instructions are executed, e.g. -

45-Year CPU Evolution: One Law and Two Equations

45-year CPU evolution: one law and two equations Daniel Etiemble LRI-CNRS University Paris Sud Orsay, France [email protected] Abstract— Moore’s law and two equations allow to explain the a) IC is the instruction count. main trends of CPU evolution since MOS technologies have been b) CPI is the clock cycles per instruction and IPC = 1/CPI is the used to implement microprocessors. Instruction count per clock cycle. c) Tc is the clock cycle time and F=1/Tc is the clock frequency. Keywords—Moore’s law, execution time, CM0S power dissipation. The Power dissipation of CMOS circuits is the second I. INTRODUCTION equation (2). CMOS power dissipation is decomposed into static and dynamic powers. For dynamic power, Vdd is the power A new era started when MOS technologies were used to supply, F is the clock frequency, ΣCi is the sum of gate and build microprocessors. After pMOS (Intel 4004 in 1971) and interconnection capacitances and α is the average percentage of nMOS (Intel 8080 in 1974), CMOS became quickly the leading switching capacitances: α is the activity factor of the overall technology, used by Intel since 1985 with 80386 CPU. circuit MOS technologies obey an empirical law, stated in 1965 and 2 Pd = Pdstatic + α x ΣCi x Vdd x F (2) known as Moore’s law: the number of transistors integrated on a chip doubles every N months. Fig. 1 presents the evolution for II. CONSEQUENCES OF MOORE LAW DRAM memories, processors (MPU) and three types of read- only memories [1]. The growth rate decreases with years, from A.