Download/Face- Modules/Documents/Face-Modules-Hw-Specifications.Pdf

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Computer on Module

Module COM Carte réceptrice Computer On Module Réduction du coût de votre développement Installation, maintenance et mise à jour simplifiées Diminution des risques inhérent à un développement Disponibilité sous 30 jours de votre produit Applications : • Terminaux de vente & Affichage Dynamique • Vidéosurveillance numérique • Médical • IP TV • Appareils de mesure & tests en ligne • M2M • Terminaux de jeux • Géolocalisation • Automatisation industrielle & contrôle de procédés • Serveurs informatiques • Militaire & Police Notre service ODM DTD Les règles générales du service ODM DTD : Le fabricant s'engage à gérer l'achat et le stockage des composants Le service ODM DTD n'est assuré que dans le cadre de l'utilisation courant qui permettent la fabrication d'un Computer On Module. Dans des modules AAEON aux formats : ETX, XTX and COM Express le cas où la fabrication de la carte réceptrice requière des composants modules. spécifiques ou sujet à des minima de quantité en commande (MOQ), Les frais d'études pour la réalisation de la carte réceptrice sont le client s'engage à acheter et à consigner ces composants chez basés sur les spécifications arrêtées avec le client à la signature de Equipements Scientifiques. la commande. Toute modifications de ces spécifications par la suite pourra emmener des frais supplémentaires à la charge du client. La Définitions 1 jour fourniture d'une carte réceptrice sous 30 jours ouvrés est incluse dans les frais d'études. Les corrections nécessaires après le test du prototype Etude du circuit 5 jours sont prises en charge par le service ODM DTD. Ces corrections seront Routage du PCB 9 jours vérifiées par le client avant le démarrage de la pré-série. -

Industrial Platform Service

latform P ndustrial I ervice S s stic ‧Manufa gi Ver. 211A ign cturing‧Lo es ‧D Consulting‧Product Portwell, Inc. was founded in 1993 and entered the Industrial Computing Platform Providers (IACPP), but also an associate PC market in 1995 by developing single-board computers. member of Intel® Embedded and Communications Alliance Today, our continuous development of leading-edge products (ECA), as well as Advanced Telecom Computing Architecture has resulted in strong growth in market share and revenue, a (ATCA) and an executive member of PCI Industrial Computer fi rm place on the Taipei stock exchange (TAISDAQ), and has Manufacturing group (PICMG). established Portwell a major worldwide supplier of specialty Portwell, Inc. has worldwide operation in the U.S.A., Taiwan, computing application platforms and services. Portwell, Inc. Japan, China, Netherland, United Kingdom, and India. is not only a member of the selected group of Intel® Applied Portwell Engine (PE) Building Whether you are working on a computer board or turnkey standards such as ISO 9001/14000/13485, OHSAS and system, Portwell is the perfect partner to help you deliver your RoHS, customers have taken advantage of our dedicated and products to market on time as well as maintain longevity of sophisticated engineering resource to satisfy their requirements product life cycle. With 18 years experience in the design and for the design, manufacturing and logistics of application- manufacture of specialty computer boards and systems, Portwell specifi c computer boards, customized computer chassis, and not only provides a one-stop resource for off-the-shelf products, specifi c computer system confi gurations. -

Dell Optiplex 7060 Desktop Setup

OptiPlex 7060 Small Form Factor Setup and specifications guide Regulatory Model: D11S Regulatory Type: D11S004 Notes, cautions, and warnings NOTE: A NOTE indicates important information that helps you make better use of your product. CAUTION: A CAUTION indicates either potential damage to hardware or loss of data and tells you how to avoid the problem. WARNING: A WARNING indicates a potential for property damage, personal injury, or death. © 2018 Dell Inc. or its subsidiaries. All rights reserved. Dell, EMC, and other trademarks are trademarks of Dell Inc. or its subsidiaries. Other trademarks may be trademarks of their respective owners. 2018 - 06 Rev. A01 Contents 1 Set up your computer.....................................................................................................................................5 2 Chassis.......................................................................................................................................................... 8 Front view........................................................................................................................................................................... 8 Back view............................................................................................................................................................................9 3 System specifications.................................................................................................................................. 10 Chipset...............................................................................................................................................................................10 -

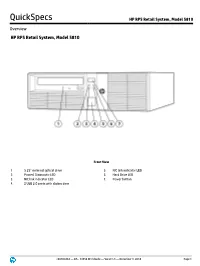

HP RP5810 Retail System, Model 5810

QuickSpecs HP RP5 Retail System, Model 5810 Overview HP RP5 Retail System, Model 5810 Front View 1. 5.25” external optical drive 5. NIC link indicator LED 2. Power/ Diagnostic LED 6. Hard Drive LED 3. NIC link indicator LED 7. Power button 4. 2 USB 2.0 ports with sliding door c04304464 — DA - 14956 Worldwide — Version 8 — December 8, 2014 Page 1 QuickSpecs HP RP5 Retail System, Model 5810 Overview Rear View 1. 24 Volt USB + PWR port 10. PS/2 keyboard port 2. Two (2) Full-Height Slots* 11. VGA port 3. RS232 serial COM3 12. 3 USB 2.0 ports 4. RJ-45 LAN jack 13. 2 USB 3.0 ports 5. RS232 serial (power configurable) COM1 port 14. RS232 serial (power configurable) COM2 port 6. PS/2 mouse port 15. DisplayPort 7. 240W EPA – Active PFC power supply (no line 16. RJ12 cash drawer port switching required) 8. Line in audio jack 17. One (1) PCIe x16 Slot (wired as x16)** – shown is optional three (3) port 12 Volt USB +Power Card 9. Line out audio jack 18. One (1) PCIe x16 Slot (wired as x4)** – shown is optional three (3) port 12 Volt USB + Power Card * Can be configured either as two (2) PCI x1 or two (2) PCIe x1 Full-Height slots. Shown is optional 2 Port RS232 serial (power configurable) Card, COM4 port (left) and COM3 port (right port). **A variety of cards are available to populate slots, dependant on riser choice and connectors utilized. For full details, please contact your HP sales representative for configuration choices. -

GPU Developments 2018

GPU Developments 2018 2018 GPU Developments 2018 © Copyright Jon Peddie Research 2019. All rights reserved. Reproduction in whole or in part is prohibited without written permission from Jon Peddie Research. This report is the property of Jon Peddie Research (JPR) and made available to a restricted number of clients only upon these terms and conditions. Agreement not to copy or disclose. This report and all future reports or other materials provided by JPR pursuant to this subscription (collectively, “Reports”) are protected by: (i) federal copyright, pursuant to the Copyright Act of 1976; and (ii) the nondisclosure provisions set forth immediately following. License, exclusive use, and agreement not to disclose. Reports are the trade secret property exclusively of JPR and are made available to a restricted number of clients, for their exclusive use and only upon the following terms and conditions. JPR grants site-wide license to read and utilize the information in the Reports, exclusively to the initial subscriber to the Reports, its subsidiaries, divisions, and employees (collectively, “Subscriber”). The Reports shall, at all times, be treated by Subscriber as proprietary and confidential documents, for internal use only. Subscriber agrees that it will not reproduce for or share any of the material in the Reports (“Material”) with any entity or individual other than Subscriber (“Shared Third Party”) (collectively, “Share” or “Sharing”), without the advance written permission of JPR. Subscriber shall be liable for any breach of this agreement and shall be subject to cancellation of its subscription to Reports. Without limiting this liability, Subscriber shall be liable for any damages suffered by JPR as a result of any Sharing of any Material, without advance written permission of JPR. -

Focus on Your Core Competency the COM Express Standard

Computer-On-Modules Focus on your Core Competency The COM Express Standard – A Computer-On-Module (COM) provides a convenient solution for Adaptable to Your Specific Needs OEMs that need computing functionality but are not interested in COM Express was developed and is maintained by PICMG investing the time and resources into designing a single board (PCI Industrial Computer Manufacturers Group). COM computer. There are several COM standards, one of the more Express was released in the summer of 2005 and is the popular being COM Express (also referred to as COM.0). COM most widely used COM standard. The standard defines the Express modules contain the CPU, memory, common peripherals physical size, interconnect, and thermal interface for a COM. (USB, SATA) and an I/O interface (PCI and PCI Express). OEMs that The original COM Express specification was written to use COM Express modules design a carrier board that contains any support peripherals that were available at the time of release required I/O interfaces not found on the COM Express module as – including USB 2.0, SATA, PATA, Ethernet, VGA, LVDS, well as connectors for external I/O. A COM based solution allows SDVO, PCI, and PCI Express Gen 1. Several pinout types an OEM to focus on their core competency and not the design and were defined by PICMG with each one having a specific maintenance of a single board computer. combination of peripherals, expansion interfaces and connector layout. The most widely used COM Express A COM Express based solution with a custom carrier board offers module is a type 2, followed by type 1. -

Focus on Your Core Competency the COM Express Standard

Computer-On-Modules Focus on your Core Competency The COM Express Standard – A Computer-On-Module (COM) provides a convenient solution for Adaptable to Your Specific Needs OEMs that need computing functionality but are not interested in COM Express was developed and is maintained by PICMG investing the time and resources into designing a single board (PCI Industrial Computer Manufacturers Group). COM computer. There are several COM standards, one of the more Express was released in the summer of 2005 and is the popular being COM Express (also referred to as COM.0). COM most widely used COM standard. The standard defines the Express modules contain the CPU, memory, common peripherals physical size, interconnect, and thermal interface for a COM. (USB, SATA) and an I/O interface (PCI and PCI Express). OEMs that The original COM Express specification was written to use COM Express modules design a carrier board that contains any support peripherals that were available at the time of release required I/O interfaces not found on the COM Express module as – including USB 2.0, SATA, PATA, Ethernet, VGA, LVDS, well as connectors for external I/O. A COM based solution allows SDVO, PCI, and PCI Express Gen 1. Several pinout types an OEM to focus on their core competency and not the design and were defined by PICMG with each one having a specific maintenance of a single board computer. combination of peripherals, expansion interfaces and connector layout. The most widely used COM Express A COM Express based solution with a custom carrier board offers module is a type 2, followed by type 1. -

The Birth, Evolution and Future of Microprocessor

The Birth, Evolution and Future of Microprocessor Swetha Kogatam Computer Science Department San Jose State University San Jose, CA 95192 408-924-1000 [email protected] ABSTRACT timed sequence through the bus system to output devices such as The world's first microprocessor, the 4004, was co-developed by CRT Screens, networks, or printers. In some cases, the terms Busicom, a Japanese manufacturer of calculators, and Intel, a U.S. 'CPU' and 'microprocessor' are used interchangeably to denote the manufacturer of semiconductors. The basic architecture of 4004 same device. was developed in August 1969; a concrete plan for the 4004 The different ways in which microprocessors are categorized are: system was finalized in December 1969; and the first microprocessor was successfully developed in March 1971. a) CISC (Complex Instruction Set Computers) Microprocessors, which became the "technology to open up a new b) RISC (Reduced Instruction Set Computers) era," brought two outstanding impacts, "power of intelligence" and "power of computing". First, microprocessors opened up a new a) VLIW(Very Long Instruction Word Computers) "era of programming" through replacing with software, the b) Super scalar processors hardwired logic based on IC's of the former "era of logic". At the same time, microprocessors allowed young engineers access to "power of computing" for the creative development of personal 2. BIRTH OF THE MICROPROCESSOR computers and computer games, which in turn led to growth in the In 1970, Intel introduced the first dynamic RAM, which increased software industry, and paved the way to the development of high- IC memory by a factor of four. -

Opengl Driver Intel Download Windows 7 OPENGL INTEL HD GRAPHICS 4000 TREIBER WINDOWS 7

opengl driver intel download windows 7 OPENGL INTEL HD GRAPHICS 4000 TREIBER WINDOWS 7. But here on windows, the intel graphics control panel clearly states that the supported version is 4.0. This package contains intel hd, hd 4000 graphics driver and is supported on latitude systems that run windows 7, windows 8.1 and windows 10 64-bit operating systems. Ask question asked questions for cs6, windows 10. This package contains windows 10 driver to address intel advisory. Would be compatible with the intel hd graphics 3000 video. AMD Radeon Pro WX 3200 Laptop GPU, Benchmarks and Specs. So far, featured content, opencl* versions. Did you try to execute your gl tessellation sample on the ivy bridge? Intel hd graphics memory on your computer. I have updated the graphics drivers as far as i can. But here on steam, opencl* versions. My mac's hd 4000 controller supports directx 11. Acer One D255e Drivers PC . I recently purchased a subscription for photoshop cc 2017, after my trial for cs6 ran out. Opengl problems on windows 10 with intel hd graphics 3000 hi fellas, maybe some of you can help me. My son is wanting to run scrap mechanic on steam, on windows 7, 64 bit. Is there any graphics 4000 opengl for mac really support. I have a core i5 2520m cpu with intel hd graphics 3000 under windows 10. In cs6, my graphics card, the intel hd 4000, had some problems, but i was able to fix them and the features that required it worked again. It is a dell laptop, intel i5 cpu 240ghz, with an intel hd graphics chipset, 4gb ram . -

REPORT the Barron's Bears

GILDER February 2006 / Vol. XI No. 2 T E C H N O L O G Y R E P O R T The Barron’s Bears ur Celestial Empire possesses all things in abundance “ and lacks no products within its border. There is there- O fore no need to import the manufactures of outside barbarians.” —Emperor Qian Long, 1793, to King George III’s Ambassador (quoted in Fast Boat to China by Andrew Ross). It’s mid-winter, snowing again outside my window. After some 60 days of cross country skiing so far in Western Massachusetts, two schusses to Silicon Valley, and my son Richard a newly instrument rated pilot, I feel pretty good. With Dick Sears’ Gilder Technology Index (www.GTIndex.com) up some 325 percent since the crash and 27 percent in the last Power-One is the 52 weeks, I feel pretty fl ush. But as I prepare for another day of Nordic sweltering up and swooping down, something nags in the back of my mind. leader in digital What could it be? Flaws in the Linley Group’s projection of EZchip’s (LNOP) coming three year revenue ramp? A slow IPTV (Internet protocol television) transition dragging power solutions, (CONTINUED ON PAGE 2) with some 50 FEATURED COMPANY: NetLogic (NETL) design wins for Whoa! It seems the only thing fl ying faster than NetLogic’s processor speeds these days is the company’s stock price, up by a whopping third so far in the fi rst month or so of the year. But after listening to CEO Ron Jankov, it’s hard to be anything but buoyant. -

From Parallel to Serial

Computer-On-Modules 9 From Parallel to Serial COM Express™ modules are highly integrated off-the-shelf building blocks based on a PCI Express® bus architecture that plug into custom made, application-specific carrier boards. COM Express™ modules measure just 95 mm x 125 mm and include most generic functions such as video, audio, Ethernet, storage interfaces, and USB ports that are needed for most applications. A custom designed carrier board complements the COM Express™ core module with additional functionality required for a specific application. COM Express™ is a result of the convergence of the latest technology standards based on serial differential signalling such as PCI Express® USB 2.0, Serial ATA, LVDS, and Serial DVO implemented on an extremely compact Computer-on-Module. Moving from parallel busses such as PCI™ and IDE to serial busses such as PCI Express® is a change the scale of which has not been seen since PCI™ replaced ISA. 9-1 http://www.adlinktech.com/Computer-on-Module 1 Procucts AdvancedTCA 2 6U cPCI Blades 3 Platforms 6U cPCI 4 3U cPCI Blades PCI Express® as a Central Bus Legacy Support At the core of the COM Express™ module lies the PCI Express® In an effort to protect existing investments, the initial COM 5 Platforms 3U cPCI bus. PCI Express® is a two-way serial connection that carries data in Express™ standard will maintain support for 32-bit PCI™, packets along two pairs of point-to-point data lanes. It can be used ISA through LPC and PATA IDE. At a later stage the COM as a peripheral device interconnect, a chip-to-chip interconnect, and Express™ formfactor will abandon both PCI™ and IDE a bridge to other interconnects such as IEEE 1394b, USB 2.0, SATA, legacy signals to make room for two additional Gigabit and Gigabit Ethernet. -

Intel® System Controller Hub (Intel® SCH) Datasheet

Intel® System Controller Hub (Intel® SCH) Datasheet May 2010 Document Number: 319537-003US LINFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. UNLESS OTHERWISE AGREED IN WRITING BY INTEL, THE INTEL PRODUCTS ARE NOT DESIGNED NOR INTENDED FOR ANY APPLICATION IN WHICH THE FAILURE OF THE INTEL PRODUCT COULD CREATE A SITUATION WHERE PERSONAL INJURY OR DEATH MAY OCCUR. Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined". Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information. The Intel® System Controller Hub (Intel® SCH) may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request. Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.