EE 330 Lecture 15 Devices in Semiconductor Processes

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Schottky Diodes Selection Guide

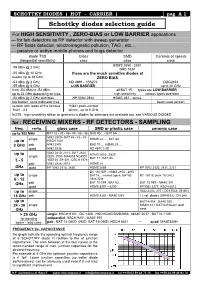

SCHOTTKY DIODES ( HOT - CARRIER ) pag A 1 Schottky diodes selection guide For HIGH SENSITIVITY , ZERO-BIAS or LOW BARRIER applications --- for lab detectors as RF detector with sweep generator --- RF fields detector, electromagnetic pollution, TAG , etc… --- passive or active mobile phones and bugs detector diode TSS Glass SMD Ceramic or special (tangential sensitivity) case case case HSMS 2850 - 2851 -59 dBm @ 2 GHz SMS 7630 -55 dBm @ 10 GHz these are the much sensitive diodes at usable up to 18 GHz ZERO BIAS -53 dBm @ 2 GHz ND 4991 - 1SS276 DDC2353 -55 dBm @ 6 GHz LOW BARRIER up to 20 GHz from -54 dBm to -52 dBm all BAT 15… types are LOW BARRIER up to 24 GHz depending on type high sensitivity vatious types available -56 dBm @ 2 GHz with bias HP 5082-2824 HSMS.282…series low barrier, up to millimeter freq. beam lead version version with leads of the famous 1N821 point-contact 1N21 - 23 silicon , up to 5 GHz NOTE : high sensitivity silicon or germanium diodes for detectors are available too, see VARIOUS DIODES for : RECEIVING MIXERS - RF DETECTORS - SAMPLING freq. config. glass case SMD or plastic case ceramic case up to 500 MHz BAT 42 - 43 - 46 - 48 - 85 - 86 BAS 40-…- BAT 64-.... 5082.2800 - BAT 45 - 82 - 83 single HSMS 28.... , BAT 68 up to HSCH 1001 2 GHz pair 5082.2804 BAS 70... , HSMS 28... quad 5082.2836 ND 487C1-3R 5082.2810, 2811, 2817 2824, up to HSMS 2810 , 2820 single 2835, 2900, MA4853 ND4991 BAT 17 , BAT 68 3 - 5 1SS154 ,BA 481, QSCH 5374 pair 5082.2826, 2912 HSMS 28…. -

Special Diodes 2113

CHAPTER54 Learning Objectives ➣ Zener Diode SPECIAL ➣ Voltage Regulation ➣ Zener Diode as Peak Clipper DIODES ➣ Meter Protection ➣ Zener Diode as a Reference Element ➣ Tunneling Effect ➣ Tunnel Diode ➣ Tunnel Diode Oscillator ➣ Varactor Diode ➣ PIN Diode ➣ Schottky Diode ➣ Step Recovery Diode ➣ Gunn Diode ➣ IMPATT Diode Ç A major application for zener diodes is voltage regulation in dc power supplies. Zener diode maintains a nearly constant dc voltage under the proper operating conditions. 2112 Electrical Technology 54.1. Zener Diode It is a reverse-biased heavily-doped silicon (or germanium) P-N junction diode which is oper- ated in the breakdown region where current is limited by both external resistance and power dissipa- tion of the diode. Silicon is perferred to Ge because of its higher temperature and current capability. As seen from Art. 52.3, when a diode breaks down, both Zener and avalanche effects are present although usually one or the other predominates depending on the value of reverse voltage. At reverse voltages less than 6 V, Zener effect predominates whereas above 6 V, avalanche effect is predomi- nant. Strictly speaking, the first one should be called Zener diode and the second one as avalanche diode but the general practice is to call both types as Zener diodes. Zener breakdown occurs due to breaking of covalent bonds by the strong electric field set up in the depletion region by the reverse voltage. It produces an extremely large number of electrons and holes which constitute the reverse saturation current (now called Zener current, Iz) whose value is limited only by the external resistance in the circuit. -

(Or Varicap) Diode

Radio and Electronics Cookbook 20 The varactor (or varicap) diode Introduction Many of the circuits for receivers and transmitters presented in this series rely upon the variable capacitor as a means of tuning. Another method of varying capacitance (without any moving parts) is provided by the varactor diode, sometimes called a varicap diode. This is a component which changes its capacitance as the voltage across it is varied. The details Figure 1 shows how a varactor diode might be connected to demonstrate its operation. Its symbol is that of an ordinary diode, with a capacitor symbol next to it. A variable voltage is applied across it in such a way that the diode is reverse-biased. This means that virtually no current passes through it – the positive voltage is applied to the cathode. Varactors are cheaper than variable capacitors, and they are tiny in comparison, very suitable for today’s miniature circuits. If A and B were connected across the tuning coil in a simple receiver (with a series capacitor to block the DC from the battery reaching the coil), the tuning operation would be accomplished by turning the knob on the 10 kilohm potentiometer. Varactors are available with different values, from less than 20 picofarad (pF) for VHF applications to 500 pF for medium-wave radios. They are Figure 1 The capacitance of the varicap diode (between A and B) increases as the voltage is reduced, using the variable resistor 64 A portable radio for medium waves tuned usually by voltages between 2 V and 9 V. For a real application of varactors, you should consult the circuit diagram of the Yearling 20 metre receiver, elsewhere in this book. -

J. W. Miller Company the Coil Forum March 1960

J. W. MILLER COMPANY-LOS ANGELES, CALIFORNIA-VOLUME 1, NUMBER 1 MARCH 1960 A TRANSISTOR FM RECEIVER With this issue, the J. W. Miller Company inaugurates a new publication devoted to the experimenter. Although coils, and their associated com ponents, are our business, we at Miller would like to supply our customers with timely information on circuits, theory to assist with your work or experiments, and data on how to select and use our coils wisely. We believe you will agree that THE COIL FORUM is indeed an appropriate nam~. www.SteamPoweredRadio.Com J. W. M I L L E R C O M P A N Y Recent advances in the state of the semiconductor from the collector back to the base through capacitor art have made it possible to construct a transistor Cl2 and the stage oscillates. Coil L3, along with the FM receiver which performs every bit as well as a tuning capacitor and circuit capacity, determines the vacuum tube version. VHF equipment places very frequency of oscillation, which is always 10. 7 me. strict demands on the transistors. They must be above the incoming signal frequency. Resistors R9 capable of constant amplification over the entire and Rl 1 provide bias and RIO is used for d.c. degener band being received, create a minimum of circuit ation. Transistor QlO and diode Xl are part of the drift, and provide maximum gain with a minimum automatic frequency control system and will be of stages. ' discussed later. All tuned circuits in the "front end" are tracked with a three-gang variable capacitor The excellent performance of the receiver to be (C3, 3-lOmmfd.) described is an outgrowth of the work done by Philco Corporation on their transistor "Safari" tele The i.f. -

Capacitor & Capacitance

CAPACITOR & CAPACITANCE - TYPES Capacitor types Listed by di-electric material. A 12 pF 20 kV fixed vacuum capacitor Vacuum : Two metal, usually copper, electrodes are separated by a vacuum. The insulating envelope is usually glass or ceramic. Typically of low capacitance - 10 - 1000 pF and high voltage, up to tens of kilovolts, they are most often used in radio transmitters and other high voltage power devices. Both fixed and variable types are available. Vacuum variable capacitors can have a minimum to maximum capacitance ratio of up to 100, allowing any tuned circuit to cover a full decade of frequency. Vacuum is the most perfect of dielectrics with a zero loss tangent. This allows very high powers to be transmitted without significant loss and consequent heating. Air : Air dielectric capacitors consist of metal plates separated by an air gap. The metal plates, of which there may be many interleaved, are most often made of aluminium or silver-plated brass. Nearly all air dielectric capacitors are variable and are used in radio tuning circuits. Metallized plastic film: Made from high quality polymer film (usually polycarbonate, polystyrene, polypropylene, polyester (Mylar), and for high quality capacitors polysulfone), and metal foil or a layer of metal deposited on surface. They have good quality and stability, and are suitable for timer circuits. Suitable for high frequencies. Mica: Similar to metal film. Often high voltage. Suitable for high frequencies. Expensive. Excellent tolerance. Paper: Used for relatively high voltages. Now obsolete. Glass: Used for high voltages. Expensive. Stable temperature coefficient in a wide range of temperatures. Ceramic: Chips of alternating layers of metal and ceramic. -

How Diodes Work

HOW DIODES WORK There are several types of diode included in your Joe Knows Electronics Semiconductor Kit: general- purpose diodes, Zener diodes, Schottky diodes, PIN IMPORTANT diodes, varicap (variable capacitance) diodes, and current regulation diodes. NOTE CONTENTS ON DIODE PACKAGES CONTACT US ....................................... 3 Most of the diodes supplied in our DATASHEET ACCESS ............................ 4 semiconductor kit are in very small DO-35 glass cases. There is very little room on GENERAL PURPOSE DIODES ............... 5 these cases to print identifying numbers and codes clearly. It would be best to ZENER DIODES .................................. 11 keep track of the identities of parts from SCHOTTKY DIODES ............................ 13 the moment they are removed from their envelopes until they are replaced. PIN DIODES ....................................... 15 VARICAP DIODES ............................... 18 CURRENT REGULATION DIODES ........ 23 CONTACT US DATASHEET Email ACCESS [email protected] Access more information about this The best way to communicate with us is by product including datasheets by email. This allows us to have a record of your scanning this QR code or visiting correspondence and the ability to convey information like technical specifications wiki.joeknowselectronics.com more easily. Toll Free Number 855-JOE-KNOW (855-563-5669) Someone is available 24/7 to take your call at our toll free number. Your contact information will be taken and a member of our management team will contact you within normal business hours, 9am – 6pm EST M-F. Please note that our phone associates don’t have the necessary information to discuss products or orders but will direct your call Find community driven content and to the appropriate company representative. -

Variable Capacitors in RF Circuits

Source: Secrets of RF Circuit Design 1 CHAPTER Introduction to RF electronics Radio-frequency (RF) electronics differ from other electronics because the higher frequencies make some circuit operation a little hard to understand. Stray capacitance and stray inductance afflict these circuits. Stray capacitance is the capacitance that exists between conductors of the circuit, between conductors or components and ground, or between components. Stray inductance is the normal in- ductance of the conductors that connect components, as well as internal component inductances. These stray parameters are not usually important at dc and low ac frequencies, but as the frequency increases, they become a much larger proportion of the total. In some older very high frequency (VHF) TV tuners and VHF communi- cations receiver front ends, the stray capacitances were sufficiently large to tune the circuits, so no actual discrete tuning capacitors were needed. Also, skin effect exists at RF. The term skin effect refers to the fact that ac flows only on the outside portion of the conductor, while dc flows through the entire con- ductor. As frequency increases, skin effect produces a smaller zone of conduction and a correspondingly higher value of ac resistance compared with dc resistance. Another problem with RF circuits is that the signals find it easier to radiate both from the circuit and within the circuit. Thus, coupling effects between elements of the circuit, between the circuit and its environment, and from the environment to the circuit become a lot more critical at RF. Interference and other strange effects are found at RF that are missing in dc circuits and are negligible in most low- frequency ac circuits. -

Document For

Semiconductor List FCC ID: ALH32943210 Model Name: TK-8102H TK-8102H Semiconductor List SYMBOL PARTS NUMBER PARTS NAME DESCRIPTION D1 DA221 DIODE SURGE ABSORPTION D2 DA221 DIODE SURGE ABSORPTION D3 DA221 DIODE SURGE ABSORPTION D4 DA221 DIODE SURGE ABSORPTION D6 MA2S111 DIODE DC SWITCH D7 HZU5ALL DIODE VOLTAGE DROPPED D9 MA2S304 VARICAP RX VCO D10 MA2S304 VARICAP TX VCO D11 MA2S304 VARICAP RX VCO D12 MA2S304 VARICAP TX VCO D13 DAN222 DIODE IF SWITCH (WIDE/NARROW) D14 MA360 VARICAP MODULATION D15 DAN222 DIODE IF SWITCH (WIDE/NARROW) D16 MA2S111 DIODE RIPPLE FILTER D18 MA742 DIODE RECTIFICATION D19 DAN235E DIODE RF SWITCH (TX/RX) D21 HVC350B VARICAP RF BPF TUNING D22 HVC350B VARICAP RF BPF TUNING D23 DA221 DIODE TEMPERATURE COMPENSATION D24 MA742 DIODE LIMITER D25 HVC350B VARICAP RF BPF TUNING D26 HVC350B VARICAP RF BPF TUNING D28 HVC350B VARICAP RF BPF TUNING D38 ZSH5MA27 DIODE REVERSE CONNECT PROTECTION D39 02DZ18 (X,Y) DIODE OVER VOLTAGE DETECTION D41 1812L110PR POLY SW CURRENT PROTECTION D43 DAN222 DIODE OR GATE D44 1SS372 DIODE AGC D800 02DZ5.1(Y) DIODE VOLTAGE PROTECTION D801 MA4PH633 DIODE ANT SW D802 MA4PH633 DIODE ANT SW D803 XB15A709 DIODE ANT SW D804 XB15A709 DIODE ANT SW D805 MA742 DIODE APC VOLTAGE DETECT D806 MA742 DIODE APC VOLTAGE DETECT D807 1SS355 DIODE TEMPERATURE COMPENSATION Q2 2SJ243 FET MIC MUTE Q3 2SC4649 (N,P) TRANSISTOR RF AMP Q4 2SA1832 (GR) TRANSISTOR CHARGE PUMP Q5 2SC4738 (GR) TRANSISTOR CHARGE PUMP Q6 2SC4649 (N,P) TRANSISTOR BUFFER AMP Q7 2SJ243 FET T/R SW Q10 2SK508NV (K52) FET RX VCO Q11 2SK508NV (K52) FET -

Two Terminal Special Purpose Devices First Year

www.uptunotes.com Content: - Special Purpose two terminal Devices: Light-Emitting Diodes, Varactor (Varicap)Diodes, Tunnel Diodes, Liquid-Crystal Displays. 1- Light Emitting Diode (LED) Light Emitting Diode is a photo electronic device which converts electrical energy to light energy. It is heavily doped P-N junction diode which under forward biased emits spontaneous radiation. The diode is covered with a transparent cover so that the emitted light may come out. Construction- In an LED, the upper layer of p-type semiconductor is deposited by diffusion on n-type layer of semiconductor. The metalized contacts are provided for applying the forward bias to the P-N junction diode from battery B through resistance R which controls the brightness of light emitted. Fig: LED construction Working of LED The LED works on the principle of electroluminescence. When a P-N junction is forward biases, the electrons in N- region cross the junction & recombines with holes in P-region. When electrons recombine with the holes, they move from conduction band to valence band which is at lower energy level. While moving, the additional energy is released by the free electrons which appear in the form of light due to the special material used in the LED. The energy released depends on the forbidden gap energy which determines the wavelength & the colour of the emitted light. Materials of LED The materials which are the mixtures of Gallium, Arsenic & Phosphorus are used in LED to obtain different coliour of light. S.No. Material Symbol Colour 1 Gallium Arsenide GaAs Infrared(Invisible) 2 Gallium Phosphide GaP Red or Green 3 Gallium Arsenide Phosphide GaAsP Red or Yellow By: Navneet Pal Email:[email protected] Page 1 www.uptunotes.com Output Characteristics- The amount of power output translated into light is directly propotional to the forward current If , more forward current If , the greater the output light. -

Design of Transformer Based Cmos Active Inductances

Proceedings of the 5th WSEAS Int. Conf. on Microelectronics, Nanoelectronics, Optoelectronics, Prague, Czech Republic, March 12-14, 2006 (pp64-69) DESIGN OF TRANSFORMER BASED CMOS ACTIVE INDUCTANCES G.SCANDURRA, C.CIOFI Dipartimento di Fisica della Materia e TFA Università degli Studi di Messina Salita Sperone 31, I-98166 Messina ITALY Abstract: - In this paper the design of a transformer based CMOS active inductance to be used for the realization of fully integrated RF CMOS front ends is discussed. The circuit topology employed aims at taking the maximum advantage of the limited transconductance gain of MOS devices for compensating the losses of the integrated magnetic structures. In this way, even if a 0.35 µm technology has been employed, it has been possible to obtain an equivalent “almost ideal” inductance of 6 nH at a center frequency of 2.4 GHz. The circuit operates with a supply voltage of 3.3 V and drives less than 1 mA. Moreover, two control voltages can be used in order to tune the maximum quality factor of the inductance and to change in a relatively wide range the frequency at which it occurs. Key-Words: - Active inductance, Integrated transformer, CMOS, Quality factor, RF, Circuit design 1 Introduction approach is the one in which a bi-pole with a Modern RF front ends to be used for mobile negative resistance behaviour is put in series to the communication and wireless networking require a inductor in order to compensate the losses and considerable amount of digital signal elaboration increase the resulting quality factor Q[8]. A third thus making the CMOS technology the mandatory approach exploits the magnetic coupling between choice if one has to design very low cost fully the spirals of an integrated transformer and a current integrated front ends. -

Basics and Types of Diodes

Basics and Types of Diodes Introduction to Diode: A diode is an electric device that permits the flow of current only in one direction and restricts the flow in the opposite direction. The most ordinary sort of diode in current circuit design is the semi-conductor diode, even though additional diode technologies are present. The word “diode” is traditionally aloof for tiny signal appliances, I ≤ 1 A. When a diode is positioned in a simple battery lamp circuit, then the diode will either permit or stop flow of current through the lamp, all this depend on the polarization of the volts applied. There are various sorts of diode but their fundamental role is identical. The most ordinary kind of diode is silicon diode; it is placed in a glass cylinder. The symbol of diode is represented as follows: Diode Operation: A diode starts its operations when a voltage signal applies across its terminals. A DC volt is applied so that diode starts its operation in a circuit and this is known as Biasing. Diode is similar to a switch which is one way, hence it can be either in conduction more or non-conduction mode. “ON” mode of the diode, is attained by forward biasing, which simply means that higher or positive potential is applied on the anode and on the cathode, negative or lower potential is applied of a diode. Whereas the “OFF” mode of the diode is attained with the aid of reverse biasing which simply means that higher or positive potential is applied on the cathode and on the anode, negative or lower potential is applied of a diode. -

Chapter 16 Other Two-Terminal Devices 11 Other Twoother Two-Two---Terminalterminal Devicesterminal Devices

www.getmyuni.com Chapter 16 Other Two-Terminal Devices 11 www.getmyuni.com owT seciveDrehtOo-wTowT lanimreT rehtO rehtO--seciveD owTseciveD rehtO lanimreT- lanimreT seciveD lanimreT odideShcott ky odideShcott ky odide aartcorV odide aartcorV odidse reoPw odidse reoPw odide unnleT odide unnleT hPoteoodid hPoteoodid sllec ehPvoitoutcocnd sllec ehPvoitoutcocnd ttismreeIR ttismreeIR asplydisyrcsta ldq uiiL asplydisyrcsta ldq uiiL sllec Soalr sllec Soalr stiomhrserT stiomhrserT iaCrcneDd1vTuh 0iei/etoc lEryeec,s t ronic 2 2 aNaLsoBnoyLdhu. eli lesoRssb ektrat dy www.getmyuni.com DodeiShcottky DodeiShcottky arbrierAlso called ar-brier arbrier ycottkSh-, ar-brier ycottkShcarrier rufacse-, or -carrier rufacse ot-hdiode. oth arhacCtertiicss arhacCtertiicss (Compared with general-purpose diodes) • Lower forward voltage drop (0.2-.63V) • Higher forward current (up to 75A) • Significantly lower PIV • Higher reverse current • Faster switching rate snoitacilppAApplications snoitacilppA gnihciswt ycneuqfre higH•High frequency switching gnihciswt ycneuqfre higH snoitacilppaapplications snoitacilppa hihgwLo• egatlovLow- Low---voltage wLovoltage tnerruc high-high---current hihgcurrent egatlov tnerruc snoitacilppaapplications snoitacilppa sretrevnoc•CAAC- AC---to CA tototo-CD---DCDC converters sretrevnoc CD tnempiuqe noitacinummoC•Communication equipment tnempiuqe noitacinummoC stiuicrc noitatnemurstIn•Instrumentation circuits stiuicrc noitatnemurstIn Electronic Devices and Circuit Theory, 10/e 33 Robert L. Boylestad and Louis Nashelsky www.getmyuni.com edoiD rotcaraVVaractor Diode edoiD rotcaraV Also calledvacapir a VVC vacapir, VVC(voltage- variable capacitance),odidetnugni or odidetnugni. It basically acts like a variable capacitor. Electronic Devices and Circuit Theory, 10/e 44 Robert L. Boylestad and Louis Nashelsky www.getmyuni.com noitarepO edoiD rotcaraVVaractor Diode Operation noitarepO edoiD rotcaraV A reverse-biased varactor acts like a capacitor. Furthermore, the amount of reverse bias voltage determines the capacitance.