Operational Amplifier, Comparator

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Op-Amp Comparators Model of a Schmitt Trigger

1 Electronic Instrumentation Experiment 6 -- Digital Switching Part A: Transistor Switches Part B: Comparators and Schmitt Triggers Part C: Digital Switching Part D: Switching a Relay Part A: Transistors Analog Circuits vs. Digital Circuits Bipolar Junction Transistors Transistor Characteristics Using Transistors as Switches 2 Analog Circuits vs. Digital Circuits An analog signal is an electric signal whose value varies continuously over time. A digital signal can take on only finite values as the input varies over time. 3 • A binary signal, the most common digital signal, is a signal that can take only one of two discrete values and is therefore characterized by transitions between two states. • In binary arithmetic, the two discrete values f1 and f0 are represented by the numbers 1 and 0, respectively. 4 • In binary voltage waveforms, these values are represented by two voltage levels. • In TTL convention, these values are nominally 5V and 0V, respectively. • Note that in a binary waveform, knowledge of the transition between one state and another is equivalent to knowledge of the state. Thus, digital logic circuits can operate by detecting transitions between voltage levels. The transitions are called edges and can be positive (f0 to f1) or negative (f1 to f0). 1 positive negative positive edge 0 edges edge 5 Bipolar Junction Transistors The bipolar junction transistor (BJT) is the salient invention that led to the electronic age, integrated circuits, and ultimately the entire digital world. The transistor is the principal active device in electrical circuits. When inputs are kept relatively small, the transistor serves as an amplifier. When the transistor is overdriven, it acts as a switch, a mode most useful in digital electronics. -

Basic Operational Amplifier Circuits

Basic Operational Amplifier Circuits Electronic Devices, 9th edition © 2012 Pearson Education. Upper Saddle River, NJ, 07458. Thomas L. Floyd All rights reserved. Comparators A comparator is a specialized nonlinear op-amp circuit that compares two input voltages and produces an output state that indicates which one is greater. Comparators are designed to be fast and frequently have other capabilities to optimize the comparison function. Comparator Differentiator An example of a – C Retriggerable one-shot comparator application is + R shown. The circuit detects Vin a power failure in order to take an action to save data. As long as the comparator senses Vin , the output will be a dc level. Electronic Devices, 9th edition © 2012 Pearson Education. Upper Saddle River, NJ, 07458. Thomas L. Floyd All rights reserved. Comparators Operational amplifiers are often used as comparators to compare the amplitude of one voltage with another. In this application, op-amps are used in the open-loop configuration. Due to high open-loop gain, an op-amp can detect very tiny differences at the input. The input voltage is applied to one terminal while a reference voltage on the other terminal. Comparators are much faster than op-amps. Op-amps can be used as comparators but comparators cannot be used as op-amps. Electronic Devices, 9th edition © 2012 Pearson Education. Upper Saddle River, NJ, 07458. Thomas L. Floyd All rights reserved. Zero-Level Detection Figure 1(a) shows an op-amp circuit to detect when a signal crosses zero. This is called a zero-level detector. Notice that inverting input is grounded to produce a zero level and the input signal is applied to the noninverting terminal. -

Analog Integrated Circuits

Analog Integrated Circuits Jieh-Tsorng Wu 6 de febrero de 2003 1. Introduction Complete Small-Signal Model with Extrinsic Components 2. PN Junctions and Bipolar Junction Transis- tors Typical values of Extrinsic Components PN Junctions 3. MOS Transistors Small-Signal Junction Capacitance MOS Transistors Large-Signal Junction Capacitance Strong Inversion PN Junction in Forward Bias Channel Charge Transfer Characteristics PN Junction Avalanche Breakdown Simplified Channel Charge Transfer Charac- PN Junction Breakdown teristics Bipolar Junction Transistor (BJT) MOST I-V Characteristics Minority Carrier Current in the Base Region Threshold Voltage Gummel Number (G) Square-Law I-V Characteristics Base Transport Current Channel-Length Modulation Forward Current Gain MOST Small-Signal Model in Saturation Re- gion BJT DC Large-Signal Model in Forward- Active Region OST Small-Signal Model in Saturation Re- gion Dependence of BF on Operating Condition MOST Small-Signal Capacitances in Satura- Collector Voltage Effects tion Region Base Transport Model Channel Capacitance in Saturation Region Ebers-Moll Model Complete MOST Small-Signal Model in Sat- Leakage Current uration Region Common-Base Transistor Breakdown MOST Small-Signal Model in Triode Region Common-Emitter Transistor Breakdown MOST Small-Signal Model in Cutoff Region Small-Signal Model of Forward-Biased BJT Carrier Velocity Saturation Charge Storage Effects of Carrier Velocity Saturation 1 Hot Carriers 5. Single-Transistor Gain Stages Short-Channel Effects Unilateral Two-Port Network Subthreshold -

Nanoelectronic Mixed-Signal System Design

Nanoelectronic Mixed-Signal System Design Saraju P. Mohanty Saraju P. Mohanty University of North Texas, Denton. e-mail: [email protected] 1 Contents Nanoelectronic Mixed-Signal System Design ............................................... 1 Saraju P. Mohanty 1 Opportunities and Challenges of Nanoscale Technology and Systems ........................ 1 1 Introduction ..................................................................... 1 2 Mixed-Signal Circuits and Systems . .............................................. 3 2.1 Different Processors: Electrical to Mechanical ................................ 3 2.2 Analog Versus Digital Processors . .......................................... 4 2.3 Analog, Digital, Mixed-Signal Circuits and Systems . ........................ 4 2.4 Two Types of Mixed-Signal Systems . ..................................... 4 3 Nanoscale CMOS Circuit Technology . .............................................. 6 3.1 Developmental Trend . ................................................... 6 3.2 Nanoscale CMOS Alternative Device Options ................................ 6 3.3 Advantage and Disadvantages of Technology Scaling . ........................ 9 3.4 Challenges in Nanoscale Design . .......................................... 9 4 Power Consumption and Leakage Dissipation Issues in AMS-SoCs . ................... 10 4.1 Power Consumption in Various Components in AMS-SoCs . ................... 10 4.2 Power and Leakage Trend in Nanoscale Technology . ........................ 10 4.3 The Impact of Power Consumption -

Computer Aided Design of Electronic Devices

TOMSK POLYTECHNIC UNIVERSITY O.A. Kozhemyak, D.N. Ogorodnikov COMPUTER AIDED DESIGN OF ELECTRONIC DEVICES It is recommended for publishing as a study aid by the Editorial Board of Tomsk Polytechnic University Tomsk Polytechnic University Publishing House 2014 1 UDC 621.38(075.8) BBC 31.2 K58 Kozhemyak O.A. K58 Computer aided design of electronic devices: study aid / O.A. Kozhemyak, D.N. Ogorodnikov; Tomsk Polytechnic University. – Tomsk: TPU Publishing House, 2014. – 130 p. This textbook focuses on the basic notions, history, types, technology and applications of computer-aided design. Methods of electronic devices simulation, automated design of power electronic devices and components, constructive- technological design are considered and discussed. Some features of the popular electronics CADs are also shown. There are a lot of practical examples using CADs of electronics. The textbook is designed at the Department of Industrial and Medical Electronics of TPU. It is intended for students majoring in the specialty „Electronics and Nanoelectronics‟. UDC 621.38(075.8) BBC 31.2 Reviewer Cand.Sc, Head of Laboratory, Tomsk State University of Control Systems and Radioelectronics Aleksandr V. Osipov © STE HPT TPU, 2014 © Kozhemyak O.A., Ogorodnikov D.N., 2014 © Design. Tomsk Polytechnic University Publishing House, 2014 2 Introduction. CAD around Us ........................................................................... 5 What is CAD? ................................................................................................ 5 Overview -

Basics of Operational Amplifiers and Comparators Application Note

Basics of Operational Amplifiers and Comparators Application Note Basics of Operational Amplifiers and Comparators Outline: Op-amps, also known as operational amplifiers, are used for voltage amplifiers, filters, phase shifts, and more. The comparator, also known as a voltage comparator, has a function to detect the high or low voltage with respect to the reference signal. This document explains the basic electrical characteristics (offset voltage, common-mode input voltage, open gain, common-mode input signal rejection ratio, frequency characteristics, etc.), absolute maximum ratings, and general usage (non-inverting amplifier, inverting amplifier). © 202 0-2021 1 2021-03-26 Toshiba Electronic Devices & Storage Corporation Basics of Operational Amplifiers and Comparators Application Note Table of Contents 1. Introduction ............................................................................................................. 3 2. Op-amps and comparators ......................................................................................... 4 2.1. Op-amp and comparator configurations.................................................................. 4 2.2. Selecting op-amps and comparators ...................................................................... 6 2.3. Power supplies for op-amps and comparators ......................................................... 6 2.4. Noninverting amplifier ......................................................................................... 7 2.5. Inverting amplifier ............................................................................................. -

The TL431 in Loop Control

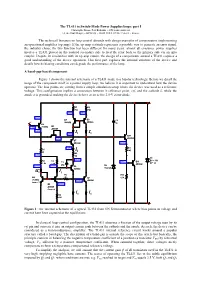

The TL431 in Switch-Mode Power Supplies loops: part I Christophe Basso, Petr Kadanka − ON Semiconductor 14, rue Paul Mesplé – BP53512 - 31035 TOULOUSE Cedex 1 - France The technicall literature on loop control abounds with design examples of compensators implementing an operational amplifier (op amp). If the op amp certainly represents a possible way to generate an error signal, the industry choice for this function has been different for many years: almost all consumer power supplies involve a TL431 placed on the isolated secondary side to feed the error back to the primary side via an opto coupler. Despite its similarities with its op amp cousin, the design of a compensator around a TL431 requires a good understanding of the device operation. This first part explores the internal structure of the device and details how its biasing conditions can degrade the performance of the loop. A band-gap-based component Figure 1 shows the internal schematic of a TL431 made in a bipolar technology. Before we detail the usage of the component itself in a power supply loop, we believe it is important to understand how the device operates. The bias points are coming from a simple simulation setup where the device was used as a reference voltage. This configuration implies a connection between it reference point, ref , and the cathode k, while the anode a is grounded, making the device behave as an active 2.5-V zener diode. k R7 R8 760 760 7.01V 7.01V 12 13 7.07V Q8 Q9 C2 ref 2N3906 2N3906 8p Q2 2.49V 2N3904 Q3 2N3904 1.87V 4 I I 6.46V 1 1 14 Q10 1.24V 2 2N3904 Q7 2N3904 637mV 16 1.29V R9 10 R1 I 240 2k 1 R6 1.12V 4K 17 3 D1 970mV R2 BV = 36V R3 11 584mV Q11 C1 N = 1.3 1.9k 5.7k 2N3904 20p D2 585mV 581mV Q6 1N4148 5 6 2N3904 3I 1 I1 R5 R10 Q4 4k Q1 6.6k 2N3904 580mV9 2N3904 Area = 3 Q5 45.9mV 2N3904 7 Area = 6 I I R4 1 1 482 a Figure 1 : the internal schematic of a typical TL431 from ON Semiconductor where bias points in voltage and current have been captured at the equilibrium. -

CL User Guide T of C

Contents Chapter 1 — Introduction ............................................................................ 1-1 What is CircuitLogix?...............................................................................................................1-1 Required Hardware/Software ...................................................................................................1-3 First Time Installation ..............................................................................................................1-3 Multi-user (Project) Installations .............................................................................................1-3 Using On-line Help ..................................................................................................................1-5 Where to go from here .............................................................................................................1-6 Technical Support ....................................................................................................................1-6 Required User Background ......................................................................................................1-6 Chapter 2 — Schematic Capture ................................................................. 2-1 Getting Started—Schematic Example .......................................................................................2-1 The Editing Tools ....................................................................................................................2-4 Placing -

Experiment 6 Transistors As Amplifiers and Switches

Introductory Electronics Laboratory Experiment 6 Transistors as amplifiers and switches Our final topic of the term is an introduction to the transistor as a discrete circuit element. Since an integrated circuit is constructed primarily from dozens to even millions of transistors formed from a single, thin silicon crystal, it might be interesting and instructive to spend a bit of time building some simple circuits directly from these fascinating devices. We start with an elementary description of how a particular type of transistor, the bipolar junction transistor (or BJT) works. Although nearly all modern digital ICs use a completely different type of transistor, the metal-oxide-semiconductor field effect transistor (MOSFET), most of the transistors in even modern analog ICs are still BJTs. With a basic understanding of the BJT in hand, we design simple amplifiers using this device. We spend a bit of time studying how to properly bias the transistor and how to calculate a transistor amplifier’s gain and input and output impedances. Following our study of amplifiers, we turn to the use of the BJT as a switch, a fundamental element of a digital logic circuit. Single transistor switches are useful as a way to interface a relatively low-power op-amp comparator output to a high-current or high-voltage device. These switches are also very useful to translate the output of an op-amp comparator to the proper 1 and 0 voltage levels of a standard digital logic circuit input. The final section of the text presents a few additional useful transistor applications including a discussion of a differential amplifier and a basic Class B power amplifier stage, both of which represent common building blocks of the operational amplifier. -

Op Amps, Linear (Negative Feedback) Circuits, Nonlinear Circuits

Operational Amplifiers A. Stolp, 4/22/01 rev, 2/6/12 An operational amplifier is basically a complete high-gain voltage amplifier in a small package. Op-amps were originally developed to perform mathematical operations in analog computers, hence the odd name. They are now made using integrated circuit technology, so they come in the typical multi-pin IC packages. With the proper external components, the operational amplifier can perform a wide variety of “operations” on the input voltage. It can multiply the input voltage by nearly any constant factor, positive or negative, it can add the input voltage to other input voltages, and it can integrate or differentiate the input voltage. The respective circuits are called amplifiers, summers, integrators, and differentiators. Op-amps are also used to make active frequency filters, current-to-voltage converters, voltage-to-current converters, current amplifiers, voltage comparators, etc. etc.. These little parts are so versatile, useful, handy, and cheap that they’re kind of like electronic Lego blocks — although somewhat drably colored. Op-amp characteristics Operational amplifiers have several very important characteristics that make them so useful: 1. An op-amp has two inputs and it amplifies the voltage difference between those two inputs. These two inputs are known as the noninverting input, labeled (+), and the inverting input, labeled (-), as shown in Fig. 1. The output voltage is a function of the noninverting input voltage minus the inverting input Figure 1 Op-amp symbol voltage. ' & That is: vo G(va vb) Where G = voltage gain of the op-amp. 2. The op-amp must be connected to external sources of power (not shown on the drawing above). -

SCHMITT TRIGGER (Regenerative Comparator) Schmitt Trigger Is an Inverting Comparator with Positive Feedback

SCHMITT TRIGGER (regenerative comparator) Schmitt trigger is an inverting comparator with positive feedback. It converts an irregular-shaped waveform to a square wave or pulse, also called as squaring circuit. The input voltage Vin triggers the output V0 every time it exceeds certain voltage levels called the upper threshold voltage Vut and lower threshold voltage Vlt, These threshold voltages are obtained by using the voltage divider where the voltage across R1 is fed back to the input. The voltage across R1 is a variable reference threshold voltage that depends on the value and polarity of the output voltage V0 When Vo = +VSat, the voltage across R1 is called the upper threshold voltage, Vut The input vp voltage Vin must be slightly more positive than Vut Vut in order to cause the output switch from +VSat to -VSat. Vut As long as Vin <Vut, Vo is at +Vsat. -vp Vut =R1/R1+R2 (+VSat) On the other hand, when V0 = -Vsat, the voltage across R1 is referred to as lower threshold +vsat voltage, vin be slightly more negative than vlt in order to switch V0 from +Vsat to -Vsat. In other words, for vin values greater than vlt, vo is at -Vsat. Vlt is given -vsat by the following equation Fig : I/O waveform (c) Vo vs Vin plot of . hysteresis voltage Vlt =R1/R1+R2 (-VSat) Thus, if the threshold voltages are made larger than the input noise voltages, the positive feedback will eliminate the false output transitions. Resistance ROM used to minimize the offset problems. In the triangular wave and sawtooth wave generators a noninverting comparator is used as a Schmitt trigger. -

"Understanding Basic Analog

Application Report SLOA026A - April 2000 Understanding Basic Analog – Active Devices Ron Mancini Mixed Signal Products ABSTRACT This application report describes active devices and their use as the basic building blocks of all electronic equipment. Active devices, coupled with passive devices, create the combination needed to fulfill all circuit requirements. A select few active devices are discussed in this report. Contents Introduction . 2 Bipolar Junction Transistor . 2 Junction Field Effect Transistor. 3 Metal Oxide Semiconductor Field Effect Transistors. 4 Voltage Feedback Operational Amplifier. 6 Current Feedback Operational Amplifiers. 7 Voltage Comparators . 8 Other Active Devices . 8 Summary . 9 List of Figures 1 BJT Description . 2 2 BJT Model of an NPN . 3 3 JFET Description . 4 4 JFET Model . 4 5 MOSFET Description . 5 6 MOSFET Model . 5 7 Voltage Feedback Op Amp Model. 6 8 Current Feedback Op Amp Model. 7 9 Voltage Comparator Model . 8 1 SLOA026A Introduction Active devices have gain, thus they have transfer functions which are not available to passive devices. Active devices are considerably more complicated than passive devices; hence, their models and transfer equations are more complicated than those of passive devices. Active devices are the foundation on which all electronics equipment is built. Integrated circuits and higher forms of electronic components are built from the active devices discussed here. Bipolar Junction Transistor The bipolar junction transistor (BJT) was the first active semiconductor device manufactured; therefore, it became the workhorse of the semiconductor industry. When the field effect transistor (FET) manufacturing process was perfected, it began competing with the BJT. Since then, the FET has been taking sockets from the BJT, but there are many applications, such as high frequency amplifiers, where the BJT still excels.