Experiment 4 Comparators, Positive Feedback, and Relaxation Oscillators

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Unit-1 Mphycc-7 Ujt

UNIT-1 MPHYCC-7 UJT The Unijunction Transistor or UJT for short, is another solid state three terminal device that can be used in gate pulse, timing circuits and trigger generator applications to switch and control either thyristors and triac’s for AC power control type applications. Like diodes, unijunction transistors are constructed from separate P-type and N-type semiconductor materials forming a single (hence its name Uni-Junction) PN-junction within the main conducting N-type channel of the device. Although the Unijunction Transistor has the name of a transistor, its switching characteristics are very different from those of a conventional bipolar or field effect transistor as it can not be used to amplify a signal but instead is used as a ON-OFF switching transistor. UJT’s have unidirectional conductivity and negative impedance characteristics acting more like a variable voltage divider during breakdown. Like N-channel FET’s, the UJT consists of a single solid piece of N-type semiconductor material forming the main current carrying channel with its two outer connections marked as Base 2 ( B2 ) and Base 1 ( B1 ). The third connection, confusingly marked as the Emitter ( E ) is located along the channel. The emitter terminal is represented by an arrow pointing from the P-type emitter to the N-type base. The Emitter rectifying p-n junction of the unijunction transistor is formed by fusing the P-type material into the N-type silicon channel. However, P-channel UJT’s with an N- type Emitter terminal are also available but these are little used. -

JRE SCHOOL of Engineering

JRE SCHOOL OF Engineering PUT EXAMINATION SET-A MAY 2015 Subject Name Microwave Engineering Subject Code EEC 603 Roll No. of Student Max Marks 100 Max Duration 3 hrs Date 02/05/2015 Time 10:00 a.m. to 1:00 p.m. For Branches: EC Branch only (6th sem) Q. 1 Attempt any FOUR from the following. All question carry equal marks. (5 X 4 = 20) a) A TE11 wave is propagating in a air-filled circular waveguide of diameter 12cm at 2.5GHz, find the cutoff frequency, guide wavelength, wave impedance in the guide. b) Show that TM01 and TM10 modes do not exist in a rectangular waveguide. c) What is a microstrip line? Compare microstrip lines with striplines. Write advantages and disadvantages of both. Microstrip Transmission Line: It is also called open strip line because of the openness of its structure. It has very simple geometry. It is an unsymmetrical strip line that is nothing but a parallel plate transmission line having dielectric substrate, the on face of which is metallised ground and the other (top) face, has thin conducting strip of certain width ‘w’ and thickness ‘t’. The top ground plate is not present and so cover plate is used for shielding purpose. Modes are only quasi TEM, thus the theory of TEM coupled lines applies only. Losses: (i) Dielectric loss in substrate (ii) ohmic skin losses in conductor strip and ground plane. Advantages: (i) Simple construction (ii) easier integration with semiconductor device (iii) fabrication cosh is lower (iv) package and unpacked semiconductor chips can be attached to these lines. -

Multivibrator Circuits

Multivibrator Circuits Bistable multivibrators Multivibrators Circuits characterized by the existence of some well defined states, amongst which take place fast transitions, called switching processes. A switching process is a fast change in value of a current or a voltage, the fast process implying the existence of positive reaction loops, or negative resistances. The switching can be triggered from outside, by means of command signals, or from inside, by slow charge accumulation and the reaching of a critical state by certain electrical quantities in the circuit. Circuits have two, well defined states, which can be either stable or unstable A stable state is a state, in which the circuit, in absence of a driving signal, can remain for an unlimited period of time The circuit can remain in an unstable state only for a limited period of time, after which, in the absence of any exterior command signals, it switches into the other state. The multivibrator circuits can be grouped, according to their number of stable (steady) states, into: - flip-flops (bistable circuits) with both states being stable - monostable circuits , having a stable and an unstable state - astable circuits , with both states being unstable Flip-flop circuits The main feature of the flip-flop circuits is the existence of two stable states, in which the circuit may remain for a long time. The switching from one state to the other is triggered by command signals Flip flop: an example for a sequential circuit (a circuit with outputs that present logical values depending on a certain sequence of signals, that have previously existed in the circuit). -

Op-Amp Comparators Model of a Schmitt Trigger

1 Electronic Instrumentation Experiment 6 -- Digital Switching Part A: Transistor Switches Part B: Comparators and Schmitt Triggers Part C: Digital Switching Part D: Switching a Relay Part A: Transistors Analog Circuits vs. Digital Circuits Bipolar Junction Transistors Transistor Characteristics Using Transistors as Switches 2 Analog Circuits vs. Digital Circuits An analog signal is an electric signal whose value varies continuously over time. A digital signal can take on only finite values as the input varies over time. 3 • A binary signal, the most common digital signal, is a signal that can take only one of two discrete values and is therefore characterized by transitions between two states. • In binary arithmetic, the two discrete values f1 and f0 are represented by the numbers 1 and 0, respectively. 4 • In binary voltage waveforms, these values are represented by two voltage levels. • In TTL convention, these values are nominally 5V and 0V, respectively. • Note that in a binary waveform, knowledge of the transition between one state and another is equivalent to knowledge of the state. Thus, digital logic circuits can operate by detecting transitions between voltage levels. The transitions are called edges and can be positive (f0 to f1) or negative (f1 to f0). 1 positive negative positive edge 0 edges edge 5 Bipolar Junction Transistors The bipolar junction transistor (BJT) is the salient invention that led to the electronic age, integrated circuits, and ultimately the entire digital world. The transistor is the principal active device in electrical circuits. When inputs are kept relatively small, the transistor serves as an amplifier. When the transistor is overdriven, it acts as a switch, a mode most useful in digital electronics. -

Npn Transistor Pnp Transistor

ELL 100 - Introduction to Electrical Engineering LECTURE 23: BIPOLAR JUNCTION TRANSISTOR (BJT) 1 CONTENTS • Introduction • Construction & working principle of BJT • Common-base and common-emitter circuits 2 BJT INTRODUCTION • Bipolar: Both electrons and holes (positively charged quasi- particles, absence of electron) contribute to current flow • Junction: Consists of an n- (or p-) type silicon sandwiched between two p- (or n-) type silicon regions • Transistor: 3-terminal device (Base, Emitter, Collector) Two types: npn & pnp 3 Bipolar Junction Transistor (BJT) 4 Various Types of General-Purpose or Switching Transistors: (a) Low Power (b) Medium Power (c) Medium to high power 5 First Working Transistor, Invented in 1947. Earliest Raytheon Blue transistors, Replica of 1st device made by first appearing in 1955 Shockley, Bardeen & Brattain at Bell Labs 6 Applications: Transistor As Switch 7 Applications: Transistor As Relay (Switch) Single channel 5V relay breakout board 8 Applications: Transistor As Amplifier TDA7297 Power Amplifier & Audio amplifier Module 9 Applications: Transistors in Radio 10 Applications: Transistor in Oscillator Colpitts Oscillator 11 Applications: Transistor in Oscillator Astable Multivibrator 12 Transistors in Timer Circuits 13 Transistor As NOT Gate 14 Transistors in NAND Gate 15 Bipolar Junction Transistor (BJT) The three terminals of the BJT are called the Base (B), the Collector (C) and the Emitter (E). n p p n n p npn transistor pnp transistor 16 Bipolar Junction Transistor (BJT) npn pnp 17 p-n-p Transistor IE, IB, IC – Emitter, Base and Collector currents VEB, VCB, VCE – Emitter-Base, Collector-Base and Collector-Emitter voltages 18 n-p-n Transistor IE, IB, IC – Emitter, Base and Collector currents VEB, VCB, VCE – Emitter-Base, Collector-Base and Collector-Emitter voltages 19 BJT Construction 20 Bipolar Junction Transistor (BJT) Basic Principle The voltage between two terminals (B and E) controls the current through the third terminal (C). -

Thyristors.Pdf

THYRISTORS Electronic Devices, 9th edition © 2012 Pearson Education. Upper Saddle River, NJ, 07458. Thomas L. Floyd All rights reserved. Thyristors Thyristors are a class of semiconductor devices characterized by 4-layers of alternating p and n material. Four-layer devices act as either open or closed switches; for this reason, they are most frequently used in control applications. Some thyristors and their symbols are (a) 4-layer diode (b) SCR (c) Diac (d) Triac (e) SCS Electronic Devices, 9th edition © 2012 Pearson Education. Upper Saddle River, NJ, 07458. Thomas L. Floyd All rights reserved. The Four-Layer Diode The 4-layer diode (or Shockley diode) is a type of thyristor that acts something like an ordinary diode but conducts in the forward direction only after a certain anode to cathode voltage called the forward-breakover voltage is reached. The basic construction of a 4-layer diode and its schematic symbol are shown The 4-layer diode has two leads, labeled the anode (A) and the Anode (A) A cathode (K). p 1 n The symbol reminds you that it acts 2 p like a diode. It does not conduct 3 when it is reverse-biased. n Cathode (K) K Electronic Devices, 9th edition © 2012 Pearson Education. Upper Saddle River, NJ, 07458. Thomas L. Floyd All rights reserved. The Four-Layer Diode The concept of 4-layer devices is usually shown as an equivalent circuit of a pnp and an npn transistor. Ideally, these devices would not conduct, but when forward biased, if there is sufficient leakage current in the upper pnp device, it can act as base current to the lower npn device causing it to conduct and bringing both transistors into saturation. -

Basic Operational Amplifier Circuits

Basic Operational Amplifier Circuits Electronic Devices, 9th edition © 2012 Pearson Education. Upper Saddle River, NJ, 07458. Thomas L. Floyd All rights reserved. Comparators A comparator is a specialized nonlinear op-amp circuit that compares two input voltages and produces an output state that indicates which one is greater. Comparators are designed to be fast and frequently have other capabilities to optimize the comparison function. Comparator Differentiator An example of a – C Retriggerable one-shot comparator application is + R shown. The circuit detects Vin a power failure in order to take an action to save data. As long as the comparator senses Vin , the output will be a dc level. Electronic Devices, 9th edition © 2012 Pearson Education. Upper Saddle River, NJ, 07458. Thomas L. Floyd All rights reserved. Comparators Operational amplifiers are often used as comparators to compare the amplitude of one voltage with another. In this application, op-amps are used in the open-loop configuration. Due to high open-loop gain, an op-amp can detect very tiny differences at the input. The input voltage is applied to one terminal while a reference voltage on the other terminal. Comparators are much faster than op-amps. Op-amps can be used as comparators but comparators cannot be used as op-amps. Electronic Devices, 9th edition © 2012 Pearson Education. Upper Saddle River, NJ, 07458. Thomas L. Floyd All rights reserved. Zero-Level Detection Figure 1(a) shows an op-amp circuit to detect when a signal crosses zero. This is called a zero-level detector. Notice that inverting input is grounded to produce a zero level and the input signal is applied to the noninverting terminal. -

Chapter 3: Oscillators and Waveform-Shaping Circuits

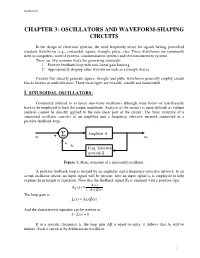

mywbut.com CHAPTER3:OSCILLATORSANDWAVEFORM-SHAPING CIRCUITS Inthedesignofelectronicsystems,theneed frequentlyarises forsignals havingprescribed standardwaveforms(e.g.,sinusoidal, square,triangle,pulse,etc).Thesewaveformsarecommonly usedincomputers,controlsystems,communicationsystemsandtestmeasurementsystems. Therearetwocommonwaysforgeneratingsinusoids: 1. Positivefeedbackloopwithnon-lineargainlimiting 2. Appropriatelyshapingotherwaveformssuchasatrianglewaves. Circuitsthatdirectlygeneratesquare,triangleandpulsewaveformsgenerallyemploycircuit blocksknownasmultivibrators.Threebasictypesarebistable,astableandmonostable. I.SINUSOIDALOSCILLATORS: Commonly referred to as linear sine-wave oscillators although some forms of non-linearity havetobeemployedtolimittheoutputamplitude.Analysisofthecircuitsismoredifficultass-plane analysis cannot be directly applied to the non-linear part of the circuit. The basic structure of a sinusoidal oscillator consists of an amplifier and a frequency selective network connected in a positivefeedbackloop. AmplifierA xS + Σ xO + xf Freq.Selective networkβ Figure1:Basicstructureofasinusoidaloscillator. Apositive-feedbackloopisformedbyanamplifierandafrequency-selectivenetwork.Inan actualoscillatorcircuit,noinputsignalwillbepresent;hereaninputsignalxsisemployedtohelp explaintheprincipleofoperation.NotethatthefeedbacksignalXFissummedwithapositivesign: A(s) A (s) = f 1− A(s) β (s) Theloopgainis: )s(L =A(s) β (s) Andthecharacteristicequationcanbewrittenas: 1-L(s)=0 If at a specific frequency -

Relaxation Oscillators and Networks

In J.G. Webster (ed.), Wiley Encyclopedia of Electrical and Electronics Engineering, Wiley & Sons, vol. 18, pp. 396-405, 1999 Relaxation Oscillators and Networks DeLiang Wang Department of Computer and Information Science and Center for Cognitive Science The Ohio State University Columbus, OH 43210-1277 Relaxation oscillations comprise a large class of nonlinear dynamical systems, and arise naturally from many physical systems such as mechanics, biology, chemistry, and engineering. Such periodic phenomena are characterized by intervals of time during which little happens, interleaved with intervals of time during which considerable changes take place. In other words, relaxation oscillations exhibit more than one time scale. The dynamics of a relaxation oscillator is illustrated by the mechanical system of a seesaw in Figure 1. At one side of the seesaw is there a water container which is empty at the beginning; in this situation the other side of the seesaw touches the ground. As the weight of water dripping from a tap into the container exceeds that of the other side, the seesaw flips and the container side touches the ground. At this moment, the container empties itself, and the seesaw returns quictly to its original position and the process repeats. AAA AAA Figure 1. An example of a relaxation oscillator: a seesaw with a water container at one end (adapted from (4)). Relaxation oscillations were first observed by van der Pol (1) in 1926 when studying properties of a triode circuit. Such a circuit exhibits self-sustained oscillations. van der Pol discovered that for a certain range of the system parameters the oscillation is almost sinusoidal, but for a different range the oscillation exhibits abrupt changes. -

Experiment No: 14 ASTABLE MULTIVIBRATOR USING IC

Experiment No: 14 ASTABLE MULTIVIBRATOR USING IC 555 AIM To design and set up astable multivibrator of 1000 Hz frequency and 60% duty cycle using IC 555 THEORY IC 555 timer is an analog IC used for generating accurate time delay or oscillations. The entire circuit is usually housed in an 8-pin package as specified in figures 1 & 2 below. A series connection of three resistors inside the IC sets the reference voltage levels to the two 2 1 comparators at V and V , the output of these comparators setting or resetting the flip- 3 CC 3 CC flop unit. The output of the flip-flop circuit is then brought out through an output buffer stage. In the stable state the 푄 output of the flip-flop is high (ie Q low). This makes the output (pin 3) low because of the buffer which basically is an inverter.The flip-flop circuit also operates a transistor inside the IC, the transistor collector usually being driven low to discharge a timing capacitor connected at pin 7. The description of each pin s described below, Pin 1: (Ground): Supply ground is connected to this pin. Pin 2: (Trigger): This pin is used to give the trigger input in monostable multivibrator. When trigger of amplitude greater than (1/3)Vcc is applied to this terminal circuit switches to quasi-stable state. Pin 3: (Output) Pin 4 (Reset): This pin is used to reset the output irrespective of input. A logic low at this pin will reset output. For normal operation pin 4 is connected to Vcc. -

Analog Integrated Circuits

Analog Integrated Circuits Jieh-Tsorng Wu 6 de febrero de 2003 1. Introduction Complete Small-Signal Model with Extrinsic Components 2. PN Junctions and Bipolar Junction Transis- tors Typical values of Extrinsic Components PN Junctions 3. MOS Transistors Small-Signal Junction Capacitance MOS Transistors Large-Signal Junction Capacitance Strong Inversion PN Junction in Forward Bias Channel Charge Transfer Characteristics PN Junction Avalanche Breakdown Simplified Channel Charge Transfer Charac- PN Junction Breakdown teristics Bipolar Junction Transistor (BJT) MOST I-V Characteristics Minority Carrier Current in the Base Region Threshold Voltage Gummel Number (G) Square-Law I-V Characteristics Base Transport Current Channel-Length Modulation Forward Current Gain MOST Small-Signal Model in Saturation Re- gion BJT DC Large-Signal Model in Forward- Active Region OST Small-Signal Model in Saturation Re- gion Dependence of BF on Operating Condition MOST Small-Signal Capacitances in Satura- Collector Voltage Effects tion Region Base Transport Model Channel Capacitance in Saturation Region Ebers-Moll Model Complete MOST Small-Signal Model in Sat- Leakage Current uration Region Common-Base Transistor Breakdown MOST Small-Signal Model in Triode Region Common-Emitter Transistor Breakdown MOST Small-Signal Model in Cutoff Region Small-Signal Model of Forward-Biased BJT Carrier Velocity Saturation Charge Storage Effects of Carrier Velocity Saturation 1 Hot Carriers 5. Single-Transistor Gain Stages Short-Channel Effects Unilateral Two-Port Network Subthreshold -

Nanoelectronic Mixed-Signal System Design

Nanoelectronic Mixed-Signal System Design Saraju P. Mohanty Saraju P. Mohanty University of North Texas, Denton. e-mail: [email protected] 1 Contents Nanoelectronic Mixed-Signal System Design ............................................... 1 Saraju P. Mohanty 1 Opportunities and Challenges of Nanoscale Technology and Systems ........................ 1 1 Introduction ..................................................................... 1 2 Mixed-Signal Circuits and Systems . .............................................. 3 2.1 Different Processors: Electrical to Mechanical ................................ 3 2.2 Analog Versus Digital Processors . .......................................... 4 2.3 Analog, Digital, Mixed-Signal Circuits and Systems . ........................ 4 2.4 Two Types of Mixed-Signal Systems . ..................................... 4 3 Nanoscale CMOS Circuit Technology . .............................................. 6 3.1 Developmental Trend . ................................................... 6 3.2 Nanoscale CMOS Alternative Device Options ................................ 6 3.3 Advantage and Disadvantages of Technology Scaling . ........................ 9 3.4 Challenges in Nanoscale Design . .......................................... 9 4 Power Consumption and Leakage Dissipation Issues in AMS-SoCs . ................... 10 4.1 Power Consumption in Various Components in AMS-SoCs . ................... 10 4.2 Power and Leakage Trend in Nanoscale Technology . ........................ 10 4.3 The Impact of Power Consumption