Am572x Sitara™ Processors Silicon Revision 2.0 Datasheet

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Pin-Outs (PDF)

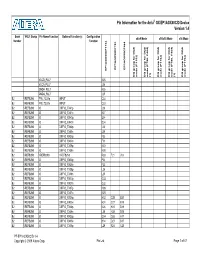

Pin Information for the Arria® GX EP1AGX50C/D Device Version 1.4 Bank VREF Group Pin Name/Function Optional Function(s) Configuration x8/x9 Mode x16/x18 Mode x36 Mode Number Function EP1AGX50DF780 EP1AGX50CF484 EP1AGX50DF1152 DQ group for DQS DQS for group DQ (F1152) mode DQS for group DQ (F780, F484) mode (1) DQS for group DQ (F1152) mode DQS for group DQ (F780, F484) mode (1) DQS for group DQ (F1152) mode VCCD_PLL7 K25 VCCA_PLL7 J26 GNDA_PLL7 K26 GNDA_PLL7 J25 B2 VREFB2N0 FPLL7CLKp INPUT C34 B2 VREFB2N0 FPLL7CLKn INPUT C33 B2 VREFB2N0 IO DIFFIO_TX41p J28 B2 VREFB2N0 IO DIFFIO_TX41n K27 B2 VREFB2N0 IO DIFFIO_RX40p E34 B2 VREFB2N0 IO DIFFIO_RX40n D34 B2 VREFB2N0 IO DIFFIO_TX40p J30 B2 VREFB2N0 IO DIFFIO_TX40n J29 B2 VREFB2N0 IO DIFFIO_RX39p F32 B2 VREFB2N0 IO DIFFIO_RX39n F31 B2 VREFB2N0 IO DIFFIO_TX39p K30 B2 VREFB2N0 IO DIFFIO_TX39n K29 B2 VREFB2N0 VREFB2N0 VREFB2N0 R30 T21 J18 B2 VREFB2N0 IO DIFFIO_RX38p F34 B2 VREFB2N0 IO DIFFIO_RX38n F33 B2 VREFB2N0 IO DIFFIO_TX38p L26 B2 VREFB2N0 IO DIFFIO_TX38n L25 B2 VREFB2N0 IO DIFFIO_RX37p G33 B2 VREFB2N0 IO DIFFIO_RX37n G32 B2 VREFB2N0 IO DIFFIO_TX37p M26 B2 VREFB2N0 IO DIFFIO_TX37n M25 B2 VREFB2N0 IO DIFFIO_RX36p H32 C28 B20 B2 VREFB2N0 IO DIFFIO_RX36n H31 C27 B19 B2 VREFB2N0 IO DIFFIO_TX36p K28 H23 D19 B2 VREFB2N0 IO DIFFIO_TX36n L28 H22 D18 B2 VREFB2N0 IO DIFFIO_RX35p G34 D28 A17 B2 VREFB2N0 IO DIFFIO_RX35n H34 D27 B17 B2 VREFB2N0 IO DIFFIO_TX35p L29 F24 C20 PT-EP1AGX50C/D-1.4 Copyright © 2009 Altera Corp. Pin List Page 1 of 47 Pin Information for the Arria® GX EP1AGX50C/D Device Version -

12. FORMULATION of the URBAN TRANSPORT MASTER PLAN Development of the RSTP Urban Transportation Master Plan (1) Methodology

The Project on The Revision and Updating of the Strategic Transport Plan for Dhaka (RSTP) Final Report 12. FORMULATION OF THE URBAN TRANSPORT MASTER PLAN Development of the RSTP Urban Transportation Master Plan (1) Methodology The development of the RSTP Urban Transportation Master Plan adopted the following methodology (see Figure 12.1): (i) Elaborate the master plan network through a screen line analysis by comparing the network capacity and future demand. (ii) Identify necessary projects to meet future demand at the same time avoiding excessive capacity. (iii) Conducts economic evaluation of each project to give priority on projects with higher economic return. (iv) Conduct preliminary environmental assessment of every project and consider countermeasures against environmental problems, if any. (v) Make a final prioritization of all physical projects by examining their respective characteristics from different perspectives. (vi) Classify the projects into three categories, namely short-, medium- and long-term projects, by considering the financial constraints. (vii) Prepare an action plan for short-term projects together with “soft” measures. Mid-term Project Source: RSTP Study Team Figure 12.1 Development Procedure for the Master Plan 12-1 The Project on The Revision and Updating of the Strategic Transport Plan for Dhaka (RSTP) Final Report (2) Output of the Transportation Network Plan The RSTP urban transportation network plan was developed based on a review and a modification of the STP network plan. The main points of the modification or adoption of the STP network master plan are as follows: i. Harmonization with future urban structure, land-use plan and development of network plan. -

Ilex Specifications

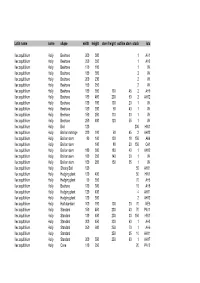

Latin name name shape width height stem height outline stem stock lots Ilex aquifolium Holly Beehave 200 300 1 AH1 Ilex aquifolium Holly Beehave 250 350 1 AH2 Ilex aquifolium Holly Beehave 170 180 1 VK Ilex aquifolium Holly Beehave 180 350 2 VK Ilex aquifolium Holly Beehave 200 230 2 VK Ilex aquifolium Holly Beehave 150 250 2 VK Ilex aquifolium Holly Beehave 180 350 130 45 2 AH9 Ilex aquifolium Holly Beehave 180 450 200 60 2 AH12 Ilex aquifolium Holly Beehave 130 180 100 20 1 VK Ilex aquifolium Holly Beehave 180 200 50 40 1 VK Ilex aquifolium Holly Beehave 150 250 110 30 1 VK Ilex aquifolium Holly Beehave 250 400 120 55 1 VK Ilex aquifolium Holly Ball 120 200 HW1 Ilex aquifolium Holly Ball on mini tige 220 180 60 45 2 AH12 Ilex aquifolium Holly Ball on stem 80 160 100 18 150 AK4 Ilex aquifolium Holly Ball on stem 160 80 20 150 CA1 Ilex aquifolium Holly Ball on stem 180 300 180 40 1 AH12 Ilex aquifolium Holly Ball on stem 180 250 140 30 1 VK Ilex aquifolium Holly Ball on stem 150 250 150 35 1 VK Ilex aquifolium Holly Shruby Ball 120 55 AH11 Ilex aquifolium Holly Hedging plant 120 400 50 HW1 Ilex aquifolium Holly Hedging plant 60 350 70 AH5 Ilex aquifolium Holly Beehave 130 300 15 AH6 Ilex aquifolium Holly Hedging plant 120 400 4 AH11 Ilex aquifolium Holly Hedging plant 120 350 2 AH12 Ilex aquifolium Holly Half standard 100 180 100 20 70 NE5 Ilex aquifolium Holly Standard 150 450 200 40 70 PA11 Ilex aquifolium Holly Standard 130 450 200 30 150 HW1 Ilex aquifolium Holly Standard 300 450 200 60 1 AH3 Ilex aquifolium Holly Standard 350 600 -

Enroll Today Easy Online Enrollment Cvtech.Edu Short-Term Classes

ADULT CAREER AND COMMUNITY DEVELOPMENT CANADIAN VALLEY TECHNOLOGY CENTER FALL 2021 JULY- DECEMBER ENROLL TODAY EASY ONLINE ENROLLMENT CVTECH.EDU SHORT-TERM CLASSES CHICKASHA COWAN EL RENO 405.224.7220 405.345.3333 405.262.2629 FALL 2021 CATALOG TABLE OF CONTENTS SHORT-TERM COURSES | JULY-DECEMBER ONLINE & BLENDED DANCING / MUSIC ....................................................4 FABRIC / YARN ...........................................................4 ALL ONLINE & BLENDED COURSES .................. 2 HEALTH / WELLNESS. ............................................. 5 BUSINESS HOME / AUTO MAINTENANCE. ........................... 5 & COMPUTERS LANGUAGE ................................................................ 5 MISCELLANEOUS .................................................... 5 ACCOUNTING / QUICKBOOKS ............................ 2 PERSONAL FINANCE. ............................................. 5 COMPUTER BASICS ................................................ 2 WRITING...................................................................... 5 COMPUTER CERTIFICATIONS .............................. 2 MICROSOFT OFFICE ............................................... 2 MODERN DESIGN / CADD ..................................2-3 TRADE, SAFETY & INDUSTRY HEALTH AUTOMOTIVE / DRIVING ....................................... 5 CPR / FIRST AID .........................................................3 ENERGY INDUSTRY ................................................. 5 DENTAL FIELD ............................................................3 -

Connecting Bangladesh: Economic Corridor Network

Connecting Bangladesh: Economic Corridor Network Economic corridors are anchored on transport corridors, and international experience suggests that the higher the level of connectivity within and across countries, the higher the level of economic growth. In this paper, a new set of corridors is being proposed for Bangladesh—a nine-corridor comprehensive integrated multimodal economic corridor network resembling the London Tube map. This paper presents the initial results of the research undertaken as an early step of that development effort. It recommends an integrated approach to developing economic corridors in Bangladesh that would provide a strong economic foundation for the construction of world-class infrastructure that, in turn, could support the growth of local enterprises and attract foreign investment. About the Asian Development Bank COnnecTING BANGLADESH: ADB’s vision is an Asia and Pacific region free of poverty. Its mission is to help its developing member countries reduce poverty and improve the quality of life of their people. Despite the region’s many successes, it remains home to a large share of the world’s poor. ADB is committed to reducing poverty through inclusive economic growth, environmentally sustainable growth, and regional integration. ECONOMIC CORRIDOR Based in Manila, ADB is owned by 67 members, including 48 from the region. Its main instruments for helping its developing member countries are policy dialogue, loans, equity investments, guarantees, grants, NETWORK and technical assistance. Mohuiddin Alamgir -

July 2016 Volume 3 No 3

6 VOLUME 3 NO 3 JULY 2016 DHAKA CENTRAL INTERNATIONAL MEDICAL COLLEGE JOURNAL (APPROVED BY BMDC) July 2016, Vol. 3 No. 3 Contents From the Desk of Editor-in-Chief 3 Instructions for Authors 4 Editorial Novel Treatment of Diabetic Nephropathy 12 Original Articles Incidence of Malignancy in Thyroid Nodule 14 Abedin SAMA, Alam MM, Islam MS, Fakir MAY Dyslipidemia and Atherogenic Index among the 21 Young Female Doctors ofBangladesh. Khanduker S, Hoque MM, Khanduker N, Chowdhury MAA, Nazneen M A Study on Stroke in Young Patients due to Cardiac 26 Disease in a Tertiary Care Hospital in Dhaka City Mukta M, Mohammad QD, Mir AS Variation of Transverse Diameter ofDry Ossified 33 Human Atlas Vertebra of Male and Female Rahman S, Ara S, Sayeed S, Rashid S, Ferdous Z, Kashem K Study on Health Effects of Teenage Pregnancies among the Patients 36 Attending Antenatal Care Centre of Chittagong Medical College Hospital Tarafdar MA, Begum N, Das SR, Begum S, Sultana A, Rahman R, Begum R Identification ofDifferent Clinical Features and Complications of 41 Type 2 Diabetes Mellitus in Bengaladeshi Males Begum F, Shamim KM, Akter S, Hossain S, Nazma N, Afrin M, Moureen A Review Articles Female Genital Tuberculosis- A Review Article 46 Shaheed S, Mamun SMAA, Khanom M Case Reports Round Worm induced Acute Appendicitis- an Incidental 51 Finding during Colonoscopy Masum QAA, Islam MN 1 Dhaka Central International Medical College Journal Vol.13 No. 3July 2016 An Official Organ of Dhaka Central International Medical College CHIEF PATRON ADVISORS The Dhaka Central International Prof. Md. Anwarul Islam Md. -

UNC Parking Zone Map UNC Transportation & Parking

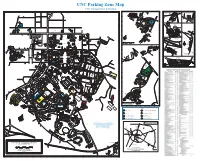

UNC Parking Zone Map UNC Transportation & Parking Q R S T U V W X Y Z A B C D E F G H I J K L M N O P 26 **UNC LEASES SPACE CAROLINA . ROAD IN THESE BUILDINGS 21 21 MT HOMESTEAD NORTH LAND MGMT. PINEY OPERATIONS CTR. VD. (NC OFFICE HORACE WILLIAMS AIRPORT VD., HILL , JR. BL “RR” 41 1 1 Resident 41 CommuterRR Lot R12 UNC VD AND CHAPEL (XEROX) TE 40 MLK BL A PRINTING RIVE EXTENSION MLK BL ESTES D SERVICES TIN LUTHER KING TERST PLANT N O I AHEC T EHS HOMESTEAD ROAD MAR HANGER VD. 86) O I-40 STORAGE T R11 TH (SEE OTHER MAPS) 22 22 O 720, 725, & 730 MLK, JR. BL R1 T PHYSICAL NOR NORTH STREET ENVRNMEN HL .3 MILES TO TH. & SAFETY ESTES DRIVE 42 COMMUTER LOT T. 42 ER NC86 ELECTRICAL DISTRICENTBUTION OPERATIONS SURPLUS WA REHOUSE N1 ST GENERAL OREROOM 2 23 23 2 R1 CHAPEL HILL ES MLK JR. BOULE NORTH R1 ARKING ARD ILITI R1 / R2OVERFLOW ZONEP V VICES C R A F SHOPS GY SE EY 43 RN 43 ENERBUILDING CONSTRUCTION PRITCHARD STREET R1 NC 86 CHURCH STREET . HO , JR. BOULE ES F R1 / V STREET SER L BUILDING VICE ARD A ST ATIO GI EET N TR AIRPOR R2 S T DRIVE IN LUTHER KING BRANCH T L MAR HIL TH WEST ROSEMARY STREET EAST ROSEMARY STREET L R ACILITIES DRIVE F A NO 24 STUDRT 24 TH COLUMBI IO CHAPE R ADMINIST OFF R NO BUILDINGICE ATIVE R10 1700 N9 MLK 208 WEST 3 N10 FRANKLIN ST. -

Master Plan on ASEAN Connectivity

Association of Southeast Asian Nations Master Plan on ASEAN Connectivity One Vision, One Identity, One Community i HA NOI DECLARATION ON THE ADOPTION OF THE MASTER PLAN ON ASEAN CONNECTIVITY WE, the Heads of State/Government of Brunei Darussalam, the Kingdom of Cambodia, the Republic of Indonesia, the Lao People’s Democratic Republic, Malaysia, the Union of Myanmar, the Republic of the Philippines, the Republic of Singapore, the Kingdom of Thailand and the Socialist Republic of Viet Nam, on the occasion of the 17th ASEAN Summit; Recalling the ASEAN Leaders’ Statement on ASEAN Connectivity issued in Cha-am Hua Hin, Thailand, on 24 October 2009; Reaffirming that enhancing intra-regional connectivity within ASEAN would benefit all ASEAN Member States through enhanced trade, investment, tourism, people-to-people exchanges, and development which would complement the ongoing regional efforts to realise a people-oriented ASEAN Community by 2015; Welcoming the work of the High Level Task Force on ASEAN Connectivity in developing the Master Plan on ASEAN Connectivity with the ASEAN Secretariat and relevant sectoral bodies, in cooperation with international organisations such as Asian Development Bank (ADB), Economic Research Institute for ASEAN and East Asia (ERIA), United Nations Economic and Social Commission for Asia and the Pacific (ESCAP) and World Bank; Recognising that the Master Plan on ASEAN Connectivity will promote economic growth, narrow development gaps, ASEAN integration and Community building process, enhance competitiveness of ASEAN, promote deeper social and cultural understanding as well as greater people mobility and connect its Member States within the region and with the rest of the world; Expressing appreciation for the support shown by our Dialogue Partners towards the ASEAN Connectivity initiative and their readiness to partner with ASEAN in the implementation of the Master Plan. -

Oneida County Legislative District 1 Date: April 1, 2014

CARTER RD D D 5 R R 6 B T 3 L L I E P L P S A T K E U C E T 5 C 6 K R D D U W O 3 M R W O D E O R S E R A K T R L Y T N C E E A A S E U D H G R I C Y T O I E O E D E R ID R A R A T R N N R F D C R D E W E O R N S E G S N D R H R E T D T E E S E A L D H S E E R I R T O S T U R I 10 D R M S N W I S R A G E A C N L H R T Y Verona D R AC11 AC12 AC13 AC14 AC15 E AC16 AC17 AC18 H AC19 R C R W H T L D R E I IL D L D D R L S E VERONA 4 R E B R M U N L R D I E T A K C K H A C O O U R S 6 R TA R N D TE 2 D R T OU R LO TE W E 31 Y EL T L U D R D R D O E R R L L B N R O E S T G E N T W E D I B A R L T O D S R NS E D T A D S A M M R R R T H 4 WESTMORELAND 3 R E C E N R RO A E N R E U FR TE N D U G Y T H B R 31 D D R S I I L D E R Y 5 YD R L R 6 L BO R D 5 L R N 3 I I 6 E SPR R H A 3 ING RD M M G E D S 3 R M E L I E T O E W N U T R EL I F U L I O RD E S L R O PR I-90 R D R ING STAT D E RD I- E R T E 90 OU T T A D AD11 AD12 AD13 E AD14 T A AD15 AD16 AD17 AD18 AD19 31 S T R S I-90 I-90 H 0 T I-9 L I OW D E R M S LL S PR VERONA 3 L ING H RD IL 0 OUS H I-90 I-9 E RD FOSTE D R CORN N ERS RD A T S S N D I R A E I-90 R M O Y I-90 O IL DA 5 M D D R 36 I-90 I-90 R E S A T -90 MIT G I C HEL S E U L R WN L R D O I O D T NE N R I D R I-90 I R RD S K SK KINNE R N 0 E N T RD -9 T 5 E I I E 0 L A 6 R L 9 S A J I- P 3 D D T T S R WESTMORELAND 4 D S E Y R E A LL R E W T N E C NL D T H O O E U H C L T F I R O R I L L M E O I R O L L X M W U D IL HIL E L T R R O M 0 T I-9 A E D E O R IN AE11 AE12 AE1R 3 T AE14 D AE15 AE16 L AE17 AE18 AE19 R D S R 3 N C D 1 E EN OW TE -

CADP 2.0) Infrastructure for Connectivity and Innovation

The Comprehensive Asia Development Plan 2.0 (CADP 2.0) Infrastructure for Connectivity and Innovation November 2015 Economic Research Institute for ASEAN and East Asia The findings, interpretations, and conclusions expressed herein do not necessarily reflect the views and policies of the Economic Research Institute for ASEAN and East Asia, its Governing Board, Academic Advisory Council, or the institutions and governments they represent. All rights reserved. Material in this publication may be freely quoted or reprinted with proper acknowledgement. Cover Art by Artmosphere ERIA Research Project Report 2014, No.4 National Library of Indonesia Cataloguing in Publication Data ISBN: 978-602-8660-88-4 Contents Acknowledgement iv List of Tables vi List of Figures and Graphics viii Executive Summary x Chapter 1 Development Strategies and CADP 2.0 1 Chapter 2 Infrastructure for Connectivity and Innovation: The 7 Conceptual Framework Chapter 3 The Quality of Infrastructure and Infrastructure 31 Projects Chapter 4 The Assessment of Industrialisation and Urbanisation 41 Chapter 5 Assessment of Soft and Hard Infrastructure 67 Development Chapter 6 Three Tiers of Soft and Hard Infrastructure 83 Development Chapter 7 Quantitative Assessment on Hard/Soft Infrastructure 117 Development: The Geographical Simulation Analysis for CADP 2.0 Appendix 1 List of Prospective Projects 151 Appendix 2 Non-Tariff Barriers in IDE/ERIA-GSM 183 References 185 iii Acknowledgements The original version of the Comprehensive Asia Development Plan (CADP) presents a grand spatial design of economic infrastructure and industrial placement in ASEAN and East Asia. Since the submission of such first version of the CADP to the East Asia Summit in 2010, ASEAN and East Asia have made significant achievements in developing hard infrastructure, enhancing connectivity, and participating in international production networks. -

Vol. 27 (T1) 2019 Vol

Pertanika Journal of Social Sciences & Humanities Vol. 27 (T1) 2019 Journal of Social Sciences & Humanities Contents Forward i Abu Bakar Salleh The Effect of Brand Equity and Perceived Value to Marketing Mix 1 Faransyah Jaya, Muhtosim Arief, Pantri Heriyati and Dyah Budiastuti Enhancing the Employability of Graduates through an Industry-led 11 Initiative Nora Zakaria and Ramesh Nair A Comparison of Customer Attendance Motivations at Victoria Park and 27 Manning Farmers’ Markets, Perth, Western Australia Mark Azavedo and John Walsh 45 Exploratory Approach Journal of Social Sciences & Humanities Sun-Hae Hyun, Moon-Kyo Seo and Se Kyung Choi Impact of Product Costing for Branding and Business Support on Small 59 and Medium Enterprises in Malaysia 27 (T1) 2019 Vol. Diana Rose Faizal, Zariyawati Mohd Ashhari, Norazlina Kamarohim and Annuar Md Nassir Establishing Green Practice Constructs among Secondary School 75 Hanifah Mahat, Nasir Nayan, Yazid Saleh, Mohmadisa Hashim and Siti Mariam Shahirah Haron Underlying Structure of Job Competency Scale in Climate-Smart 93 Agricultural Extension Service Sulaiman Umar, Norsida Man, Nolila Mohd Nawi, Ismail Abd. Latif and Bashir Garba Muktar Practiced Culture toward Firm Competitiveness Performance: Evidence 113 from Indonesia VOL. 27 (T1) 2019 Journal of Social Sciences & Humanities Prio Utomo and Dyah Budiastuti Thematic Edition Survival through Strategic Performance Measurement System in Coal 125 Mines Nandang Sukmana, Sri Bramantoro Abdinagoro and Dyah Budiastuti Management Studies Pertanika Editorial Oce, Journal Division Oce of the Deputy Vice Chancellor (R&I) 1st Floor, IDEA Tower II UPM-MTDC Technology Centre Universiti Putra Malaysia 43400 UPM Serdang Selangor Darul Ehsan Malaysia http://www.pertanika.upm.edu.my/ E-mail: [email protected] Tel: +603 8947 1622 Journal of Social Sciences & Humanities About the Journal Overview Pertanika Journal of Social Sciences & Humanities (JSSH) is the official journal of Universiti Putra Malaysia published by UPM Press. -

Europe Price List

2019 Europe Price List EUROPE PRICE LIST 2019 Terms and Conditions of Sale Conditions générales de vente Condizioni generali di vendita Allgemeine Verkaufsbedingungen By placing an order, the customer Toutes les commandes passées Tutti gli ordini effettuati com- Mit Aufgabe einer Bestellung er- fully accepts the following Terms impliquent que l’acheteur accep- portano la piena accettazione, kennt der Kunde die folgenden and Conditions of Sale: te intégralement les Conditions da parte dell’acquirente, delle Allgemeinen Verkaufsbedingun- générales de vente suivantes : seguenti Condizioni Generali di gen in vollem Umfang an: 0. Validity Vendita: Price list valid from 18/02/2019. 0. Validité 0. Gültigkeit Tarif valable à partir de 18/02/2019. 0. Validità Die Preisliste gilt ab dem 1. Prices Listino valido dal 18/02/2019. 18/02/2019. The prices applied will be those 1. Prix valid on the date of reception of Les tarifs en vigueur s’appliquent 1. Prezzi 1. Preise the order (RRP, VAT not included). à la date de réception de la com- Verranno applicate le tariffe Es werden die Preise berechnet, All prices featured in the price list mande (prix PVPR, TVA non com- vigenti alla data di ricezione die am Tag des Auftrageingangs include the WEEE eco-fee. prise). Tous les prix indiqués dans dell’ordine (prezzi di vendita al gelten (UVP ohne Mehrwerts- la liste des tarifs comprennent pubblico consigliati, IVA esclusa). teuer). Alle angegebenen Preise 2. Delivery times l’éco-participation DEEE. Tutti i prezzi indicati nel listino sind einschließlich WEEE Gebühr. Delivery times will be confirmed at prezzi sono con contributo ECO- the moment of placing the order 2.