ADVANCED SEMICONDUCTOR DEVICES 01 Introduction

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Imperial College London Department of Physics Graphene Field Effect

Imperial College London Department of Physics Graphene Field Effect Transistors arXiv:2010.10382v2 [cond-mat.mes-hall] 20 Jul 2021 By Mohamed Warda and Khodr Badih 20 July 2021 Abstract The past decade has seen rapid growth in the research area of graphene and its application to novel electronics. With Moore's law beginning to plateau, the need for post-silicon technology in industry is becoming more apparent. Moreover, exist- ing technologies are insufficient for implementing terahertz detectors and receivers, which are required for a number of applications including medical imaging and secu- rity scanning. Graphene is considered to be a key potential candidate for replacing silicon in existing CMOS technology as well as realizing field effect transistors for terahertz detection, due to its remarkable electronic properties, with observed elec- tronic mobilities reaching up to 2 × 105 cm2 V−1 s−1 in suspended graphene sam- ples. This report reviews the physics and electronic properties of graphene in the context of graphene transistor implementations. Common techniques used to syn- thesize graphene, such as mechanical exfoliation, chemical vapor deposition, and epitaxial growth are reviewed and compared. One of the challenges associated with realizing graphene transistors is that graphene is semimetallic, with a zero bandgap, which is troublesome in the context of digital electronics applications. Thus, the report also reviews different ways of opening a bandgap in graphene by using bi- layer graphene and graphene nanoribbons. The basic operation of a conventional field effect transistor is explained and key figures of merit used in the literature are extracted. Finally, a review of some examples of state-of-the-art graphene field effect transistors is presented, with particular focus on monolayer graphene, bilayer graphene, and graphene nanoribbons. -

Evaluation of Passivation Process for Stainless Steel Hypotubes Used in Coronary Angioplasty Technique

coatings Article Evaluation of Passivation Process for Stainless Steel Hypotubes Used in Coronary Angioplasty Technique Lucien Reclaru 1,2 and Lavinia Cosmina Ardelean 2,3,* 1 Scientific Independent Consultant Biomaterials and Medical Devices, 103 Paul-Vouga, 2074 Marin-Neuchâtel, Switzerland; [email protected] 2 Multidisciplinary Center for Research, Evaluation, Diagnosis and Therapies in Oral Medicine, “Victor Babes” University of Medicine and Pharmacy Timisoara, 2 Eftimie Murgu sq, 300041 Timisoara, Romania 3 Department of Technology of Materials and Devices in Dental Medicine, “Victor Babes” University of Medicine and Pharmacy Timisoara, 2 Eftimie Murgu sq, 300041 Timisoara, Romania * Correspondence: [email protected] Abstract: In the manufacturing of hypotubes for coronary applications, austenitic steels of types 304, 304, or 316 L are being used. The manufacturing process involves bending steel strips into tubes and the continuous longitudinal welding of the tubes. Manufacturing also includes heat treatments and stretching operations to achieve an external/internal diameter of 0.35/0.23 mm, with a tolerance of +/− 0.01 mm. Austenitic steels are sensitive to localized corrosion (pitting, crevice, and intergranular) that results from the welding process and various heat treatments. An extremely important step is the cleaning and the internal and external passivation of the hypotube surface. During patient interventions, there is a high risk of metal cations being released in contact with human blood. The aim of this study was to evaluate the state of passivation and corrosion resistance by using electrochemical methods and specific intergranular corrosion tests (the Strauss test). There were difficulties in passivating the hypotubes and assessing the corrosion phenomena in the interior of the tubes. -

Si Passivation and Chemical Vapor Deposition of Silicon Nitride: Final Technical Report, March 18, 2007

A national laboratory of the U.S. Department of Energy Office of Energy Efficiency & Renewable Energy National Renewable Energy Laboratory Innovation for Our Energy Future Si Passivation and Chemical Subcontract Report NREL/SR-520-42325 Vapor Deposition of Silicon Nitride November 2007 Final Technical Report March 18, 2007 H.A. Atwater California Institute of Technology Pasadena, California NREL is operated by Midwest Research Institute ● Battelle Contract No. DE-AC36-99-GO10337 Si Passivation and Chemical Subcontract Report NREL/SR-520-42325 Vapor Deposition of Silicon Nitride November 2007 Final Technical Report March 18, 2007 H.A. Atwater California Institute of Technology Pasadena, California NREL Technical Monitor: R. Matson/F. Posey-Eddy Prepared under Subcontract No. AAT-2-31605-01 National Renewable Energy Laboratory 1617 Cole Boulevard, Golden, Colorado 80401-3393 303-275-3000 • www.nrel.gov Operated for the U.S. Department of Energy Office of Energy Efficiency and Renewable Energy by Midwest Research Institute • Battelle Contract No. DE-AC36-99-GO10337 This publication was reproduced from the best available copy Submitted by the subcontractor and received no editorial review at NREL NOTICE This report was prepared as an account of work sponsored by an agency of the United States government. Neither the United States government nor any agency thereof, nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States government or any agency thereof. -

Chapter1: Semiconductor Diode

Chapter1: Semiconductor Diode. Electronics I Discussion Eng.Abdo Salah Theoretical Background: • The semiconductor diode is formed by doping P-type impurity in one side and N-type of impurity in another side of the semiconductor crystal forming a p-n junction as shown in the following figure. At the junction initially free charge carriers from both side recombine forming negatively c harged ions in P side of junction(an atom in P -side accept electron and be comes negatively c harged ion) and po sitive ly c harged ion on n side (an atom in n-side accepts hole i.e. donates electron and becomes positively charged ion)region. This region deplete of any type of free charge carrier is called as depletion region. Further recombination of free carrier on both side is prevented because of the depletion voltage generated due to charge carriers kept at distance by depletion (acts as a sort of insulation) layer as shown dotted in the above figure. Working principle: When voltage is not app lied acros s the diode , de pletion region for ms as shown in the above figure. When the voltage is applied be tween the two terminals of the diode (anode and cathode) two possibilities arises depending o n polarity of DC supply. [1] Forward-Bias Condition: When the +Ve terminal of the battery is connected to P-type material & -Ve terminal to N-type terminal as shown in the circuit diagram, the diode is said to be forward biased. The application of forward bias voltage will force electrons in N-type and holes in P -type material to recombine with the ions near boundary and to flow crossing junction. -

MOSFET - Wikipedia, the Free Encyclopedia

MOSFET - Wikipedia, the free encyclopedia http://en.wikipedia.org/wiki/MOSFET MOSFET From Wikipedia, the free encyclopedia The metal-oxide-semiconductor field-effect transistor (MOSFET, MOS-FET, or MOS FET), is by far the most common field-effect transistor in both digital and analog circuits. The MOSFET is composed of a channel of n-type or p-type semiconductor material (see article on semiconductor devices), and is accordingly called an NMOSFET or a PMOSFET (also commonly nMOSFET, pMOSFET, NMOS FET, PMOS FET, nMOS FET, pMOS FET). The 'metal' in the name (for transistors upto the 65 nanometer technology node) is an anachronism from early chips in which the gates were metal; They use polysilicon gates. IGFET is a related, more general term meaning insulated-gate field-effect transistor, and is almost synonymous with "MOSFET", though it can refer to FETs with a gate insulator that is not oxide. Some prefer to use "IGFET" when referring to devices with polysilicon gates, but most still call them MOSFETs. With the new generation of high-k technology that Intel and IBM have announced [1] (http://www.intel.com/technology/silicon/45nm_technology.htm) , metal gates in conjunction with the a high-k dielectric material replacing the silicon dioxide are making a comeback replacing the polysilicon. Usually the semiconductor of choice is silicon, but some chip manufacturers, most notably IBM, have begun to use a mixture of silicon and germanium (SiGe) in MOSFET channels. Unfortunately, many semiconductors with better electrical properties than silicon, such as gallium arsenide, do not form good gate oxides and thus are not suitable for MOSFETs. -

Analysis of the Silicon Dioxide Passivation and Forming Gas

&RQIHUHQFH3URFHHGLQJV 6RODU:RUOG&RQJUHVV Daegu, Korea, 08 – 12 November 2015 Analysis of the Silicon Dioxide Passivation and Forming Gas Annealing in Silicon Solar Cells Izete Zanesco and Adriano Moehlecke Solar Energy Technology Nucleus (NT-Solar), Faculty of Physics, Pontifical Catholic University of Rio Grande do Sul (PUCRS), Porto Alegre (Brazil) Abstract The passivation of silicon solar cells by the deposition of SiNx anti-reflection coating is usual in the industry. However, materials such as SiO2, TiO2 and Al2O3 may be a cost-effective alternative and its analysis is mainly reported in silicon wafers. The goal of this paper is to present the development and analysis of silicon solar cells passivated with a thin layer of SiO2 as well as the evaluation of the effectiveness of the annealing step in forming gas. The dry oxidation was performed before the TiO2 anti-reflection coating deposition and the annealing in forming gas was performed in the same furnace. The temperature and time of the oxidation and the annealing step were experimentally optimized. The efficiency of 15.9 %was achieved. The highest average efficiency was found in the oxidation temperature range from 750 ºC to 800 ºC, during 7 minutes, caused by the increasing of open circuit voltage and fill factor. At short wavelengths, the internal quantum efficiency decreases slightly with the increasing of the oxidation temperature. The minority carrier diffusion length (LD) of the solar cells processed with the oxidation temperature of 800 °C was around 1890 Pm. The open circuit voltage shows a slight trend of increasing with the oxidation time. The annealing step in forming gas did not improve the average efficiency of the solar cells. -

The Reliability of the Silicon Nitride Dielectric in Capacitive MEMS

The Pennsylvania State University The Graduate School Department of Materials Science and Engineering THE RELIABILITY OF THE SILICON NITRIDE DIELECTRIC IN CAPACITIVE MEMS SWITCHES A Thesis in Materials Science and Engineering by Abuzer Dogan © 2005 Abuzer Dogan Submitted in Partial Fulfillment of the Requirements for the Degree of Master of Science August 2005 I grant The Pennsylvania State University the nonexclusive right to use this work for the University's own purposes and to make single copies of the work available to the public on a not-for-profit basis if copies are not otherwise available. Abuzer Dogan We approve the thesis of Abuzer Dogan. Date of Signature Susan Trolier-McKinstry Professor of Ceramic Science and Engineering Thesis Advisor Michael Lanagan Associate Professor of Engineering Science and Mechanics and Materials Science and Engineering Mark Horn Associate Professor of Engineering Science and Mechanics James P. Runt Professor of Polymer Science Associate Head for Graduate Studies iii ABSTRACT Silicon nitride thin film dielectrics can be used in capacitive radio frequency micro-electromechanical systems switches since they provide a low insertion loss, good isolation, and low return loss. The lifetime of these switches is believed to be adversely affected by charge trapping in the silicon nitride. These charges cause the metal bridge to be partially or fully pulled down, degrading the on-off ratio of the switch. Little information is available in the literature providing a fundamental solution to this problem. Consequently, the goals of this research were to characterize SixNy–based MIM (Metal-Insulator-Metal) capacitors and capacitive MEMS switches to measure the current-voltage response. -

The Economic Impact of Moore's Law: Evidence from When It Faltered

The Economic Impact of Moore’s Law: Evidence from when it faltered Neil Thompson Sloan School of Management, MIT1 Abstract “Computing performance doubles every couple of years” is the popular re- phrasing of Moore’s Law, which describes the 500,000-fold increase in the number of transistors on modern computer chips. But what impact has this 50- year expansion of the technological frontier of computing had on the productivity of firms? This paper focuses on the surprise change in chip design in the mid-2000s, when Moore’s Law faltered. No longer could it provide ever-faster processors, but instead it provided multicore ones with stagnant speeds. Using the asymmetric impacts from the changeover to multicore, this paper shows that firms that were ill-suited to this change because of their software usage were much less advantaged by later improvements from Moore’s Law. Each standard deviation in this mismatch between firm software and multicore chips cost them 0.5-0.7pp in yearly total factor productivity growth. These losses are permanent, and without adaptation would reflect a lower long-term growth rate for these firms. These findings may help explain larger observed declines in the productivity growth of users of information technology. 1 I would like to thank my PhD advisors David Mowery, Lee Fleming, Brian Wright and Bronwyn Hall for excellent support and advice over the years. Thanks also to Philip Stark for his statistical guidance. This work would not have been possible without the help of computer scientists Horst Simon (Lawrence Berkeley National Lab) and Jim Demmel, Kurt Keutzer, and Dave Patterson in the Berkeley Parallel Computing Lab, I gratefully acknowledge their overall guidance, their help with the Berkeley Software Parallelism Survey and their hospitality in letting me be part of their lab. -

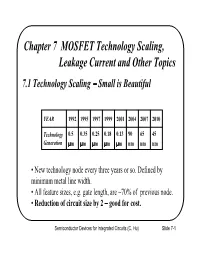

MOSFET Technology Scaling, Leakage Current, and Other Topics

Chapter 7 MOSFET Technology Scaling, Leakage Current and Other Topics 7.1 Technology Scaling Small is Beautiful YEAR 1992 1995 1997 1999 2001 2004 2007 2010 Technology 0.5 0.35 0.25 0.18 0.13 90 65 45 Generation µµµm µµµm µµµm µµµm µµµm nm nm nm • New technology node every three years or so. Defined by minimum metal line width. • All feature sizes, e.g. gate length, are ~70% of previous node. • Reduction of circuit size by 2 good for cost. Semiconductor Devices for Integrated Circuits (C. Hu) Slide 7-1 International Technology Roadmap for Semiconductors, 1999 Edition Year of Shipment 1999 2002 2005 2008 2011 2014 DRAM metal half pitch 180 130 100 70 50 35 (nm) MPU physical Lg (nm) 140 85 65 45 32 22 Tox (nm) 1.5-1.8 1.5-1.9 1-1.5 0.8-1.2 0.6-0.8 0.5-0.6 VDD 1.5-1.8 1.2-1.5 0.9-1.2 0.6-0.9 0.5-0.6 0.3-0.6 µµµ µµµ Ion,HP ( A/ m) 750/350 750/350 750/350 750/350 750/350 750/350 µµµ Ioff,HP (nA/ m) 5 10 20 40 60 160 µµµ µµµ Ion,LP ( A/ m) 490/230 490/230 490/230 490/230 490/230 490/230 µµµ Ioff,LP (pA/ m) 7 10 20 40 80 160 No known solutions •Vdd is reduced at each node to contain power consumption in spite of rising transistor density and frequency •Tox is reduced to raise I on for speed consideration Semiconductor Devices for Integrated Circuits (C. -

Resistors, Diodes, Transistors, and the Semiconductor Value of a Resistor

Resistors, Diodes, Transistors, and the Semiconductor Value of a Resistor Most resistors look like the following: A Four-Band Resistor As you can see, there are four color-coded bands on the resistor. The value of the resistor is encoded into them. We will follow the procedure below to decode this value. • When determining the value of a resistor, orient it so the gold or silver band is on the right, as shown above. • You can now decode what resistance value the above resistor has by using the table on the following page. • We start on the left with the first band, which is BLUE in this case. So the first digit of the resistor value is 6 as indicated in the table. • Then we move to the next band to the right, which is GREEN in this case. So the second digit of the resistor value is 5 as indicated in the table. • The next band to the right, the third one, is RED. This is the multiplier of the resistor value, which is 100 as indicated in the table. • Finally, the last band on the right is the GOLD band. This is the tolerance of the resistor value, which is 5%. The fourth band always indicates the tolerance of the resistor. • We now put the first digit and the second digit next to each other to create a value. In this case, it’s 65. 6 next to 5 is 65. • Then we multiply that by the multiplier, which is 100. 65 x 100 = 6,500. • And the last band tells us that there is a 5% tolerance on the total of 6500. -

Semiconductor Science for Clean Energy Technologies

LEVERAGING SEMICONDUCTOR SCIENCE FOR CLEAN ENERGY TECHNOLOGIES Keeping the lights on in the United States consumes 350 billion kilowatt hours of electricity annu- ally. Most of that light still comes from incandescent bulbs, which haven’t changed much since Thomas Edison invented them 140 years ago. But now a dramatically more efficient lighting tech- nology is seeing rapid adoption: semiconductor devices known as light-emitting diodes (LEDs) use 85 percent less energy than incandescent bulbs, last 25 times as long, and have the potential to save U.S. consumers a huge portion of the electricity now used for lighting. High-performance solar power plant in Alamosa, Colorado. It generates electricity with multi-layer solar cells, developed by the National Renewable Energy Laboratory, that absorb and utilize more of the sun’s energy. (Dennis Schroeder / National Renewable Energy Laboratory) How we generate electricity is also changing. The costs of to produce an electrical current. The challenge has been solar cells that convert light from the sun into electricity to improve the efficiency with which solar cells convert have come down dramatically over the past decade. As a sunlight to electricity and to reduce their cost for commer- result, solar power installations have grown rapidly, and cial applications. Initially, solar cell production techniques in 2016 accounted for a significant share of all the new borrowed heavily from the semiconductor industry. Silicon electrical generating capacity installed in the U.S. This solar cells are built on wafers cut from ingots of crystal- grid-scale power market is dominated by silicon solar cells, line silicon, just as are the chips that drive computers. -

Nanoelectronics

Highlights from the Nanoelectronics for 2020 and Beyond (Nanoelectronics) NSI April 2017 The semiconductor industry will continue to be a significant driver in the modern global economy as society becomes increasingly dependent on mobile devices, the Internet of Things (IoT) emerges, massive quantities of data generated need to be stored and analyzed, and high-performance computing develops to support vital national interests in science, medicine, engineering, technology, and industry. These applications will be enabled, in part, with ever-increasing miniaturization of semiconductor-based information processing and memory devices. Continuing to shrink device dimensions is important in order to further improve chip and system performance and reduce manufacturing cost per bit. As the physical length scales of devices approach atomic dimensions, continued miniaturization is limited by the fundamental physics of current approaches. Innovation in nanoelectronics will carry complementary metal-oxide semiconductor (CMOS) technology to its physical limits and provide new methods and architectures to store and manipulate information into the future. The Nanoelectronics Nanotechnology Signature Initiative (NSI) was launched in July 2010 to accelerate the discovery and use of novel nanoscale fabrication processes and innovative concepts to produce revolutionary materials, devices, systems, and architectures to advance the field of nanoelectronics. The Nanoelectronics NSI white paper1 describes five thrust areas that focus the efforts of the six participating agencies2 on cooperative, interdependent R&D: 1. Exploring new or alternative state variables for computing. 2. Merging nanophotonics with nanoelectronics. 3. Exploring carbon-based nanoelectronics. 4. Exploiting nanoscale processes and phenomena for quantum information science. 5. Expanding the national nanoelectronics research and manufacturing infrastructure network.