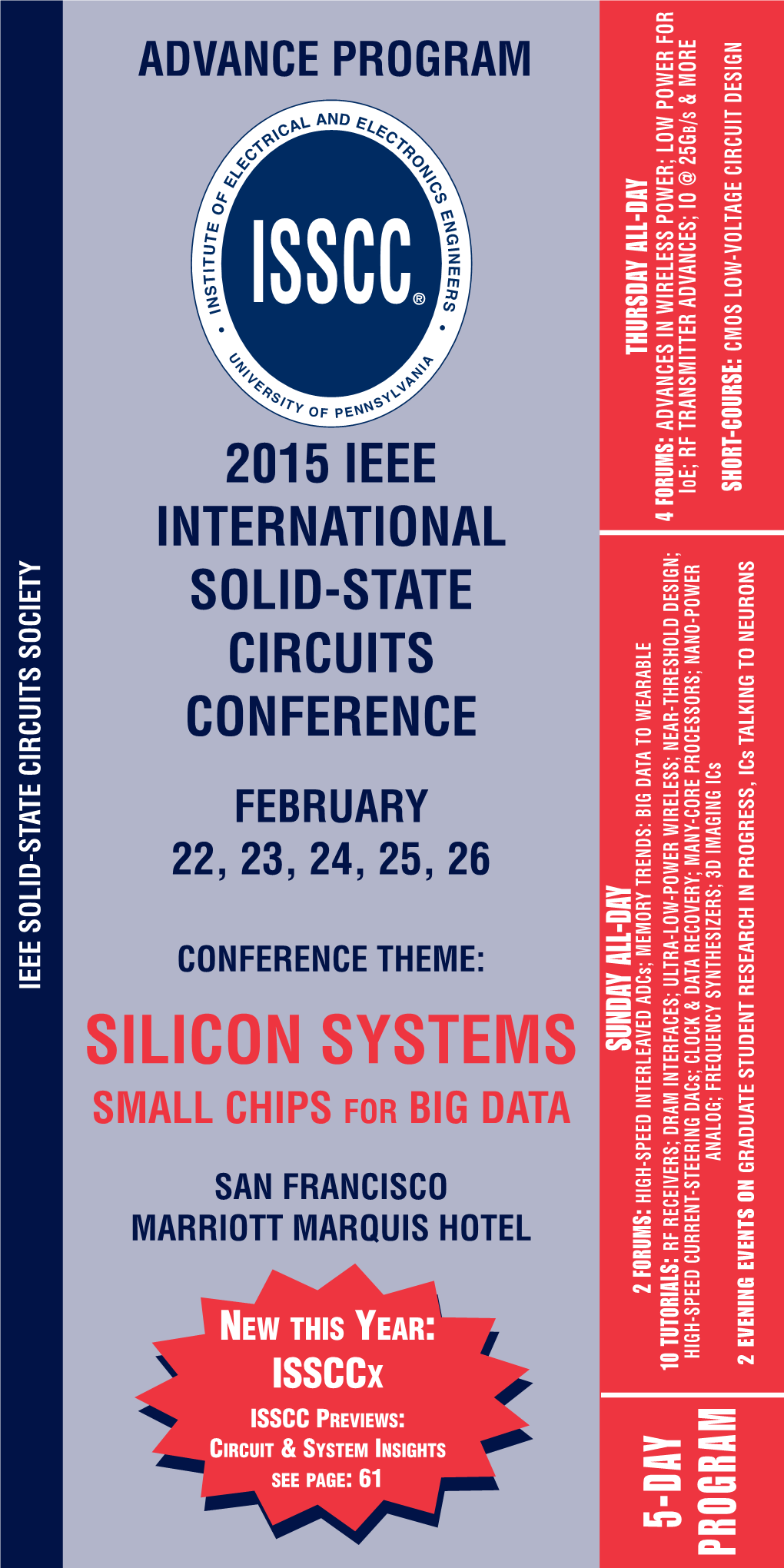

Advance Program 2015 Ieee International Solid-State

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

North American Company Profiles 8X8

North American Company Profiles 8x8 8X8 8x8, Inc. 2445 Mission College Boulevard Santa Clara, California 95054 Telephone: (408) 727-1885 Fax: (408) 980-0432 Web Site: www.8x8.com Email: [email protected] Fabless IC Supplier Regional Headquarters/Representative Locations Europe: 8x8, Inc. • Bucks, England U.K. Telephone: (44) (1628) 402800 • Fax: (44) (1628) 402829 Financial History ($M), Fiscal Year Ends March 31 1992 1993 1994 1995 1996 1997 1998 Sales 36 31 34 20 29 19 50 Net Income 5 (1) (0.3) (6) (3) (14) 4 R&D Expenditures 7 7 7 8 8 11 12 Capital Expenditures — — — — 1 1 1 Employees 114 100 105 110 81 100 100 Ownership: Publicly held. NASDAQ: EGHT. Company Overview and Strategy 8x8, Inc. is a worldwide leader in the development, manufacture and deployment of an advanced Visual Information Architecture (VIA) encompassing A/V compression/decompression silicon, software, subsystems, and consumer appliances for video telephony, videoconferencing, and video multimedia applications. 8x8, Inc. was founded in 1987. The “8x8” refers to the company’s core technology, which is based upon Discrete Cosine Transform (DCT) image compression and decompression. In DCT, 8-pixel by 8-pixel blocks of image data form the fundamental processing unit. 2-1 8x8 North American Company Profiles Management Paul Voois Chairman and Chief Executive Officer Keith Barraclough President and Chief Operating Officer Bryan Martin Vice President, Engineering and Chief Technical Officer Sandra Abbott Vice President, Finance and Chief Financial Officer Chris McNiffe Vice President, Marketing and Sales Chris Peters Vice President, Sales Michael Noonen Vice President, Business Development Samuel Wang Vice President, Process Technology David Harper Vice President, European Operations Brett Byers Vice President, General Counsel and Investor Relations Products and Processes 8x8 has developed a Video Information Architecture (VIA) incorporating programmable integrated circuits (ICs) and compression/decompression algorithms (codecs) for audio/video communications. -

Logos De Fabricantes De Semiconductores Semiconductor Manufacturers Logos

2013 Logos de fabricantes de semiconductores Semiconductor manufacturers logos EugenioNieto Vilardell Fidestec 15/03/2013 Logos de fabricantes de semiconductores 2013 2 8x8 Acer Acer Laboratories Acrian Actel ADDtek ADMtek Advanced Analogic Technology Advanced Communication Devices(ACD) Advanced Hardware Architectures Advanced Linear Devices Advanced Micro Devices(AMD) Advanced Micro Systems Advanced Monolithic Systems Advanced Power Technology Aeroflex Agere (formerly Lucent) Agilent Technologies Aimtron AITech International aJile Systems AKM Semiconductor Alchemy Semiconductor Alesis Semiconductor Allayer Communications(Now Broadcom) Allegro Microsystems Alliance Semiconductor Alogics Alpha & Omega Semiconductor Alpha Industries Alpha Microelectronics Alpha Semiconductor(Now Sipex) Altera Altima Communications AME Inc American Microsystems American Power Devices Logos de fabricantes de semiconductores 2013 3 AMIC Technology Anachip ANADIGICS Anadigm Analog Devices Analog Express Corp. Analog Integrations Corporation Analog Systems Anchor Chips Andigilog Anpec Ansaldo (Now Poseico) Apex Microtechnology API NetWorks Arizona Microtek ARK Logic Array Microsystems Astec Semiconductor AT&T ATAN Technology ATecoM ATI Technologies Atmel Auctor AudioCodes AUK Semiconductor Corp. Aura Vision Aureal Aurora Systems Austin Semiconductor Austria Mikro Systeme International Avance Logic Avantek Averlogic Avic Electronics Corp. AXElite Technology Co., Ltd BCD Semiconductor Manufacturing Limited Bel Fuse Logos de fabricantes de semiconductores 2013 -

A Decade of Semiconductor Companies : 1988 Edition

1988 y DataQuest Do Not Remove A. Decade of Semiconductor Companies 1988 Edition Components Division TABLE OF CONTENTS Page I. Introduction 1 II. Venture Capital 11 III. Strategic Alliances 15 IV. Product Analysis 56 Emerging Technology Companies 56 Analog ICs 56 ASICs 58 Digital Signal Processing 59 Discrete Semiconductors 60 Gallium Arsenide 60 Memory 62 Microcomponents 64 Optoelectronics 65 Telecommunication ICs 65 Other Products 66 Bubble Memory 67 V. Company Profiles (139) 69 A&D Co., Ltd. 69 Acrian Inc. 71 ACTEL Corporation 74 Acumos, Inc. 77 Adaptec, Inc. 79 Advanced Linear Devices, Inc. 84 Advanced Microelectronic Products, Inc. 87 Advanced Power Technology, Inc. 89 Alliance Semiconductor 92 Altera Corporation 94 ANADIGICS, Inc. 100 Applied Micro Circuits Corporation 103 Asahi Kasei Microsystems Co., Ltd. 108 Aspen Semiconductor Corporation 111 ATMEL Corporation 113 Austek Microsystems Pty. Ltd. 116 Barvon Research, Inc. 119 Bipolar Integrated Technology 122 Brooktree Corporation 126 California Devices, Ihc. 131 California Micro Devices Corporation 135 Calmos Systems, Inc. 140 © 1988 Dataquest Incorporated June TABLE OF CONTENTS (Continued) Pagg Company Profiles (Continued) Calogic Corporation 144 Catalyst Semiconductor, Inc. 146 Celeritek, Inc. ISO Chartered Semiconductor Pte Ltd. 153 Chips and Technologies, Inc. 155 Cirrus Logic, Inc. 162 Conductus Inc. 166 Cree Research Inc. 167 Crystal Semiconductor Corporation 169 Custom Arrays Corporation 174 Custom Silicon Inc. 177 Cypress Semiconductor Corporation 181 Dallas Semiconductor Corporation 188 Dolphin Integration SA 194 Elantec, Inc. 196 Electronic Technology Corporation 200 Epitaxx Inc. 202 European Silicon Structures 205 Exel Microelectronics Inc. 209 G-2 Incorporated 212 GAIN Electronics 215 Gazelle Microcircuits, Inc. 218 Genesis Microchip Inc. -

Table of Contents

PROFILES 1996 A Worldwide Survey of IC Manufacturers and Suppliers Table of Contents Alphabetical Listing of Companies....................................................................................................ix North American Company Profiles 8x8, Inc. ..................................................................................................................................1-1 ACC Microelectronics Corporation............................................................................................1-3 Actel Corporation.....................................................................................................................1-4 Allegro MicroSystems, Inc........................................................................................................1-7 Alliance Semiconductor Corporation ........................................................................................1-10 Altera Corporation....................................................................................................................1-14 AMCC (Applied Micro Circuits Corporation)...............................................................................1-18 AMD (Advanced Micro Devices, Inc.) .......................................................................................1-21 AMI (American Microsystems Inc.)...........................................................................................1-28 Anadigics, Inc..........................................................................................................................1-31 -

Integrated Circuit Test Engineering Iana.Grout Integrated Circuit Test Engineering Modern Techniques

Integrated Circuit Test Engineering IanA.Grout Integrated Circuit Test Engineering Modern Techniques With 149 Figures 123 Ian A. Grout, PhD Department of Electronic and Computer Engineering University of Limerick Limerick Ireland British Library Cataloguing in Publication Data Grout, Ian Integrated circuit test engineering: modern techniques 1. Integrated circuits - Verification I. Title 621.3’81548 ISBN-10: 1846280230 Library of Congress Control Number: 2005929631 ISBN-10: 1-84628-023-0 e-ISBN: 1-84628-173-3 Printed on acid-free paper ISBN-13: 978-1-84628-023-8 © Springer-Verlag London Limited 2006 HSPICE® is the registered trademark of Synopsys, Inc., 700 East Middlefield Road, Mountain View, CA 94043, U.S.A. http://www.synopsys.com/home.html MATLAB® is the registered trademark of The MathWorks, Inc., 3 Apple Hill Drive Natick, MA 01760- 2098, U.S.A. http://www.mathworks.com Verifault-XL®, Verilog® and PSpice® are registered trademarks of Cadence Design Systems, Inc., 2655 Seely Avenue, San Jose, CA 95134, U.S.A. http://www.cadence.com/index.aspx T-Spice™ is the trademark of Tanner Research, Inc., 2650 East Foothill Blvd. Pasadena, CA 91107, U.S.A. http://www.tanner.com/ Apart from any fair dealing for the purposes of research or private study, or criticism or review, as permitted under the Copyright, Designs and Patents Act 1988, this publication may only be reproduced, stored or transmitted, in any form or by any means, with the prior permission in writing of the publishers, or in the case of reprographic reproduction in accordance with the terms of licences issued by the Copyright Licensing Agency. -

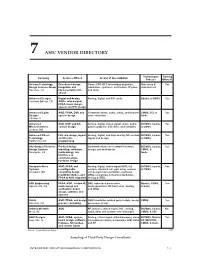

7 Asic Vendor Directory

7 ASIC VENDOR DIRECTORY Technologies Training Company Services Offered Area(s) of Specialization Process Offered? Acclaim Technology, Core-based design Cores, COT, DFT, technology migration, Gate array & Yes Design Services Group integration and simulation, synthesis, verification, IC place standard cell San Jose, CA implementation into and route silicon Advanced Designs Digital and Analog Analog, digital, and PCI cards Bipolar & CMOS Yes Colorado Springs, CO ASICs, mixed-signal, FPGA, board design, system, and PCI design Advanced Digital ASIC, FPGA, DSP, and Communications, audio, video, and forward- CMOS, ECL & Yes Designs system design error correction GaAs Chicago, IL Advanced ASIC, DSP, and full- Analog, digital, mixed-signal, video, audio, BiCMOS, bipolar, Yes Microelectronics custom design power, graphics, disk drive, and networks & CMOS Jackson, MS Advanced Silicon Full chip design, layout Analog, digital, and high-density full-custom BiCMOS, bipolar, Yes Technology and Dracula layout and design & CMOS Harbor City, CA programming Alta Group of Cadence Product design, Communications and network hardware BiCMOS, bipolar, Yes Design Systems modeling, validation, design, and multimedia CMOS, & Sunnyvale, CA methodology, tool GaAs interfaces, & communications hardware design Annapolis Micro ASIC, FPGA, and Analog, digital, mixed-signal ASIC, full BiCMOS, bipolar, Yes Systems reconfigurable custom, standard cell, gate array, custom & CMOS Annapolis, MD computing design cell design/characterization, synthesis, feasibility studies, and -

1995 Annual Report

Vision The Semiconductor Research Corporation (SRC) will be the worlds premier research management consortium for providing university-based research results in semiconductor science and technology to its members. Mission As the research arm of the semiconductor Industry Association (SIA), the SRC is a not-for-profit, tax-exempt research management consortium which helps solve the North American semiconductor Industrys technical challenges, focusing on long-range university research. Charter The SRC manages a low-overhead, industry-driven, pre-competitive research program that addresses the research needs of the SIA's National Technology Roadmap for Semiconductors. Funding for this research IS derived primarily from member fees. The SRC is not a government contractor; however, it does encourage government participation and funding support of key research programs. T ABLE OF CONTENTS What is the SRC? 1 Message from the President and the Chairman 2 1995 SRC Accomplishments ● Refocusing SRC Research Aligning With the Roadmap and Leveraging Industrys Investment 4 ● Reinforcing Student Services Meeting Industrys Demand for Qualified Graduates 5 ● Redefining Technology Transfer -The New SRC Research Catalog 6 SRC Members and Participants 7 SRC-Participating Universities and Research Institutions 8 The SRC Research Program 9 ● Design Sciences 10 ● Environment, Safety & Health Sciences 11 ● Factory Sciences 12 ● Interconnect Sciences 13 ● Lithography Sciences 14 ● Materials and Bulk Processes Sciences 15 ● Packaging Sciences 16 ● Process Integration and Device Sciences 17 SRC Technical Excellence Awards 18 SRC Industrial Mentor Program 19 SRC Intellectual Property 20 Financial Report 21 The Annual Report of the Semiconductor Research Corporation is published each year to summarize the directions and results of the SRC Research Program, present the formal financial report, and provide information on activities and events of the SRC industry/government/university community for the previous calendar year. -

Alphabetical Listing of Companies

Alphabetical Listing of Companies 8x8, Inc. ..................................................................................................................................1-1 ABB Hafo AB (see Mitel Semiconductor) ACC Microelectronics Corporation............................................................................................1-3 Actel Corporation.....................................................................................................................1-4 Advanced Semiconductor Manufacturing Corporation (ASMC, see Philips) Alcatel Mietec..........................................................................................................................3-1 Allegro MicroSystems, Inc........................................................................................................1-7 Alliance Semiconductor Corporation ........................................................................................1-10 Alpha-TI Semiconductor Company (see Texas Instruments) Altera Corporation....................................................................................................................1-14 AMCC (Applied Micro Circuits Corporation)...............................................................................1-18 AMD (Advanced Micro Devices, Inc.) .......................................................................................1-21 AMI (American Microsystems Inc.)...........................................................................................1-28 Anadigics, Inc..........................................................................................................................1-31 -

CLASSIC COMPONENTS CORP 23605 Telo Ave

Founded in 1985, Classic Components is a full service independent stocking distributor specializing in Integrated Components, Passives, Interconnect Products and Peripherals. We pride ourselves on our exceptional customer service, abundant on-the-shelf inventory, and our ability to customize any partnership to meet the needs of our customers. ACTIVE COMPONENTS Integrated Circuits, Transistors, Diodes Actel GEC Plessey Micron SGS Thompson-ST Micro Adaptec General Instrument Mitel Semi – Zarlink Sharp Advanced Micro Devices Goldstar Mitsubishi Siemens / Infineon Agere/ATT/Lucent Harris Semi-Intersil Monolithic Mem. (obs) Signetics (obs) Agilent/HP HP-Agilent Mosel / Vitelic Silicon General Allegro Microsoft Hitachi Motorola – Freescale Silicon Systems / TDK Alliance Semi Honeywell National Semi Sipex Altera Hyundai-Hynix NCR (obs) Smos – Seiko AMI IBM NEC Electronics Sony Analog Devices IDT NMB Tech-Computer Prod. Standard Micro AT&T (obs) Lucent Inmos (obs) NXP Startex – Exar Atmel International Rectifier Oki Supertex Avantek Intersil-Harris On Semi Symbios Logic-LSI Logic Benchmarq-TI IPS Osram Teccor – Littlefuse Broadcom Isocom Panasonic Telcom Semi-Micro Comp Brocade ISSI Paradigm Tech- Ixys Teledyne (obs) Brooktree-Conexant ITT Cannon Pericom Temic-Siliconix/Vishay Burr Brown-TI Ixys Philips Texas Instruments C-Cube-LSI Lattice Semi Plessey (obs) – Mitel Toshiba Cal Micro Devices Legerity PMC – Sierra TRW Catalyst Semi LG PMI (obs) – Analog Dev. UMC Cherry Semi Level One-Intel Quality Technology – IDT Unitrode-TI Chips & Tech. (obs) Linear Technology Quicklogic VLSI-Philips Cirrus Logic Lite-On Raytheon Semi Vishay-Temic-Siliconix CP Clare-lxys Logic Devices RCA – Intersil Vitelic / Mosel Crystal Semi LSI Renesas Vitesse Dallas Semi-Maxim Macronix-Ixys Rockwell / Brooktree – Waferscale Elantec-Intersil Marvell Conexant Weltek (Rockwell) Elpida Maxim Rohm Western Digital (obs) Epson Micrel Samsung Winbond Exar Micro Linear Sanyo Xicor-Intersil Excel Microsoft Micro Power Seeq Tech. -

4 Ic Device and Packaging Technology Trends

4 IC DEVICE AND PACKAGING TECHNOLOGY TRENDS IC DEVICE TECHNOLOGY OVERVIEW There are a variety of major manufacturing process technologies (Figure 4-1) used in design and fabrication of silicon-based integrated circuits (ICs). These include metal-oxide-semiconductor (MOS), bipolar, and combined bipolar and complementary-MOS (BiCMOS). While silicon-based processing dominates in semiconductor manufacturing, gallium arsenide (GaAs), a compound- semiconductor material, is a niche alternative to silicon for some applications. Marketshare IC (Percent of Total Dollars) Manufacturing 1997 Status Process 1997 2002 1970 1980 1990 Technologies (EST) (FCST) MOS (total): 35 52 75 ~69 ~87 PMOS Obsolete 31 5 — — — NMOS/HMOS Virtually obsolete 2 37 10 <1 <1 CMOS Mainstream MOS technology, with continued 2 10 65 69 86 growth. Bipolar (total): 65 48 24 ~12 ~10 ECL Fastest silicon-based process, but losing to 3 3 3 <1 <1 GaAs. Virtually obsolete. TTL Virtually obsolete. 29 8 2 <1 — S/LS TTL Virtually obsolete, having lost to MOS ASICs 7 13 4 1 <1 designs. LINEAR Mainstream analog technology, but 26 24 15 11 8 competition from CMOS, and GaAs. BiCMOS: Offers both MOS and bipolar advantages, but — — 1 18 5 slipping from high cost/complexity. GaAs: Still niche technology, but future potential. — — <1 1 1 Source: ICE 11218W Figure 4-1. Market Share Overview of IC Manufacturing Process Technologies INTEGRATED CIRCUIT ENGINEERING CORPORATION 4-1 IC Device and Packaging Technology Trends Within MOS and bipolar manufacturing process technologies, device design variations have emerged and declined as IC applications and complexities have changed. Historically, back in 1970 bipolar was the major technology of choice; it was used for almost 66 percent of the total IC market. -

3M Interconnect Solutions 3M Touch Systems Aaeon Aavid Thermalloy

3M Interconnect Solutions 3M Touch Systems A Aaeon Aavid Thermalloy AB Connectors Abbatron Abracon Actel Adaptec by PMC ADI Engineering ADLINK Technology Inc. Advanced Analogic Technologies Advanced Hardware Architectures Advanced Linear Devices Advanced Micro Devices (AMD) Advanced Power Technology Advanced Semiconductor Advantech Allgemeine Elektrizitäts-Gesellschaft (AEG) AEP (Applied Engineering Products) Aeroflex Inc Aerovox Agastat/Tyco Agilent Technologies AIC Aimtec Airpax AIS AKM Semiconductor Alco Alcor Micro Corp Alcoswitch Allegro MicroSystems Allen Bradley Alliance Semiconductor Corp Alpha Wire Alps Electric Altech 1 Altera AMCC AMD American Power Conversion (APC) American Zettler AMI AMIC Technology Corp AMP/TYCO Amphenol Amphenol RF/Connex Anachip Corp Anadigics Analog Devices Analog Integrations Corp Antenova Aopen APC Apex Microtechnology Corp API Delevan Applied Micro (AMCC) Aras Power Technologies Arcotronics Aromat Artesyn Technologies Astec AT+T Atmel ATP Electronics AU Optronics Augat AUK Co, Ltd Austin Semiconductor Austria Mikro Systeme Int Avago Technologies Avasem AVX AVX / ELCO Axiomtek AZ Displays B BC Components BCM Advanced Research BeagleBoard Beckman Bel Fuse Belden Belling Lee 2 Benchmarq Bendix Berg Beyond Innovation Technology Beyschlag BHC Aerovox BI Technologies BLP Components Blugiga Technologies Bourns Broadcom Brocade Brooktree Buchanan/TYCO Bulgin Burgess Burndy Burr-Brown Corp Bussmann C C&D C&K Components Cal Chip California Micro Devices Calogic, LLC Cambion CAO Group Inc Carling Technologies -

A Decade of Semiconductor Companies—1988 Edition to Keep Clients Informed of These New and Emerging Companies

1988 y DataQuest Do Not Remove A. Decade of Semiconductor Companies 1988 Edition Components Division TABLE OF CONTENTS Page I. Introduction 1 II. Venture Capital 11 III. Strategic Alliances 15 IV. Product Analysis 56 Emerging Technology Companies 56 Analog ICs 56 ASICs 58 Digital Signal Processing 59 Discrete Semiconductors 60 Gallium Arsenide 60 Memory 62 Microcomponents 64 Optoelectronics 65 Telecommunication ICs 65 Other Products 66 Bubble Memory 67 V. Company Profiles (139) 69 A&D Co., Ltd. 69 Acrian Inc. 71 ACTEL Corporation 74 Acumos, Inc. 77 Adaptec, Inc. 79 Advanced Linear Devices, Inc. 84 Advanced Microelectronic Products, Inc. 87 Advanced Power Technology, Inc. 89 Alliance Semiconductor 92 Altera Corporation 94 ANADIGICS, Inc. 100 Applied Micro Circuits Corporation 103 Asahi Kasei Microsystems Co., Ltd. 108 Aspen Semiconductor Corporation 111 ATMEL Corporation 113 Austek Microsystems Pty. Ltd. 116 Barvon Research, Inc. 119 Bipolar Integrated Technology 122 Brooktree Corporation 126 California Devices, Ihc. 131 California Micro Devices Corporation 135 Calmos Systems, Inc. 140 © 1988 Dataquest Incorporated June TABLE OF CONTENTS (Continued) Pagg Company Profiles (Continued) Calogic Corporation 144 Catalyst Semiconductor, Inc. 146 Celeritek, Inc. ISO Chartered Semiconductor Pte Ltd. 153 Chips and Technologies, Inc. 155 Cirrus Logic, Inc. 162 Conductus Inc. 166 Cree Research Inc. 167 Crystal Semiconductor Corporation 169 Custom Arrays Corporation 174 Custom Silicon Inc. 177 Cypress Semiconductor Corporation 181 Dallas Semiconductor Corporation 188 Dolphin Integration SA 194 Elantec, Inc. 196 Electronic Technology Corporation 200 Epitaxx Inc. 202 European Silicon Structures 205 Exel Microelectronics Inc. 209 G-2 Incorporated 212 GAIN Electronics 215 Gazelle Microcircuits, Inc. 218 Genesis Microchip Inc.