The Magazine for Chip and Silicon Systems Designers

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Field Programmable Gate Arrays with Hardwired Networks on Chip

Field Programmable Gate Arrays with Hardwired Networks on Chip PROEFSCHRIFT ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus prof. ir. K.C.A.M. Luyben, voorzitter van het College voor Promoties, in het openbaar te verdedigen op dinsdag 6 november 2012 om 15:00 uur door MUHAMMAD AQEEL WAHLAH Master of Science in Information Technology Pakistan Institute of Engineering and Applied Sciences (PIEAS) geboren te Lahore, Pakistan. Dit proefschrift is goedgekeurd door de promotor: Prof. dr. K.G.W. Goossens Copromotor: Dr. ir. J.S.S.M. Wong Samenstelling promotiecommissie: Rector Magnificus voorzitter Prof. dr. K.G.W. Goossens Technische Universiteit Eindhoven, promotor Dr. ir. J.S.S.M. Wong Technische Universiteit Delft, copromotor Prof. dr. S. Pillement Technical University of Nantes, France Prof. dr.-Ing. M. Hubner Ruhr-Universitat-Bochum, Germany Prof. dr. D. Stroobandt University of Gent, Belgium Prof. dr. K.L.M. Bertels Technische Universiteit Delft Prof. dr.ir. A.J. van der Veen Technische Universiteit Delft, reservelid ISBN: 978-94-6186-066-8 Keywords: Field Programmable Gate Arrays, Hardwired, Networks on Chip Copyright ⃝c 2012 Muhammad Aqeel Wahlah All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without permission of the author. Printed in The Netherlands Acknowledgments oday when I look back, I find it a very interesting journey filled with different emotions, i.e., joy and frustration, hope and despair, and T laughter and sadness. -

Life of Occam-Pi

View metadata, citation and similar papers at core.ac.uk brought to you by CORE provided by Kent Academic Repository Communicating Process Architectures 2013 293 P.H. Welch et al. (Eds.) Open Channel Publishing Ltd., 2013 © 2013 The authors and Open Channel Publishing Ltd. All rights reserved. Life of occam-Pi Peter H. WELCH School of Computing, University of Kent, UK [email protected] Abstract. This paper considers some questions prompted by a brief review of the history of computing. Why is programming so hard? Why is concurrency considered an “advanced” subject? What’s the matter with Objects? Where did all the Maths go? In searching for answers, the paper looks at some concerns over fundamental ideas within object orientation (as represented by modern programming languages), before focussing on the concurrency model of communicating processes and its particular expression in the occam family of languages. In that focus, it looks at the history of occam, its underlying philosophy (Ockham’s Razor), its semantic foundation on Hoare’s CSP, its principles of process oriented design and its development over almost three decades into occam-π (which blends in the concurrency dynamics of Milner’s π-calculus). Also presented will be an urgent need for rationalisation – occam-π is an experiment that has demonstrated significant results, but now needs time to be spent on careful review and implementing the conclusions of that review. Finally, the future is considered. In particular, is there a future? Keywords. process, object, local reasoning, global reasoning, occam-pi, concurrency, compositionality, verification, multicore, efficiency, scalability, safety, simplicity Introduction Let’s try a few questions to which the answer might be: “occam, obviously”. -

North American Company Profiles 8X8

North American Company Profiles 8x8 8X8 8x8, Inc. 2445 Mission College Boulevard Santa Clara, California 95054 Telephone: (408) 727-1885 Fax: (408) 980-0432 Web Site: www.8x8.com Email: [email protected] Fabless IC Supplier Regional Headquarters/Representative Locations Europe: 8x8, Inc. • Bucks, England U.K. Telephone: (44) (1628) 402800 • Fax: (44) (1628) 402829 Financial History ($M), Fiscal Year Ends March 31 1992 1993 1994 1995 1996 1997 1998 Sales 36 31 34 20 29 19 50 Net Income 5 (1) (0.3) (6) (3) (14) 4 R&D Expenditures 7 7 7 8 8 11 12 Capital Expenditures — — — — 1 1 1 Employees 114 100 105 110 81 100 100 Ownership: Publicly held. NASDAQ: EGHT. Company Overview and Strategy 8x8, Inc. is a worldwide leader in the development, manufacture and deployment of an advanced Visual Information Architecture (VIA) encompassing A/V compression/decompression silicon, software, subsystems, and consumer appliances for video telephony, videoconferencing, and video multimedia applications. 8x8, Inc. was founded in 1987. The “8x8” refers to the company’s core technology, which is based upon Discrete Cosine Transform (DCT) image compression and decompression. In DCT, 8-pixel by 8-pixel blocks of image data form the fundamental processing unit. 2-1 8x8 North American Company Profiles Management Paul Voois Chairman and Chief Executive Officer Keith Barraclough President and Chief Operating Officer Bryan Martin Vice President, Engineering and Chief Technical Officer Sandra Abbott Vice President, Finance and Chief Financial Officer Chris McNiffe Vice President, Marketing and Sales Chris Peters Vice President, Sales Michael Noonen Vice President, Business Development Samuel Wang Vice President, Process Technology David Harper Vice President, European Operations Brett Byers Vice President, General Counsel and Investor Relations Products and Processes 8x8 has developed a Video Information Architecture (VIA) incorporating programmable integrated circuits (ICs) and compression/decompression algorithms (codecs) for audio/video communications. -

Rmox: a Raw-Metal Occam Experiment

Communicating Process Architectures – 2003 269 Jan F. Broenink and Gerald H. Hilderink (Eds.) IOS Press, 2003 RMoX: A Raw-Metal occam Experiment Fred BARNES†, Christian JACOBSEN† and Brian VINTER‡ † Computing Laboratory, University of Kent, Canterbury, Kent, CT2 7NF, England. {frmb2,clj3}@kent.ac.uk ‡ Department of Mathematics and Computer Science, University of Southern Denmark, Odense, Denmark. [email protected] Abstract. Operating-systems are the core software component of many modern com- puter systems, ranging from small specialised embedded systems through to large distributed operating-systems. This paper presents RMoX: a highly concurrent CSP- based operating-system written in occam. The motivation for this stems from the overwhelming need for reliable, secure and scalable operating-systems. The major- ity of operating-systems are written in C, a language that easily offers the level of flexibility required (for example, interfacing with assembly routines). C compilers, however, provide little or no mechanism to guard against race-hazard and aliasing er- rors, that can lead to catastrophic run-time failure (as well as to more subtle errors, such as security loop-holes). The RMoX operating-system presents a novel approach to operating-system design (although this is not the first CSP-based operating-system). Concurrency is utilised at all levels, resulting in a system design that is well defined, easily understood and scalable. The implementation, using the KRoC extended oc- cam, provides guarantees of freedom from race-hazard and aliasing errors, and makes extensive use of the recently added support for dynamic process creation and channel mobility. Whilst targeted at mainstream computing, the ideas and methods presented are equally applicable for small-scale embedded systems — where advantage can be made of the lightweight nature of RMoX (providing fast interrupt responses, for ex- ample). -

NASDAQ Stock Market

Nasdaq Stock Market Friday, December 28, 2018 Name Symbol Close 1st Constitution Bancorp FCCY 19.75 1st Source SRCE 40.25 2U TWOU 48.31 21st Century Fox Cl A FOXA 47.97 21st Century Fox Cl B FOX 47.62 21Vianet Group ADR VNET 8.63 51job ADR JOBS 61.7 111 ADR YI 6.05 360 Finance ADR QFIN 15.74 1347 Property Insurance Holdings PIH 4.05 1-800-FLOWERS.COM Cl A FLWS 11.92 AAON AAON 34.85 Abiomed ABMD 318.17 Acacia Communications ACIA 37.69 Acacia Research - Acacia ACTG 3 Technologies Acadia Healthcare ACHC 25.56 ACADIA Pharmaceuticals ACAD 15.65 Acceleron Pharma XLRN 44.13 Access National ANCX 21.31 Accuray ARAY 3.45 AcelRx Pharmaceuticals ACRX 2.34 Aceto ACET 0.82 Achaogen AKAO 1.31 Achillion Pharmaceuticals ACHN 1.48 AC Immune ACIU 9.78 ACI Worldwide ACIW 27.25 Aclaris Therapeutics ACRS 7.31 ACM Research Cl A ACMR 10.47 Acorda Therapeutics ACOR 14.98 Activision Blizzard ATVI 46.8 Adamas Pharmaceuticals ADMS 8.45 Adaptimmune Therapeutics ADR ADAP 5.15 Addus HomeCare ADUS 67.27 ADDvantage Technologies Group AEY 1.43 Adobe ADBE 223.13 Adtran ADTN 10.82 Aduro Biotech ADRO 2.65 Advanced Emissions Solutions ADES 10.07 Advanced Energy Industries AEIS 42.71 Advanced Micro Devices AMD 17.82 Advaxis ADXS 0.19 Adverum Biotechnologies ADVM 3.2 Aegion AEGN 16.24 Aeglea BioTherapeutics AGLE 7.67 Aemetis AMTX 0.57 Aerie Pharmaceuticals AERI 35.52 AeroVironment AVAV 67.57 Aevi Genomic Medicine GNMX 0.67 Affimed AFMD 3.11 Agile Therapeutics AGRX 0.61 Agilysys AGYS 14.59 Agios Pharmaceuticals AGIO 45.3 AGNC Investment AGNC 17.73 AgroFresh Solutions AGFS 3.85 -

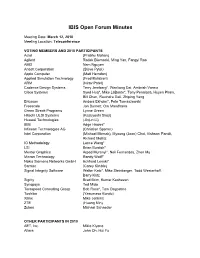

IBIS Open Forum Minutes

IBIS Open Forum Minutes Meeting Date: March 12, 2010 Meeting Location: Teleconference VOTING MEMBERS AND 2010 PARTICIPANTS Actel (Prabhu Mohan) Agilent Radek Biernacki, Ming Yan, Fangyi Rao AMD Nam Nguyen Ansoft Corporation (Steve Pytel) Apple Computer (Matt Herndon) Applied Simulation Technology (Fred Balistreri) ARM (Nirav Patel) Cadence Design Systems Terry Jernberg*, Wenliang Dai, Ambrish Varma Cisco Systems Syed Huq*, Mike LaBonte*, Tony Penaloza, Huyen Pham, Bill Chen, Ravindra Gali, Zhiping Yang Ericsson Anders Ekholm*, Pete Tomaszewski Freescale Jon Burnett, Om Mandhana Green Streak Programs Lynne Green Hitachi ULSI Systems (Kazuyoshi Shoji) Huawei Technologies (Jinjun Li) IBM Adge Hawes* Infineon Technologies AG (Christian Sporrer) Intel Corporation (Michael Mirmak), Myoung (Joon) Choi, Vishram Pandit, Richard Mellitz IO Methodology Lance Wang* LSI Brian Burdick* Mentor Graphics Arpad Muranyi*, Neil Fernandes, Zhen Mu Micron Technology Randy Wolff* Nokia Siemens Networks GmbH Eckhard Lenski* Samtec (Corey Kimble) Signal Integrity Software Walter Katz*, Mike Steinberger, Todd Westerhoff, Barry Katz Sigrity Brad Brim, Kumar Keshavan Synopsys Ted Mido Teraspeed Consulting Group Bob Ross*, Tom Dagostino Toshiba (Yasumasa Kondo) Xilinx Mike Jenkins ZTE (Huang Min) Zuken Michael Schaeder OTHER PARTICIPANTS IN 2010 AET, Inc. Mikio Kiyono Altera John Oh, Hui Fu Avago Razi Kaw Broadcom Mohammad Ali Curtiss-Wright John Phillips ECL, Inc. Tom Iddings eSilicon Hanza Rahmai Exar Corp. Helen Nguyen Mindspeed Bobby Altaf National Semiconductor Hsinho Wu* NetLogic Microsystems Eric Hsu, Edward Wu Renesas Technology Takuji Komeda Simberian Yuriy Shlepnev Span Systems Corporation Vidya (Viddy) Amirapu Summit Computer Systems Bob Davis Tabula David Banas* TechAmerica (Chris Denham) Texas Instruments Bonnie Baker Independent AbdulRahman (Abbey) Rafiq, Robert Badal In the list above, attendees at the meeting are indicated by *. -

Chapters 1-10 As a Single File (Pdf)

Boldrin & Levine: Against Intellectual Monopoly, Chapter 1 Chapter 1: Introduction In late 1764, while repairing a small Newcomen steam engine, the idea of allowing steam to expand and condense in separate containers sprang into the mind of James Watt. He spent the next few months in unceasing labor building a model of the new engine. In 1768, after a series of improvements and substantial borrowing, he applied for a patent on the idea. August found Watt in London about the patent and he spent another six months working hard to obtain it. The patent was finally awarded in January of the following year. Nothing much happened by way of production until 1775. Then, with a major effort supported by his business partner, the rich industrialist Matthew Boulton, Watt secured an Act of Parliament extending his patent until the year 1800. The great statesman Edmund Burke spoke eloquently in Parliament in the name of economic freedom and against the creation of unnecessary monopoly – but to no avail. The connections of Watt’s partner Boulton were too solid to be defeated by simple principle. Once Watt’s patents were secured and production started, a substantial portion of his energy was devoted to fending off rival inventors. In 1782, Watt secured an additional patent, made “necessary in consequence of ... having been so unfairly anticipated, by [Matthew] Wasborough in the crank motion.” More dramatically, in the 1790s, when the superior Hornblower engine was put into production, Boulton and Watt went after him with the full force of the legal system. During the period of Watt’s patents the U.K. -

Advance Program 2015 Ieee International Solid-State

2015_MiniAP_Cover_AP 1/19/15 9:33 AM Page 1 ADVANCE PROGRAM & MORE S / B CMOS LOW-VOLTAGE CIRCUIT DESIGN CMOS LOW-VOLTAGE THURSDAY ALL-DAY THURSDAY : ADVANCES IN WIRELESS POWER; LOW POWER FOR ADVANCES : E; RF TRANSMITTER ADVANCES; IO @ 25G E; RF TRANSMITTER ADVANCES; O 2015 IEEE SHORT-COURSE I INTERNATIONAL 4 FORUMS SOLID-STATE CIRCUITS CONFERENCE FEBRUARY 22, 23, 24, 25, 26 CONFERENCE THEME: IEEE SOLID-STATE CIRCUITS SOCIETY IEEE SOLID-STATE SILICON SYSTEMS ALL-DAY SUNDAY SMALL CHIPS FOR BIG DATA ANALOG; FREQUENCY SYNTHESIZERS; 3D IMAGING ICs GRADUATE STUDENT RESEARCH IN PROGRESS, ICsGRADUATE TO NEURONS TALKING SAN FRANCISCO TO WEARABLE TRENDS: BIG DATA ADCs; MEMORY HIGH-SPEED INTERLEAVED MARRIOTT MARQUIS HOTEL : RF RECEIVERS; DRAM INTERFACES; ULTRA-LOW-POWER WIRELESS; NEAR-THRESHOLD DESIGN; ULTRA-LOW-POWER RF RECEIVERS; DRAM INTERFACES; : 2 FORUMS NEW THIS YEAR: HIGH-SPEED CURRENT-STEERING DACs; CLOCK & DATA RECOVERY; MANY-CORE PROCESSORS; NANO-POWER MANY-CORE RECOVERY; DACs; CLOCK & DATA HIGH-SPEED CURRENT-STEERING 2 EVENING EVENTS ON ISSCCX 10 TUTORIALS ISSCC PREVIEWS: CIRCUIT & SYSTEM INSIGHTS SEE PAGE: 61 5-DAY PROGRAM 2015_MiniAP_Cover_AP 1/19/15 9:33 AM Page 2 ISSCC VISION STATEMENT The International Solid-State Circuits Conference is the foremost global forum for presentation of advances in solid-state circuits and systems-on-a-chip. The Conference offers a unique opportunity for engineers working at thecutting edge of IC design and application to maintain technical currency, and to network with leading experts. CONFERENCE TECHNICAL HIGHLIGHTS On Sunday, February 22nd, the day before the official opening of the Conference, ISSCC 2015 offers: • A choice of up to 4 of a total of 10 Tutorials • A choice of 1 of 2 all-day Advanced-Circuit-Design Forums The 90-minute tutorials offer background information and a review of the basics in specific circuit-design topics. -

Logos De Fabricantes De Semiconductores Semiconductor Manufacturers Logos

2013 Logos de fabricantes de semiconductores Semiconductor manufacturers logos EugenioNieto Vilardell Fidestec 15/03/2013 Logos de fabricantes de semiconductores 2013 2 8x8 Acer Acer Laboratories Acrian Actel ADDtek ADMtek Advanced Analogic Technology Advanced Communication Devices(ACD) Advanced Hardware Architectures Advanced Linear Devices Advanced Micro Devices(AMD) Advanced Micro Systems Advanced Monolithic Systems Advanced Power Technology Aeroflex Agere (formerly Lucent) Agilent Technologies Aimtron AITech International aJile Systems AKM Semiconductor Alchemy Semiconductor Alesis Semiconductor Allayer Communications(Now Broadcom) Allegro Microsystems Alliance Semiconductor Alogics Alpha & Omega Semiconductor Alpha Industries Alpha Microelectronics Alpha Semiconductor(Now Sipex) Altera Altima Communications AME Inc American Microsystems American Power Devices Logos de fabricantes de semiconductores 2013 3 AMIC Technology Anachip ANADIGICS Anadigm Analog Devices Analog Express Corp. Analog Integrations Corporation Analog Systems Anchor Chips Andigilog Anpec Ansaldo (Now Poseico) Apex Microtechnology API NetWorks Arizona Microtek ARK Logic Array Microsystems Astec Semiconductor AT&T ATAN Technology ATecoM ATI Technologies Atmel Auctor AudioCodes AUK Semiconductor Corp. Aura Vision Aureal Aurora Systems Austin Semiconductor Austria Mikro Systeme International Avance Logic Avantek Averlogic Avic Electronics Corp. AXElite Technology Co., Ltd BCD Semiconductor Manufacturing Limited Bel Fuse Logos de fabricantes de semiconductores 2013 -

Efpgas : Architectural Explorations, System Integration & a Visionary Industrial Survey of Programmable Technologies Syed Zahid Ahmed

eFPGAs : Architectural Explorations, System Integration & a Visionary Industrial Survey of Programmable Technologies Syed Zahid Ahmed To cite this version: Syed Zahid Ahmed. eFPGAs : Architectural Explorations, System Integration & a Visionary Indus- trial Survey of Programmable Technologies. Micro and nanotechnologies/Microelectronics. Université Montpellier II - Sciences et Techniques du Languedoc, 2011. English. tel-00624418 HAL Id: tel-00624418 https://tel.archives-ouvertes.fr/tel-00624418 Submitted on 16 Sep 2011 HAL is a multi-disciplinary open access L’archive ouverte pluridisciplinaire HAL, est archive for the deposit and dissemination of sci- destinée au dépôt et à la diffusion de documents entific research documents, whether they are pub- scientifiques de niveau recherche, publiés ou non, lished or not. The documents may come from émanant des établissements d’enseignement et de teaching and research institutions in France or recherche français ou étrangers, des laboratoires abroad, or from public or private research centers. publics ou privés. Université Montpellier 2 (UM2) École Doctorale I2S LIRMM (Laboratoire d'Informatique, de Robotique et de Microélectronique de Montpellier) Domain: Microelectronics PhD thesis report for partial fulfillment of requirements of Doctorate degree of UM2 Thesis conducted in French Industrial PhD (CIFRE) framework between: Menta & LIRMM lab (Dec.2007 – Feb. 2011) in Montpellier, FRANCE “eFPGAs: Architectural Explorations, System Integration & a Visionary Industrial Survey of Programmable Technologies” eFPGAs: Explorations architecturales, integration système, et une enquête visionnaire industriel des technologies programmable by Syed Zahid AHMED Presented and defended publically on: 22 June 2011 Jury: Mr. Guy GOGNIAT Prof. at STICC/UBS (Lorient, FRANCE) President Mr. Habib MEHREZ Prof. at LIP6/UPMC (Paris, FRANCE) Reviewer Mr. -

Architecture Exploration of FPGA Based Accelerators for Bioinformatics Applications Springer Series in Advanced Microelectronics

Springer Series in Advanced Microelectronics 55 B. Sharat Chandra Varma Kolin Paul M. Balakrishnan Architecture Exploration of FPGA Based Accelerators for BioInformatics Applications Springer Series in Advanced Microelectronics Volume 55 Series editors Kukjin Chun, Seoul, Korea, Republic of (South Korea) Kiyoo Itoh, Tokyo, Japan Thomas H. Lee, Stanford, CA, USA Rino Micheloni, Vimercate (MB), Italy Takayasu Sakurai, Tokyo, Japan Willy M.C. Sansen, Leuven, Belgium Doris Schmitt-Landsiedel, München, Germany The Springer Series in Advanced Microelectronics provides systematic information on all the topics relevant for the design, processing, and manufacturing of microelectronic devices. The books, each prepared by leading researchers or engineers in their fields, cover the basic and advanced aspects of topics such as wafer processing, materials, device design, device technologies, circuit design, VLSI implementation, and subsystem technology. The series forms a bridge between physics and engineering and the volumes will appeal to practicing engineers as well as research scientists. More information about this series at http://www.springer.com/series/4076 B. Sharat Chandra Varma Kolin Paul • M. Balakrishnan Architecture Exploration of FPGA Based Accelerators for BioInformatics Applications 123 B. Sharat Chandra Varma M. Balakrishnan Department of Electrical and Electronic Department of Computer Science Engineering and Engineering The University of Hong Kong Indian Institute of Technology Delhi Hong Kong New Delhi, Delhi Hong Kong India Kolin Paul Department of Computer Science and Engineering Indian Institute of Technology Delhi New Delhi, Delhi India ISSN 1437-0387 ISSN 2197-6643 (electronic) Springer Series in Advanced Microelectronics ISBN 978-981-10-0589-3 ISBN 978-981-10-0591-6 (eBook) DOI 10.1007/978-981-10-0591-6 Library of Congress Control Number: 2016931344 © Springer Science+Business Media Singapore 2016 This work is subject to copyright. -

Modelling with Cellular Automata: Problem Solving Environments and Multidimensional Applications

UvA-DARE (Digital Academic Repository) Modelling with cellular automata: problem solving environments and multidimensional applications Naumov, L.A. Publication date 2011 Document Version Final published version Link to publication Citation for published version (APA): Naumov, L. A. (2011). Modelling with cellular automata: problem solving environments and multidimensional applications. General rights It is not permitted to download or to forward/distribute the text or part of it without the consent of the author(s) and/or copyright holder(s), other than for strictly personal, individual use, unless the work is under an open content license (like Creative Commons). Disclaimer/Complaints regulations If you believe that digital publication of certain material infringes any of your rights or (privacy) interests, please let the Library know, stating your reasons. In case of a legitimate complaint, the Library will make the material inaccessible and/or remove it from the website. Please Ask the Library: https://uba.uva.nl/en/contact, or a letter to: Library of the University of Amsterdam, Secretariat, Singel 425, 1012 WP Amsterdam, The Netherlands. You will be contacted as soon as possible. UvA-DARE is a service provided by the library of the University of Amsterdam (https://dare.uva.nl) Download date:05 Oct 2021 Modelling with Cellular Automata: Problem Solving Environments and Multidimensional Applications ACADEMISCH PROEFSCHRIFT ter verkrijging van de graad van doctor aan de Universiteit van Amsterdam op gezag van de Rector Magnificus prof. dr. D.C. van den Boom ten overstaan van een door het college voor promoties ingestelde commissie, in het openbaar te verdedigen in de Agnietenkapel op dinsdag 14 juni 2011, te 10:00 uur door Lev Alexandrovich Naumov geboren te Sint-Petersburg, Rusland Promotiecommissie Promotor: Prof.