Very High Frequency Integrated POL for Cpus

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Chapter 6 BUILDING a HOMEBREW

1. Chapter 6, Harris CRYSTAL SETS TO SIDEBAND © Frank W. Harris 2002 Chapter 6 BUILDING A HOMEBREW QRP Among the guys I work, QRPs seem to be the most common homebrew project, second only to building antennas. Therefore this chapter describes a simple QRP design I have settled on. I use my QRPs as stand-alone transmitters or I use them to drive a final amplifier to produce higher power, 25 to 100 watts. It’s true that before you build a transmitter you’ll need a receiver. Unfortunately, a good selective, all-band ham receiver is complicated to build and most guys don’t have the time and enthusiasm to do it. (See chapter 13.) The next chapter describes building a simple, 5 transistor 40 meter receiver which I have used with the QRP below to talk to other hams. This simple receiver will work best during off hours when 40 meters isn’t crowded. It can also be used to receive Morse code for code practice. A 40 meter QRP module. The QRP transmitter above is designed exclusively for 40 meters, (7.000 to 7.300 MHz.) The twelve-volt power supply comes in through the pig-tail wire up on the right. The telegraph key plugs into the blue-marked phono plug socket on the right of the aluminum heat sink. The antenna output is the red-colored socket on the left end of the heat sink. The transmitting frequency of the QRP module is controlled by a quartz crystal. That’s the silver rectangular can plugged into the box on the right front. -

Three-Dimensional Integrated Circuit Design: EDA, Design And

Integrated Circuits and Systems Series Editor Anantha Chandrakasan, Massachusetts Institute of Technology Cambridge, Massachusetts For other titles published in this series, go to http://www.springer.com/series/7236 Yuan Xie · Jason Cong · Sachin Sapatnekar Editors Three-Dimensional Integrated Circuit Design EDA, Design and Microarchitectures 123 Editors Yuan Xie Jason Cong Department of Computer Science and Department of Computer Science Engineering University of California, Los Angeles Pennsylvania State University [email protected] [email protected] Sachin Sapatnekar Department of Electrical and Computer Engineering University of Minnesota [email protected] ISBN 978-1-4419-0783-7 e-ISBN 978-1-4419-0784-4 DOI 10.1007/978-1-4419-0784-4 Springer New York Dordrecht Heidelberg London Library of Congress Control Number: 2009939282 © Springer Science+Business Media, LLC 2010 All rights reserved. This work may not be translated or copied in whole or in part without the written permission of the publisher (Springer Science+Business Media, LLC, 233 Spring Street, New York, NY 10013, USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in connection with any form of information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed is forbidden. The use in this publication of trade names, trademarks, service marks, and similar terms, even if they are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights. Printed on acid-free paper Springer is part of Springer Science+Business Media (www.springer.com) Foreword We live in a time of great change. -

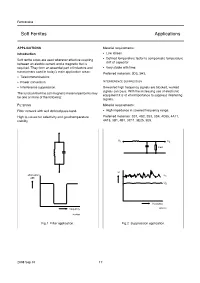

Soft Ferrites Applications

Ferroxcube Soft Ferrites Applications APPLICATIONS Material requirements: Introduction • Low losses • Defined temperature factor to compensate temperature Soft ferrite cores are used wherever effective coupling drift of capacitor between an electric current and a magnetic flux is required. They form an essential part of inductors and • Very stable with time. transformers used in today’s main application areas: Preferred materials: 3D3, 3H3. • Telecommunications • Power conversion INTERFERENCE SUPPRESSION • Interference suppression. Unwanted high frequency signals are blocked, wanted signals can pass. With the increasing use of electronic The function that the soft magnetic material performs may equipment it is of vital importance to suppress interfering be one or more of the following: signals. FILTERING Material requirements: Filter network with well defined pass-band. • High impedance in covered frequency range. High Q-values for selectivity and good temperature Preferred materials: 3S1, 4S2, 3S3, 3S4, 4C65, 4A11, stability. 4A15, 3B1, 4B1, 3C11, 3E25, 3E5. andbook, halfpage handbook, halfpage U1 U2 load U attenuation U1 (dB) U2 frequency frequency MBW404 MBW403 Fig.1 Filter application. Fig.2 Suppression application. 2008 Sep 01 17 Ferroxcube Soft Ferrites Applications DELAYING PULSES STORAGE OF ENERGY The inductor will block current until saturated. Leading An inductor stores energy and delivers it to the load during edge is delayed depending on design of magnetic circuit. the off-time of a Switched Mode Power Supply (SMPS). Material requirements: Material requirements: • High permeability (µi). • High saturation level (Bs). Preferred materials: 3E25, 3E5, 3E6, 3E7, 3E8, 3E9. Preferred materials: 3C30, 3C34, 3C90, 3C92, 3C96 2P-iron powder. U U handbook, halfpage 1 handbook, halfpage1 U2 U2 SMPS load delay U U U1 U2 U1 U2 time time MBW405 MBW406 Fig.3 Pulse delay application. -

Negative Capacitance in a Ferroelectric Capacitor

Negative Capacitance in a Ferroelectric Capacitor Asif Islam Khan1, Korok Chatterjee1, Brian Wang1, Steven Drapcho2, Long You1, Claudy Serrao1, Saidur Rahman Bakaul1, Ramamoorthy Ramesh2,3,4, Sayeef Salahuddin1,4* 1 Dept. of Electrical Engineering and Computer Sciences, University of California, Berkeley 2 Dept. of Physics, University of California, Berkeley 3 Dept. of Material Science and Engineering, University of California, Berkeley 4 Material Science Division, Lawrence Berkeley National Laboratory, Berkeley, *To whom correspondence should be addressed; E-mail: [email protected] The Boltzmann distribution of electrons poses a fundamental barrier to lowering energy dissipation in conventional electronics, often termed as Boltzmann Tyranny1-5. Negative capacitance in ferroelectric materials, which stems from the stored energy of phase transition, could provide a solution, but a direct measurement of negative capacitance has so far been elusive1-3. Here we report the observation of negative capacitance in a thin, epitaxial ferroelectric film. When a voltage pulse is applied, the voltage across the ferroelectric capacitor is found to be decreasing with time–in exactly the opposite direction to which voltage for a regular capacitor should change. Analysis of this ‘inductance’-like behavior from a capacitor presents an unprecedented insight into the intrinsic energy profile of the ferroelectric material and could pave the way for completely new applications. 1 Owing to the energy barrier that forms during phase transition and separates the two degenerate polarization states, a ferroelectric material could show negative differential capacitance while in non-equilibrium1-5. The state of negative capacitance is unstable, but just as a series resistance can stabilize the negative differential resistance of an Esaki diode, it is also possible to stabilize a ferroelectric in the negative differential capacitance state by placing a series dielectric capacitor 1-3. -

Designing Magnetic Components for Optimum Performance Article

Power Supply Design Seminar Designing Magnetic Components for Optimum Performance in Low-Cost AC/DC Converter Applications Topic Category: Magnetic Component Design Reproduced from 2010 Texas Instruments Power Supply Design Seminar SEM1900, Topic 5 TI Literature Number: SLUP265 © 2010, 2011 Texas Instruments Incorporated Power Seminar topics and online power- training modules are available at: power.ti.com/seminars Designing Magnetic Components for Optimum Performance in Low-Cost AC/DC Converter Applications Seamus O’Driscoll, Peter Meaney, John Flannery, and George Young AbstrAct Assuming that the reader is familiar with basic magnetic design theory, this topic provides design guidance to achieve high efficiency, low electromagnetic interference (EMI), and manufacturing ease for the magnetic components in typical offline power converters. Magnetic-component designs for a 90-W notebook adapter and a 300-W ATX power supply are used as examples. Magnetic applications to be considered include the input EMI filter, power inductor design, high-voltage (HV) level-shifting gate drives, and single- and multiple-output forward-mode transformers in both wound and planar formats. The techniques are also applied to flyback “transformers” (coupled inductors) and will enable lower- profile designs with lower intrinsic common-mode noise generation. I. IntroductIon Gate Drive Note: The SI (extended MKS) units system AC Filter PFC Isolated Main Drive (for some Converter Output(s) is used throughout this topic. CM Inductor, topologies), Balanced Bridge, Differential This material is intended as a high- PFC Inductor, Multi-Output Filter level overview of the primary consider- Bias Flyback ations when designing magnetic components for high-volume and cost- Isolated Feedback optimized applications such as computer Fig. -

APPLICATION NOTE How to Select the Right Reinforced Transformer for High Voltage Energy Storage Applications

APPLICATION NOTE How to Select the Right Reinforced Transformer for High Voltage Energy Storage Applications Introduction Providing isolated low voltage bias power to ICs such as microcontrollers, analog-to-digital HCT Series converters, isolated gate drivers or voltage monitoring ICs in high voltage systems is usually accomplished with an isolated DC-DC converter. If the high voltage system is spread out over several modules, the architecture may call for a parallel DC bus on the low voltage side with multiple isolated low power DC-DC converters for each module. Because it is used multiple times in this scenario, an efficient and cost-effective topology is the best approach. This application note highlights the design benefits of using push-pull transformers that are proven solutions for these situations. Used as an example is the Bourns® Model HCTSM8 series transformer, which is AEC-Q200 compliant and available with a wide range of turns ratios as standard. Multiple turns ratios are an important feature enabling the same basic circuit topology to be replicated across a system with the same components and PCB layout. With a transformer series like the Model HCTSM8, designers are able to select the right reinforced transformer part number based on the specified output voltage for powering a microcontroller or an isolated IGBT gate driver. www.bourns.com 07/20 • e/IC2075 APPLICATION NOTE How to Select the Right Reinforced Transformer for High Voltage Energy Storage Applications Why Push-Pull Transformers are an Optimal Choice Electrical Advantages HCT Series Push-pull transformers are known to operate well with low voltages and low variations in input and output. -

Ferrite and Metal Composite Inductors

Ferrite and Metal Composite Inductors Design and Characteristics © 2019 KEMET Corporation What is an Inductor? Coil Magnetic Magnetic flux φ (Wire) Field dφ Core e = - dt Material i The coil converts electric energy into magnetic energy and stores it. e Core Material Current through the coil of wire creates a magnetic field Air Ferrite Metal and stores it. (None) (Iron) Composite Different core materials change magnetic field strength. © 2019 KEMET Corporation Ferrite Inductor or Metal Composite Inductor? Ferrite InductorFerrite Metal InductorMetal Composite MaterialMaterial Type type Ni-ZnNi-Zn Mn-Zn Mn-Zn Fe based Fe Based Very Good!! No Good.. InductanceInductace GoodGood! Very Good No Good Very Good!! Magnetic Saturation Good! No Good.. Good! No Good.. Very Good!! MagneticThermal Saturation Property Good No Good Very Good Good! Very Good!! Good! Efficiency Very Good!! No Good.. Good! ThermalResistance Property of core Good No Good Very Good Efficiency SBC/SBCPGood TPI Very GoodMPC, MPCV Good Products MPLC, MPLCV Resistance of Core Very Good No Good Good © 2019 KEMET Corporation Ferrite and Metal Composite Comparison Advantage of Ferrite 1. Higher inductance with high permeability 2. Stable inductance in the right range High L and Low DCR capability Advantage of Metal Composite 1. Very slow saturation 2. Very stable saturation for the thermal Core Loss Comparison Good for Auto app especially Advantage of Ferrite Very low core loss in dynamic frequency range Mn-Zn Ferrite Metal Core Low power consumption capability © 2019 KEMET Corporation -

RX200, RX100 Series Application Note Overview of CTSU Operation

APPLICATION NOTE RX200, RX100 Series R01AN3824EU0100 Rev 1.00 Overview of CTSU operation May 10, 2017 Introduction This document gives an operational overview of the capacitive touch sensing unit (CTSU) associated with a variety of RX and Synergy MCUs, including functioning principals and waveforms describing its operation in mutual and self- capacitive modes. Target Device RX230, RX231, RX130, and RX113. Contents 1. The components of capacitive touch ............................................................................. 2 2. Generation of the Electrostatic Field ............................................................................. 2 2.1 Overview of Parasitic capacitance ............................................................................................ 3 3. CTSU Capacitance Estimation ........................................................................................ 4 3.1 Measuring current via the Self-Capacitance Method .............................................................. 4 3.2 Measuring current via the Mutual-Capacitance Method ......................................................... 6 3.2.1 Simulation of the currents in Mutual Mode ........................................................................ 8 3.3 Turning the current to a digital measurement ......................................................................... 9 R01AN3824EU0100 Rev 1.00 Page 1 of 11 May 10, 2017 RX200, RX100 Series Overview of CTSU operation 1. The components of capacitive touch Renesas’ capacitive touch solution -

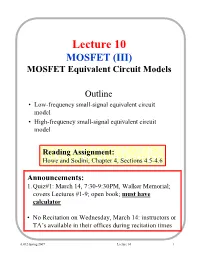

Lecture 10 MOSFET (III) MOSFET Equivalent Circuit Models

Lecture 10 MOSFET (III) MOSFET Equivalent Circuit Models Outline • Low-frequency small-signal equivalent circuit model • High-frequency small-signal equivalent circuit model Reading Assignment: Howe and Sodini; Chapter 4, Sections 4.5-4.6 Announcements: 1.Quiz#1: March 14, 7:30-9:30PM, Walker Memorial; covers Lectures #1-9; open book; must have calculator • No Recitation on Wednesday, March 14: instructors or TA’s available in their offices during recitation times 6.012 Spring 2007 Lecture 10 1 Large Signal Model for NMOS Transistor Regimes of operation: VDSsat=VGS-VT ID linear saturation ID V DS VGS V GS VBS VGS=VT 0 0 cutoff VDS • Cut-off I D = 0 • Linear / Triode: W V I = µ C ⎡ V − DS − V ⎤ • V D L n ox⎣ GS 2 T ⎦ DS • Saturation W 2 I = I = µ C []V − V •[1 + λV ] D Dsat 2L n ox GS T DS Effect of back bias VT(VBS ) = VTo + γ [ −2φp − VBS −−2φp ] 6.012 Spring 2007 Lecture 10 2 Small-signal device modeling In many applications, we are only interested in the response of the device to a small-signal applied on top of a bias. ID+id + v - ds + VDS v + v gs - - bs VGS VBS Key Points: • Small-signal is small – ⇒ response of non-linear components becomes linear • Since response is linear, lots of linear circuit techniques such as superposition can be used to determine the circuit response. • Notation: iD = ID + id ---Total = DC + Small Signal 6.012 Spring 2007 Lecture 10 3 Mathematically: iD(VGS, VDS , VBS; vgs, vds , vbs ) ≈ ID()VGS , VDS ,VBS + id (vgs, vds, vbs ) With id linear on small-signal drives: id = gmvgs + govds + gmbvbs Define: gm ≡ transconductance [S] go ≡ output or drain conductance [S] gmb ≡ backgate transconductance [S] Approach to computing gm, go, and gmb. -

LM2596 SIMPLE SWITCHER Power Converter 150 Khz3a Step-Down

Distributed by: www.Jameco.com ✦ 1-800-831-4242 The content and copyrights of the attached material are the property of its owner. LM2596 SIMPLE SWITCHER Power Converter 150 kHz 3A Step-Down Voltage Regulator May 2002 LM2596 SIMPLE SWITCHER® Power Converter 150 kHz 3A Step-Down Voltage Regulator General Description Features The LM2596 series of regulators are monolithic integrated n 3.3V, 5V, 12V, and adjustable output versions circuits that provide all the active functions for a step-down n Adjustable version output voltage range, 1.2V to 37V (buck) switching regulator, capable of driving a 3A load with ±4% max over line and load conditions excellent line and load regulation. These devices are avail- n Available in TO-220 and TO-263 packages able in fixed output voltages of 3.3V, 5V, 12V, and an adjust- n Guaranteed 3A output load current able output version. n Input voltage range up to 40V Requiring a minimum number of external components, these n Requires only 4 external components regulators are simple to use and include internal frequency n Excellent line and load regulation specifications compensation†, and a fixed-frequency oscillator. n 150 kHz fixed frequency internal oscillator The LM2596 series operates at a switching frequency of n TTL shutdown capability 150 kHz thus allowing smaller sized filter components than n Low power standby mode, I typically 80 µA what would be needed with lower frequency switching regu- Q n lators. Available in a standard 5-lead TO-220 package with High efficiency several different lead bend options, and a 5-lead TO-263 n Uses readily available standard inductors surface mount package. -

High Power Inverters

High Power Inverters Applications Power Converter Capacitors Industries Green Energy Automotive Industrial © 2019 KEMET Corporation Power Converter Components System Overview AC ~ AC ~ AC/DC DC/AC Power Converter Inverter Power Source Load 2 3 6 7 2 7 4 5 5 0 1 Components 0 Common Mode 3 EMI Core 4 Boost Reactor 7 Current Sensor Choke Coil Capacitors 1 EMI / RFI 2 AC Harmonic 5 Snubber 6 DC Link Filter 1Φ Filter 3Φ © 2019 KEMET Corporation 0 Common Mode Choke © 2019 KEMET Corporation AC Line Filters Application Noise is classified according to the conduction mode into either Common Mode of Differential Mode Differential Mode Common Mode Differential Mode Common Mode Electronic Filter lay-out Attenuated with Suppressed by Chokes and Differential Mode is also known as “Normal” Mode. Inductors & X-capacitors Y-capacitors AC Line Filters are choke coil products used to suppress both types of noise. © 2019 KEMET Corporation AC Line Filters How to Tell Between Common and Differential Mode Common Mode Differential or Normal Mode 4 Pins 2 Pins SCR HHB © 2019 KEMET Corporation New Ferrite Material High µ Ferrite Development Developed the Highest µ S18H © 2019 KEMET Corporation High Performance Line Filter SCR-HB (SR18) New Product Features • Use of high performance SR18 material • High current (~50A) and high voltage (500V) Advantages SCR-HB(S18H) • High impedance (greater than any other ferrite +35% common mode choke) -30% • Same performance in smaller size and less Conventional SCR(S15H) winding Conventional SC(10H) • Custom designs available -

American Cores & Electronics

The broadest range of magnetic cores from a single source - Call Toll Free: 800-898-1883 Home Product Specifications Value- Request Contact Selection Added Quote Us Iron Powder Cores These cores are composed of finely defined particles of iron which are insulated from each other but bound together with a binding compound. The iron powder and binding compound are mixed and compressed under heavy pressure, and baked at high temperature. The characteristics of the cores are determined by the size and density of the core, and the property of the iron powder. Powdered iron cores do not saturate easily, and has high core temperature stability and Q. However, it is only available in low permeability (below µi = 110). The high temperature stability makes it suitable for applications such as narrow band filter inductors, tuned transformers, oscillators and tank circuits. Iron Powder Cores are made in numerous and sizes: such as Toroidal Cores, E-cores, Shielded Coil Forms, Sleeves etc., each of which is available in many different materials. There are two basic groups of iron powder material: The Carbonyl Iron and, The Hydrogen Reduced Iron. The Carbonyl Iron cores are especially noted for their stability over a wide range of temperatures and flux levels. Their permeability range is from less than 3 µi to 35 µi and can offer excellent 'Q' factors from 50 KHz to 200 MHz. They are ideally suited for a variety of RF applications where good stability and good 'Q' are essential. Also, they are very much in demand for broadband inductors, especially where high power is concerned.