Designing Magnetic Components for Optimum Performance Article

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Class-E Audio Modulated Tesla Coil Instruction Manual

Class-E Audio Modulated Tesla Coil CCllaassss--EE AAuuddiioo MMoodduullaatteedd TTeessllaa CCooiill IInnssttrruuccttiioonn MMaannuuaall Eastern Voltage Research, LLC May 19, 2017 REV F − 1 − http://www.EasternVoltageResearch.com Class-E Tesla Coil Instruction Manual Class-E Audio Modulated Tesla Coil BOARD REVISION C This manual only applies to the new Revision C PCB boards. These boards can be identified by their red or green silkscreen color as well as the marking SC2076 REV C which is located underneath the location for T41 on the upper right of the PCB board. May 19, 2017 REV F − 2 − http://www.EasternVoltageResearch.com Class-E Tesla Coil Instruction Manual Class-E Audio Modulated Tesla Coil AGE DISCLAIMER THIS KIT IS AN ADVANCED, HIGH POWER SOLID STATE POWER DEVICE. IT IS INTENDED FOR USE FOR INDIVIDUALS OVER 18 YEARS OF AGE WITH THE PROPER KNOWLEDGE AND EXPERIENCE, AS WELL AS FAMILIARITY WITH LINE VOLTAGE POWER CIRCUITS. BY BUILDING, USING, OR OPERATING THIS KIT, YOU ACKNOWLEDGE THAT YOU ARE OVER 18 YEARS OF AGE, AND THAT YOU HAVE THOROUGHLY READ THROUGH THE SAFETY INFORMATION PRESENTED IN THIS MANUAL. THIS KIT SHALL NOT BE USED AT ANY TIME BY INDIVIDUALS UNDER 18 YEARS OF AGE. May 19, 2017 REV F − 3 − http://www.EasternVoltageResearch.com Class-E Tesla Coil Instruction Manual Class-E Audio Modulated Tesla Coil SAFETY AND EQUIPMENT HAZARDS PLEASE BE SURE TO READ AND UNDERSTAND ALL SAFETY AND EQUIPMENT RELATED HAZARDS AND WARNINGS BEFORE BUILDING AND OPERATING YOUR KIT. THE PURPOSE OF THESE WARNINGS IS NOT TO SCARE YOU, BUT TO KEEP YOU WELL INFORMED TO WHAT HAZARDS MAY APPLY FOR YOUR PARTICULAR KIT. -

Chapter 6 BUILDING a HOMEBREW

1. Chapter 6, Harris CRYSTAL SETS TO SIDEBAND © Frank W. Harris 2002 Chapter 6 BUILDING A HOMEBREW QRP Among the guys I work, QRPs seem to be the most common homebrew project, second only to building antennas. Therefore this chapter describes a simple QRP design I have settled on. I use my QRPs as stand-alone transmitters or I use them to drive a final amplifier to produce higher power, 25 to 100 watts. It’s true that before you build a transmitter you’ll need a receiver. Unfortunately, a good selective, all-band ham receiver is complicated to build and most guys don’t have the time and enthusiasm to do it. (See chapter 13.) The next chapter describes building a simple, 5 transistor 40 meter receiver which I have used with the QRP below to talk to other hams. This simple receiver will work best during off hours when 40 meters isn’t crowded. It can also be used to receive Morse code for code practice. A 40 meter QRP module. The QRP transmitter above is designed exclusively for 40 meters, (7.000 to 7.300 MHz.) The twelve-volt power supply comes in through the pig-tail wire up on the right. The telegraph key plugs into the blue-marked phono plug socket on the right of the aluminum heat sink. The antenna output is the red-colored socket on the left end of the heat sink. The transmitting frequency of the QRP module is controlled by a quartz crystal. That’s the silver rectangular can plugged into the box on the right front. -

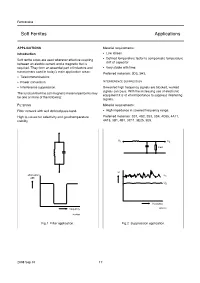

Soft Ferrites Applications

Ferroxcube Soft Ferrites Applications APPLICATIONS Material requirements: Introduction • Low losses • Defined temperature factor to compensate temperature Soft ferrite cores are used wherever effective coupling drift of capacitor between an electric current and a magnetic flux is required. They form an essential part of inductors and • Very stable with time. transformers used in today’s main application areas: Preferred materials: 3D3, 3H3. • Telecommunications • Power conversion INTERFERENCE SUPPRESSION • Interference suppression. Unwanted high frequency signals are blocked, wanted signals can pass. With the increasing use of electronic The function that the soft magnetic material performs may equipment it is of vital importance to suppress interfering be one or more of the following: signals. FILTERING Material requirements: Filter network with well defined pass-band. • High impedance in covered frequency range. High Q-values for selectivity and good temperature Preferred materials: 3S1, 4S2, 3S3, 3S4, 4C65, 4A11, stability. 4A15, 3B1, 4B1, 3C11, 3E25, 3E5. andbook, halfpage handbook, halfpage U1 U2 load U attenuation U1 (dB) U2 frequency frequency MBW404 MBW403 Fig.1 Filter application. Fig.2 Suppression application. 2008 Sep 01 17 Ferroxcube Soft Ferrites Applications DELAYING PULSES STORAGE OF ENERGY The inductor will block current until saturated. Leading An inductor stores energy and delivers it to the load during edge is delayed depending on design of magnetic circuit. the off-time of a Switched Mode Power Supply (SMPS). Material requirements: Material requirements: • High permeability (µi). • High saturation level (Bs). Preferred materials: 3E25, 3E5, 3E6, 3E7, 3E8, 3E9. Preferred materials: 3C30, 3C34, 3C90, 3C92, 3C96 2P-iron powder. U U handbook, halfpage 1 handbook, halfpage1 U2 U2 SMPS load delay U U U1 U2 U1 U2 time time MBW405 MBW406 Fig.3 Pulse delay application. -

Common Mode Chokes by Würth Elektronik

Welcome! Inductors & EMC-Ferrites Basics - Parts and Applications Wurth Electronics Inc. Field Application Engineer Michael Eckert Würth Elektronik eiSos © May/2006 Michael Eckert What is an Inductor ? technical view: a piece of wire wounded on something a filter an energy-storage-part (short-time) examples: Würth Elektronik eiSos © May/2006 Michael Eckert What is an EMC-Ferrite ? Technical view: Frequency dependent filter Absorber for RF-energy examples: EMC Snap-Ferrites EMC-Ferrites for SMD-Ferrites Flatwire Würth Elektronik eiSos © May/2006 Michael Eckert Magnetic Field Strenght H of some configurations I long, straight wire H = 2⋅π ⋅R N⋅I Toroidal Coil H = 2⋅π ⋅R N⋅I Long solenoid H = l (e.g. rod core indcutor) Würth Elektronik eiSos © May/2006 Michael Eckert Example: Conducted Emission Measurement • Dosing pump for chemicals industry. Würth Elektronik eiSos © May/2006 Michael Eckert Conducted Emission Measurement • Power supply V 1.0 PCB Buck Converter ST L4960/2.5A/fs 85-115KHz Würth Elektronik eiSos © May/2006 Michael Eckert Conducted Emission Measurement • Power supply V 1.1 PCB Schematic Würth Elektronik eiSos © May/2006 Michael Eckert Awareness: • Select the right parts for your application • Do not always look on cost Very easy solution with a dramatic result!!! or Choke before Choke after Würth Elektronik eiSos © May/2006 Michael Eckert What is permeability [ur]? – Permability (µr): describe the capacity of concentration of the magnetic flux in the material. typical permeabilities [µr] : Magnetic induction in ferrite: -

Custom Power Supplies, Transformers, Chokes & Reactors

YOUR POWER SOURCE Custom Power Supplies, Transformers, Chokes & Reactors NeeltranThe Story Transformers and Power Supplies • Industry Leader since 1973 Neeltran has become the most reliable supplier of Transformers and Power Supply Systems in the industry. Our engineers, along with our manufacturing team, have the knowledge and ability to meet the special needs of our customers. All power supplies are custom designed to your specifications by our engineering staff and completely fabricated in-house at our manufacturing facility. Our facilities and experience include: • Research & Development Since 1973 Neeltran has been a leading • Test Laboratory manufacturer of transformers and • Design Engineering power supplies. • Printed Circuit Board Manufacturing Our general product range is: • Steel Cutting Machinery • Dry Type and Water Cooled Transformers: • Baking Ovens 5–10,000 KVA (up to 25 KV input) • Vacuum Pressure Impregnation Tanks (Outputs up to 300 KV and 50 KHZ) • Coil Winding Equipment • Oil filled Transformers (Rectifier type only): 100 KVA to 50 MVA (up to 69 KV input) • Painting and Steel Fabrication to manufacture our own enclosures • Oil filled high frequency Transformers: • Assembly Areas up to 50 KHZ, 2000 KVA, up to 50 KV output Industry standards are maintained with our • Cast Coil Transformers: up to 20 MVA testing equipment assuring that all shipped (up to 35 KV input) products meet customer’s requirements and • Chokes and Reactors air or iron: specifications. Impulse testing as well as customer up to 25 KV, 20,000 amps specific testing is available upon request. • Power Supplies: 100 A to 500,000 amp (AC or DC) 1500 VDC. Special outputs up to 300,000 volts AC or DC and high frequencies are available. -

Checking out the Power Supply the Power Supply Must Be Carefully Checked out a Good Many Australian-Made Sets from the Mid 1930S-1950 Era

Checking out the power supply The power supply must be carefully checked out a good many Australian-made sets from the mid 1930s-1950 era. Fig.1 before switching on a vintage radio. The shows a typical circuit configura- components most likely to be at fault are the tion but there are other variations. electrolytic capacitors, most of which should be For example, some rectifiers re- quire a cathode voltage of 6.3V AC, replaced as a matter of course. not 5V. Similarly, not all radio valves use Although only a few parts are in- (equivalent to 570 volts, centre- 6.3V heater supplies. There are volved, the power supply is a com- tapped). 2.5V valves, 4V valves and 12V mon source of problems in vintage The 5V and 6.3V AC supplies are valves in some late model sets. In radios. It should be carefully check- wired straight from the trans- these radios, the low tension ed out before power is applied, as a former to the filaments and voltages on the transformer will be fault here can quickly cause heaters. However, the high tension different — but that's about all. damage to critical components. supply must be rectified to give a The high tension voltage will still be Most mains-operated valve high-tension DC supply for the well in excess of 250 volts. radios have three separate secon- anodes and screens for the various The output from the rectifier dary windings on the power receiving and output valves. A valve will not be pure DC but does transformer. -

APPLICATION NOTE How to Select the Right Reinforced Transformer for High Voltage Energy Storage Applications

APPLICATION NOTE How to Select the Right Reinforced Transformer for High Voltage Energy Storage Applications Introduction Providing isolated low voltage bias power to ICs such as microcontrollers, analog-to-digital HCT Series converters, isolated gate drivers or voltage monitoring ICs in high voltage systems is usually accomplished with an isolated DC-DC converter. If the high voltage system is spread out over several modules, the architecture may call for a parallel DC bus on the low voltage side with multiple isolated low power DC-DC converters for each module. Because it is used multiple times in this scenario, an efficient and cost-effective topology is the best approach. This application note highlights the design benefits of using push-pull transformers that are proven solutions for these situations. Used as an example is the Bourns® Model HCTSM8 series transformer, which is AEC-Q200 compliant and available with a wide range of turns ratios as standard. Multiple turns ratios are an important feature enabling the same basic circuit topology to be replicated across a system with the same components and PCB layout. With a transformer series like the Model HCTSM8, designers are able to select the right reinforced transformer part number based on the specified output voltage for powering a microcontroller or an isolated IGBT gate driver. www.bourns.com 07/20 • e/IC2075 APPLICATION NOTE How to Select the Right Reinforced Transformer for High Voltage Energy Storage Applications Why Push-Pull Transformers are an Optimal Choice Electrical Advantages HCT Series Push-pull transformers are known to operate well with low voltages and low variations in input and output. -

Measured Data for Chokes Wound on New Big #31 Toroid

A New Choke Cookbook for the 160–10M Bands Using Fair-Rite #31 2.4-in o.d. (2631803802) and 4-in o.d. (2631814002) Toroids © 2018-19 by James W. Brown All Rights Reserved Introduction: Common mode chokes are added as series elements to a transmission line to kill common mode current. The line may be a short one carrying audio or control signals between a computer and a radio, video between a computer and a monitor, noisy power wiring, or feedlines for antennas. This application note focuses on the use of chokes on the feedlines of high power transmitting antennas to suppress received noise, to minimize RF in the shack (and a neighbor’s living room) and to minimize crosstalk between stations in multi-transmitter environments. Fundamentals Differential mode current is the normal transmission of power or other signals inside coax, or between paired conductors. The currents in the two conductors are precisely equal and are out of polarity (that is, flowing in opposite directions at each point along the line). Because the current in the two conductors are equal and out of polarity, they do not radiate, nor do they receive. Common mode current is carried on the outside of the coax shield, or as the difference of unequal currents on the two conductors of 2-wire line. A line carrying common mode current acts as antenna for both transmit and receive. Common mode current that couples to the antenna changes the directional pattern of an antenna by filling in the nulls of it’s directional pattern. -

Very High Frequency Integrated POL for Cpus

Very High Frequency Integrated POL for CPUs Dongbin Hou Dissertation submitted to the Faculty of the Virginia Polytechnic Institute and State University in partial fulfillment of the requirements for the degree of DOCTOR OF PHILOSOPHY in Electrical Engineering Fred C. Lee, Chair Qiang Li Rolando Burgos Daniel J. Stilwell Dwight D. Viehland March 23rd, 2017 Blacksburg, Virginia Keywords: Point-of-load converter, integrated voltage regulator, very high frequency, 3D integration, ultra-low profile inductor, magnetic characterizations, core loss measurement © 2017, Dongbin Hou Dongbin Hou Very High Frequency Integrated POL for CPUs Dongbin Hou Abstract Point-of-load (POL) converters are used extensively in IT products. Every piece of the integrated circuit (IC) is powered by a point-of-load (POL) converter, where the proximity of the power supply to the load is very critical in terms of transient performance and efficiency. A compact POL converter with high power density is desired because of current trends toward reducing the size and increasing functionalities of all forms of IT products and portable electronics. To improve the power density, a 3D integrated POL module has been successfully demonstrated at the Center for Power Electronic Systems (CPES) at Virginia Tech. While some challenges still need to be addressed, this research begins by improving the 3D integrated POL module with a reduced DCR for higher efficiency, the vertical module design for a smaller footprint occupation, and the hybrid core structure for non-linear inductance control. Moreover, as an important category of the POL converter, the voltage regulator (VR) serves an important role in powering processors in today’s electronics. -

Ferrite and Metal Composite Inductors

Ferrite and Metal Composite Inductors Design and Characteristics © 2019 KEMET Corporation What is an Inductor? Coil Magnetic Magnetic flux φ (Wire) Field dφ Core e = - dt Material i The coil converts electric energy into magnetic energy and stores it. e Core Material Current through the coil of wire creates a magnetic field Air Ferrite Metal and stores it. (None) (Iron) Composite Different core materials change magnetic field strength. © 2019 KEMET Corporation Ferrite Inductor or Metal Composite Inductor? Ferrite InductorFerrite Metal InductorMetal Composite MaterialMaterial Type type Ni-ZnNi-Zn Mn-Zn Mn-Zn Fe based Fe Based Very Good!! No Good.. InductanceInductace GoodGood! Very Good No Good Very Good!! Magnetic Saturation Good! No Good.. Good! No Good.. Very Good!! MagneticThermal Saturation Property Good No Good Very Good Good! Very Good!! Good! Efficiency Very Good!! No Good.. Good! ThermalResistance Property of core Good No Good Very Good Efficiency SBC/SBCPGood TPI Very GoodMPC, MPCV Good Products MPLC, MPLCV Resistance of Core Very Good No Good Good © 2019 KEMET Corporation Ferrite and Metal Composite Comparison Advantage of Ferrite 1. Higher inductance with high permeability 2. Stable inductance in the right range High L and Low DCR capability Advantage of Metal Composite 1. Very slow saturation 2. Very stable saturation for the thermal Core Loss Comparison Good for Auto app especially Advantage of Ferrite Very low core loss in dynamic frequency range Mn-Zn Ferrite Metal Core Low power consumption capability © 2019 KEMET Corporation -

LM2596 SIMPLE SWITCHER Power Converter 150 Khz3a Step-Down

Distributed by: www.Jameco.com ✦ 1-800-831-4242 The content and copyrights of the attached material are the property of its owner. LM2596 SIMPLE SWITCHER Power Converter 150 kHz 3A Step-Down Voltage Regulator May 2002 LM2596 SIMPLE SWITCHER® Power Converter 150 kHz 3A Step-Down Voltage Regulator General Description Features The LM2596 series of regulators are monolithic integrated n 3.3V, 5V, 12V, and adjustable output versions circuits that provide all the active functions for a step-down n Adjustable version output voltage range, 1.2V to 37V (buck) switching regulator, capable of driving a 3A load with ±4% max over line and load conditions excellent line and load regulation. These devices are avail- n Available in TO-220 and TO-263 packages able in fixed output voltages of 3.3V, 5V, 12V, and an adjust- n Guaranteed 3A output load current able output version. n Input voltage range up to 40V Requiring a minimum number of external components, these n Requires only 4 external components regulators are simple to use and include internal frequency n Excellent line and load regulation specifications compensation†, and a fixed-frequency oscillator. n 150 kHz fixed frequency internal oscillator The LM2596 series operates at a switching frequency of n TTL shutdown capability 150 kHz thus allowing smaller sized filter components than n Low power standby mode, I typically 80 µA what would be needed with lower frequency switching regu- Q n lators. Available in a standard 5-lead TO-220 package with High efficiency several different lead bend options, and a 5-lead TO-263 n Uses readily available standard inductors surface mount package. -

High Power Inverters

High Power Inverters Applications Power Converter Capacitors Industries Green Energy Automotive Industrial © 2019 KEMET Corporation Power Converter Components System Overview AC ~ AC ~ AC/DC DC/AC Power Converter Inverter Power Source Load 2 3 6 7 2 7 4 5 5 0 1 Components 0 Common Mode 3 EMI Core 4 Boost Reactor 7 Current Sensor Choke Coil Capacitors 1 EMI / RFI 2 AC Harmonic 5 Snubber 6 DC Link Filter 1Φ Filter 3Φ © 2019 KEMET Corporation 0 Common Mode Choke © 2019 KEMET Corporation AC Line Filters Application Noise is classified according to the conduction mode into either Common Mode of Differential Mode Differential Mode Common Mode Differential Mode Common Mode Electronic Filter lay-out Attenuated with Suppressed by Chokes and Differential Mode is also known as “Normal” Mode. Inductors & X-capacitors Y-capacitors AC Line Filters are choke coil products used to suppress both types of noise. © 2019 KEMET Corporation AC Line Filters How to Tell Between Common and Differential Mode Common Mode Differential or Normal Mode 4 Pins 2 Pins SCR HHB © 2019 KEMET Corporation New Ferrite Material High µ Ferrite Development Developed the Highest µ S18H © 2019 KEMET Corporation High Performance Line Filter SCR-HB (SR18) New Product Features • Use of high performance SR18 material • High current (~50A) and high voltage (500V) Advantages SCR-HB(S18H) • High impedance (greater than any other ferrite +35% common mode choke) -30% • Same performance in smaller size and less Conventional SCR(S15H) winding Conventional SC(10H) • Custom designs available