13. Stored-Program Computers

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

COM 113 INTRO to COMPUTER PROGRAMMING Theory Book

1 [Type the document title] UNESCO -NIGERIA TECHNICAL & VOCATIONAL EDUCATION REVITALISATION PROJECT -PHASE II NATIONAL DIPLOMA IN COMPUTER TECHNOLOGY Computer Programming COURSE CODE: COM113 YEAR I - SE MESTER I THEORY Version 1: December 2008 2 [Type the document title] Table of Contents WEEK 1 Concept of programming ................................................................................................................ 6 Features of a good computer program ............................................................................................ 7 System Development Cycle ............................................................................................................ 9 WEEK 2 Concept of Algorithm ................................................................................................................... 11 Features of an Algorithm .............................................................................................................. 11 Methods of Representing Algorithm ............................................................................................ 11 Pseudo code .................................................................................................................................. 12 WEEK 3 English-like form .......................................................................................................................... 15 Flowchart ..................................................................................................................................... -

Defining Computer Program Parts Under Learned Hand's Abstractions Test in Software Copyright Infringement Cases

Michigan Law Review Volume 91 Issue 3 1992 Defining Computer Program Parts Under Learned Hand's Abstractions Test in Software Copyright Infringement Cases John W.L. Ogilive University of Michigan Law School Follow this and additional works at: https://repository.law.umich.edu/mlr Part of the Computer Law Commons, Intellectual Property Law Commons, and the Judges Commons Recommended Citation John W. Ogilive, Defining Computer Program Parts Under Learned Hand's Abstractions Test in Software Copyright Infringement Cases, 91 MICH. L. REV. 526 (1992). Available at: https://repository.law.umich.edu/mlr/vol91/iss3/5 This Note is brought to you for free and open access by the Michigan Law Review at University of Michigan Law School Scholarship Repository. It has been accepted for inclusion in Michigan Law Review by an authorized editor of University of Michigan Law School Scholarship Repository. For more information, please contact [email protected]. NOTE Defining Computer Program Parts Under Learned Hand's Abstractions Test in Software Copyright Infringement Cases John W.L. Ogilvie INTRODUCTION Although computer programs enjoy copyright protection as pro tectable "literary works" under the federal copyright statute, 1 the case law governing software infringement is confused, inconsistent, and even unintelligible to those who must interpret it.2 A computer pro gram is often viewed as a collection of different parts, just as a book or play is seen as an amalgamation of plot, characters, and other familiar parts. However, different courts recognize vastly different computer program parts for copyright infringement purposes. 3 Much of the dis array in software copyright law stems from mutually incompatible and conclusory program part definitions that bear no relation to how a computer program is actually designed and created. -

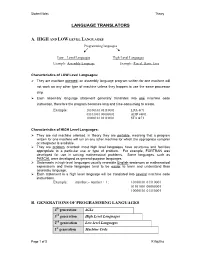

Language Translators

Student Notes Theory LANGUAGE TRANSLATORS A. HIGH AND LOW LEVEL LANGUAGES Programming languages Low – Level Languages High-Level Languages Example: Assembly Language Example: Pascal, Basic, Java Characteristics of LOW Level Languages: They are machine oriented : an assembly language program written for one machine will not work on any other type of machine unless they happen to use the same processor chip. Each assembly language statement generally translates into one machine code instruction, therefore the program becomes long and time-consuming to create. Example: 10100101 01110001 LDA &71 01101001 00000001 ADD #&01 10000101 01110001 STA &71 Characteristics of HIGH Level Languages: They are not machine oriented: in theory they are portable , meaning that a program written for one machine will run on any other machine for which the appropriate compiler or interpreter is available. They are problem oriented: most high level languages have structures and facilities appropriate to a particular use or type of problem. For example, FORTRAN was developed for use in solving mathematical problems. Some languages, such as PASCAL were developed as general-purpose languages. Statements in high-level languages usually resemble English sentences or mathematical expressions and these languages tend to be easier to learn and understand than assembly language. Each statement in a high level language will be translated into several machine code instructions. Example: number:= number + 1; 10100101 01110001 01101001 00000001 10000101 01110001 B. GENERATIONS OF PROGRAMMING LANGUAGES 4th generation 4GLs 3rd generation High Level Languages 2nd generation Low-level Languages 1st generation Machine Code Page 1 of 5 K Aquilina Student Notes Theory 1. MACHINE LANGUAGE – 1ST GENERATION In the early days of computer programming all programs had to be written in machine code. -

Programming Fundamentals - I Basic Concepts Fall-Semester 2016

Programming Fundamentals - I Basic Concepts Fall-Semester 2016 Prepared By: Rao Muhammad Umer Lecturer, Web: raoumer.github.io Department of Computer Science & IT, The University of Lahore. What is computer? The term "computer" was originally given to humans who performed numerical calculations using mechanical calculators, such as the abacus and slide rule. The term was later given to a mechanical device as they began replacing the human computers. Today's computers are electronic devices that accept data such as numbers, text, sound, image, animations, video, etc., (input), process that data (converts data to information) , produce output, and then store (storage) the results. A basic computer consists of 4 components: 1. Input devices 2. Central Processing Unit or CPU 3. Output devices 4. Memory Input Devices are used to provide input to the computer basic input devices include keyboard, mouse, touch screens etc. Central Processing Unit acts like a brain, it processes all instructions and data in the computer, the instructions are computer commands, these commands are given to CPU by input devices, some of the instructions are generated by the computer itself Output devices are used to receive computer output, the output, some basic output devices are hard drive disk (HDD, commonly known as hard disk), printers, computer screens (Monitors and LCDs) The computer memory is a temporary storage area. It holds the data and instructions that the Central Processing Unit (CPU) needs. Before a program can be run, the program is loaded from some storage device such as into the memory, the CPU loads the program or part of the program from the memory and executes it. -

Introduction to Computer Programming

Introduction to Computer Programming CISC1600/1610 Computer Science I/Lab Spring 2016 CISC1600 Yanjun Li 1 Outline This Course Computer Programming Spring 2016 CISC1600 Yanjun Li 2 1 This is a course In Programming For beginners who want to become professionals or who would like to know something about programming who are assumed to be bright Though not (necessarily) geniuses who are willing to work hard Though do need sleep occasionally, and take a normal course load Using the C++ programming language Spring 2016 CISC1600 Yanjun Li 3 Learning Goals Learn Fundamental programming concepts Key useful techniques Basic Standard C++ facilities After the course, you’ll be able to Write small sound C++ programs Read much larger programs Learn the basics of many other languages by yourself Proceed with an “advanced” C++ programming course After the course, you will not (yet) be An expert programmer A C++ language expert An expert user of advanced libraries Spring 2016 CISC1600 Yanjun Li 4 2 The Means Lectures Attend every one Outside of lectures Read a chapter ahead, and read the chapter again after each lecture Read actively: with questions in mind, try to reorganize/rephrase the key points in your mind Review questions/Terms in chapters Drills Always do the drills, before the exercises Exercises Spring 2016 CISC1600 Yanjun Li 5 The Means (Cont.) Lab projects That’s where the most fun and the best learning takes place Don’t wait until lab section to start the project Start to think about the project early Finish up & get help during labs Exams Midterms Final Spring 2016 CISC1600 Yanjun Li 6 3 How to be Successful? Don’t study alone when you don’t have to Form study groups Do help each other (without plagiarizing) If in doubt if a collaboration is legitimate: ask! Don’t claim to have written code that you copied from others Don’t give anyone else your code (to hand in for a grade) When you rely on the work of others, explicitly list all of your sources – i.e. -

Lecture 1: Introduction to Java®

Lecture 1: Introduction to Java MIT-AITI Kenya 2005 1 Lecture Outline • What a computer program is • How to write a computer program • The disadvantages and advantages of using Java • How a program that you write in Java is changed into a form that your computer can understand • Sample Java code and comments MIT-Africa Internet Technology Initiative ©2005 2 Computer Program vs. Food Recipe Food Recipe Computer Program A chef writes a set of A programmer writes a set of instructions called a recipe instructions called a program The recipe requires specific The program requires specific ingredients inputs The cook follows the The computer follows the instructions step-by-step instructions step-by-step The food will vary depending on The output will vary depending the amount of ingredients and on the values of the inputs and the cook the computer MIT-Africa Internet Technology Initiative ©2005 3 Recipe and Program Examples Student’s Student’s Ingredient # 1 Ingredient # 2 Name Grade Recipe Program Dinner “Bilha got an A on the exam!” MIT-Africa Internet Technology Initiative ©2005 4 What is a computer program? • For a computer to be able to perform specific tasks (i.e. print what grade a student got on an exam), it must be given instructions to do the task • The set of instructions that tells the computer to perform specific tasks is known as a computer program MIT-Africa Internet Technology Initiative ©2005 5 Writing Computer Programs • We write computer programs (i.e. a set of instructions) in programming languages such as C, Pascal, and -

What Is a Computer Program? 1 High-Level Vs Low-Level Languages

What Is A Computer Program? Scientific Computing Fall, 2019 Paul Gribble 1 High-level vs low-level languages1 2 Interpreted vs compiled languages3 What is a computer program? What is code? What is a computer language? A computer program is simply a series of instructions that the computer executes, one after the other. An instruction is a single command. A program is a series of instructions. Code is another way of referring to a single instruction or a series of instructions (a program). 1 High-level vs low-level languages The CPU (central processing unit) chip(s) that sit on the motherboard of your computer is the piece of hardware that actually executes instructions. A CPU only understands a relatively low-level language called machine code. Often machine code is generated automatically by translating code written in assembly language, which is a low-level programming language that has a relatively direcy relationship to machine code (but is more readable by a human). A utility program called an assembler is what translates assembly language code into machine code. In this course we will be learning how to program in MATLAB, which is a high-level programming language. The “high-level” refers to the fact that the language has a strong abstraction from the details of the computer (the details of the machine code). A “strong abstraction” means that one can operate using high-level instructions without having to worry about the low-level details of carrying out those instructions. An analogy is motor skill learning. A high-level language for human action might be drive your car to the grocery store and buy apples. -

Virtual Machines for Dynamic Languages Ausgewählte Kapitel Der Systemsoftwaretechnik, WS2021

Virtual Machines for Dynamic Languages Ausgewählte Kapitel der Systemsoftwaretechnik, WS2021 Mark Deutel Friedrich-Alexander-University Erlangen-Nürnberg (FAU) Erlangen, Germany [email protected] ABSTRACT threading model. It is common that once a dynamic language has A common approach to execute dynamic languages is inside a vir- grown popular enough the interpreter is extended by a just-in-time tual machine (VM), usually implemented in a low level system (JIT) compiler to more efficiently execute interpreted code. language like C. Such VMs have to support the often complex However this approach does not come without problems. The syntax and semantics of the dynamic languages they are hosting. effort required to write a complete virtual machine from scratch Additionally, some properties of dynamic language code can only is huge. It also forces the language implementer to deal with plat- be inferred at runtime making the optimization of code execution form or target architecture specific details. This makes implement- another challenging task. Therefore, it is hardly possible to provide ing a VM time consuming, error prone, and complicated to port general purpose implementations that support a large range of to other systems. Additionally, modern dynamic languages like different dynamic languages. Furthermore, many commonly used Python, Ruby or JavaScript evolve rapidly and have complex syn- dynamic languages such as Python or Javascript are still evolving tax and semantics. This not only makes it hard to represent the which means that their VMs have to adapt constantly. This implies language properly in low level code, but makes maintenance of that it is necessary to write and maintain a sufficiently elaborated existing VM implementations a complicated task as well. -

Computer Programming

d. Ballpoint pens or sharpened pencils e. Blank notebook paper COMPUTER f. All competitors must create a one-page résumé and submit a hard copy to the PROGRAMMING technical committee chair at orientation. Failure to do so will result in a 10-point penalty. PURPOSE To evaluate each contestant’s preparation for Note: Your contest may also require a hard employment and to recognize outstanding copy of your résumé as part of the actual students for excellence and professionalism in contest. Check the Contest Guidelines the field of computer programming. and/or the updates page on the SkillsUSA website: http://updates.skillsusa.org. First, download and review the General Regulations at: http://updates.skillsusa.org. SCOPE OF THE CONTEST The contest uses competencies identified by the ELIGIBILITY Computing Technology Industry Association. Open to active SkillsUSA members enrolled in The specific projects chosen for national programs with computer programming as the competition will be determined by the occupational objective. Computer Programming technical committee. Knowledge Performance CLOTHING REQUIREMENTS The contest includes a written knowledge test Class E: Contest specific — Business Casual assessing knowledge of Visual Basic, Java, C++ • Official SkillsUSA white polo shirt or RPG or “other approved language.” Check • Black dress slacks (accompanied by black the Contest Guidelines and/or the updates page dress socks or black or skin-tone seamless on the SkillsUSA website: updates.skillsusa.org. hose) or black dress skirt (knee-length, accompanied by black or skin-tone Skill Performance seamless hose) The contest includes a computer programming • Black leather closed-toe dress shoes problem consisting of background information and program specifications with accompanying These regulations refer to clothing items that reference materials and description of program are pictured and described at: output requirements. -

Introduction to Computer Programming with C Language

Introduction to Computer Programming with C Language BY Dr. MOHAMED ANWAR MODIFIED BY Dr. EMAD SAMI C Language Course Chapters 1. Introduction 2. Program development 3. The Essentials of C programs 4. Manipulating data with operators 5. Reading and writing standard I/O 6. Decision 7. Iteration 8. Arrays 9. C functions 1. Introduction Chapter Objectives: 1-1 Computer Program 1-2 Programming Languages 1-3 The C programming Language 1-4 Interpreter 1-5 Compiler 1-6 Assembler 1-7 Setting up the computer 1-8 The C-Free 4.0 IDE Preparation Steps 1-9 The first C program 1-1 Computer Program • A computer program is a sequence of instructions written to perform a specified task with a computer. • The program has an executable form (i.e., after your write the program to performs a specific task and then save it, .exe file is obtained for running) • The .exe program: # It has human readable form called the source code # this source code is written by computer programmers. # this source code written using a programming language. # an interpreter or compiler is used to convert the source code into .exe form. 1-2 Programming Languages • It is an artificial language designed to communicate instructions to a computer. • It has a text form (i.e., it contains words, numbers, and punctuation). • Have three groups: machine language, assembly language and high level language. 1-2 Programming Languages (Cont’s) • machine language: – program code has 0’s and 1’s only. – difficult to read and write. • assembly language: – Its level higher than machine language. -

Computers and History Outline What Is a Computer?

Computer system • Hardware -- physical components of Computers and History computer that you see or touch • Software -- computer programs that instruct hardware to perform specific tasks • A computer program is a set of instructions written in a programming language. CS 1305 Intro to Computers and History 4 Computer Tecnology Outline Basic Computer Components • Computer and information • Central Processing Unit • History of computer technology • Storage -- memory • Input devices • Output devices CS 1305 Intro to Computers and History 2 CS 1305 Intro to Computers and History 5 Computer Tecnology Computer Tecnology What is a computer? Categories of Computers A computer is an information-processing • Personal computer (PC) machine that performs simple tasks • Minicomputers according to specific instructions. This • Mainframe computers means it can store, retrieve, output and process data. • Supercomputers Data is a collection of unorganized facts or information, which includes words, numbers, images, and sound. CS 1305 Intro to Computers and History 3 CS 1305 Intro to Computers and History 6 Computer Tecnology Computer Tecnology 1 Personal Computers Supercomputers • Desktop computers A supercomputer is the fastest, most • Network of computers and Web appliances powerful, and most expensive. It is -- WebTV designed specifically for applications • Laptop or notebook computers requiring complex, sophisticated mathematical calculations -- weather • Handheld computers -- small personal forecasting, medical image processing, computers petroleum exploration,... CS 1305 Intro to Computers and History 7 CS 1305 Intro to Computers and History 10 Computer Tecnology Computer Tecnology Minicomputers Software A minicomputer is designed for a small group • System software of organizations with a more powerful – Operating system computing capabilities. The computing – System utilities process of a minicomputer can be accessed • Application software by several users via terminal that connected to it. -

Instructions for Creating a Computer Program Using the C Langua

Creating a Simple Computer Program Using the C Language Creating a simple executable program using the C language is a straight-forward process. This process can be broken down into four processes: 1. Edit Create or edit a source file using a text editor. 2. Preprocess Replace macros, process header files, and remove comments. 3. Compile Check the validity of the code and translate the source (text) file into machine (binary) code. 4. Link Combine other object code and libraries to make one final executable program. 5. Execute Run the program making sure it functions correctly. These processes are commonly referred to as the edit/preprocess/compile/link/execute loop. Figure 1 on the next page shows the flow chart of this process. It is called a loop because if the execution of the program (step five) does not work properly, you must start at step one and repeat the loop. Step1: Editing The first step is to create a file using a text editor. (Do not use a word processor, such as Microsoft Word. Word processors save files in their native format which is incompatible with programming tools.) The file you create should end with a .c extension and is referred to as your source file. Every Windows machine has a program called Notepad which can be used to edit source files. However, Notepad is a very rudimentary text file editor and is not recommended for daily use. The computers at DigiPen have a program called Notepad++, which is a much more powerful and capable text editor. This is the recommended editing tool for this class.