"Latch-Up,ESD,And Other Phenomena"

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Basic Electronics

14 Basic Electronics In this chapter, we lead you through a study of the basics of electronics. After completing the chapter, you should be able to Understand the physical structure of semiconductors. Understand the essence of the diode function. Understand the operation of diodes. Realize the applications of diodes and their use in the design of rectifiers. Understand the physical operation of bipolar junction transistors. Realize the applications of bipolar junction transistors. Understand the physical operation of field-effect transistors. Realize the application of field-effect transistors. Perform rapid analysis of transistor circuits. REFERENCES 1. Giorgio Rizzoni, Principles and Applications of Electrical Engineering, McGraw Hill, 2003. 2. J. R. Cogdel, Foundations of Electronics, Prentice Hall, 1999. 3. Donald A., Neaman, Electronic Circuit Analysis and Design, McGraw Hill, 2001. 4. Sedra/Smith, Microelectronic Circuits, Oxford, 1998. 1 Basic Electronics 2 14.1 INTRODUCTION Electronics is one of the most important fields in existence today. It has greatly influenced everything since early 1900s. Everyone nowadays realize the impact of electronics on our daily life. Table 14-1 shows many important areas with tremendous impact of electronics. Table 14-1 Various Application Areas of Electronics Area Examples of Applications Automotives Electronic ignition system, antiskid braking system, automatic suspension adjustment, performance optimization. Aerospace Airplane controls, spacecrafts, space missiles. Telecommunications Radio, television, telephones, mobile and cellular communications, satellite communications, military communications. Computers Personal computers, mainframe computers, supercomputers, calculators, microprocessors. Instrumentation Measurement equipment such as meters and oscilloscopes, medical equipment such as MRI, X- ray machines, etc. Microelectronics Microelectronic circuits, microelectromechanical systems. Power electronics Converters, Radar Air traffic control, security systems, military systems, police traffic radars. -

1999-2017 INDEX This Index Covers Tube Collector Through August 2017, the TCA "Data Cache" DVD- ROM Set, and the TCA Special Publications: No

1999-2017 INDEX This index covers Tube Collector through August 2017, the TCA "Data Cache" DVD- ROM set, and the TCA Special Publications: No. 1 Manhattan College Vacuum Tube Museum - List of Displays .........................1999 No. 2 Triodes in Radar: The Early VHF Era ...............................................................2000 No. 3 Auction Results ....................................................................................................2001 No. 4 A Tribute to George Clark, with audio CD ........................................................2002 No. 5 J. B. Johnson and the 224A CRT.........................................................................2003 No. 6 McCandless and the Audion, with audio CD......................................................2003 No. 7 AWA Tube Collector Group Fact Sheet, Vols. 1-6 ...........................................2004 No. 8 Vacuum Tubes in Telephone Work.....................................................................2004 No. 9 Origins of the Vacuum Tube, with audio CD.....................................................2005 No. 10 Early Tube Development at GE...........................................................................2005 No. 11 Thermionic Miscellany.........................................................................................2006 No. 12 RCA Master Tube Sales Plan, 1950....................................................................2006 No. 13 GE Tungar Bulb Data Manual................................................................. -

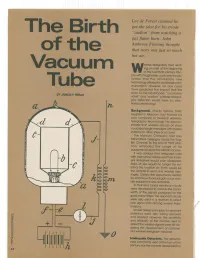

Lee De Forest Claimet\He Got the Idea for His Triode ''Audion" From

Lee de Forest claimet\he got the idea for his triode h ''audion" from wntching a gas flame bum. John Ambrose Flen#ng thought that story ·~just so much hot air. lreJess telegraphy held excit m WIng promise at the beginning of the twentieth century. Peo ~With Imagination could seethe po.. tentlal thot 'the rematkoble new technology offered forworlct1Nk:le com munfcotion. However, no one could hove predicted the impact that the soon-to-be-developed "osdllotlon volve" ond "oudlon" Wireless-telegra phy detector& wauid have on elec tronics technology. Backpouncl. Shortly before 1900, · Guglielmo Morconl had formed his own company to develop wireless telegraphy technology. He demon strated that wireless set-ups on ships eot~ld~messageswlth nearby stations on other ships or on land. t The Marconi Company hOd also j transmitted messages across the EhQ Jish Channel. By the end of 1901. Mar coni extended the range of his equipmenttospantheAtlan1tcOcean. It was obvlgus. 1hot ~raph ~MeS with subrhatlrie cables and ihelr lnber ent flmltations woUld soon disappear, Ships· at sea would no longer be iso la1ed. No locatlon on Eorth would. be too remote to send and receive mes sages. Clear1y; the opportunity existed tor enormous tiOOnciql gain once Jelio ble equlprrient was avoltable. To that end, 1Uned electrical circuits were developed to reduce the band width of the signals produced by ,the spark transrnlf'tirs. The resonont clfcults were also used in a receiver to select one signal from omong several trans missions. Slm~deslgn principles for resonont ontennas were also being explored and applied, However, the senstflvlty and reUabltlty of the devices used to ctetectthe Wireless signals were still hln cterlng the development of commer () cial wireless-telegraph nefWorks. -

History of Thethermionic Tube / Valve / Vacuum

History of theThermionic Tube / Valve / Vacuum Tube – Page 1 The following notes have been assembled by Phil (VK5SRP) from original material and material from several web sites, including Wikipedia for a class run at the North East Radio Club, South Australia January 2016. In electronics, a vacuum tube, an electron tube, or just a tube (North America), or valve (Britain and some other regions) is a device that controls electric current between electrodes in an evacuated container. Vacuum tubes mostly rely on thermionic emission of electrons from a hot filament or a cathode heated by the filament/heater. This type is called a thermionic tube or thermionic valve. A Photo-tube, however, achieves electron emission through the photoelectric effect. Not all electronic circuit valves/electron tubes are vacuum tubes (evacuated). Gas-filled tubes are similar devices containing a gas, typically at low pressure, which exploit phenomena related to electric discharge in gases, usually without a heater. Although thermionic emission was originally reported in 1873 by Frederick Guthrie, it was Thomas Edison's 1883 investigation that spurred future research, the phenomenon thus becoming known as the "Edison effect". Edison patented what he found, but he did not understand the underlying physics, nor did he have an inkling of the potential value of the discovery. It wasn't until the early 20th century that the rectifying property of such a device was utilised, most notably by John Ambrose Fleming, who used the Diode tube to detect (demodulate) radio signals. Lee De Forest's 1906 "Audion" was also developed as a radio detector, and soon led to the development of the Triode tube. -

The Venerable Triode

The Venerable Triode The very first gain device, the vacuum tube Triode, is still made after more than a hundred years, and while it has been largely replaced by other tubes and the many transistor types, it still remains popular in special industry and audio applications. I have some thoughts on why the Triode remains special for audio amplifiers (apart from sentimental value) that I would like to share. But first, a quick tutorial about Triodes: The earliest Triode was Lee De Forest's 1906 “Audion”. Over a hundred years development has resulted in many Triodes, large and small. The basic design has remained much the same. An evacuated container, usually glass, holds three signal connections, seen in the drawing as the Cathode, Grid and Plate (the Plate is also referred to as the Anode). In addition you see an internal heater, similar to a light bulb filament, which is used to heat the Cathode. Triode operation is simple. Electrons have what's known as “negative electrostatic charge”, and it is understood that “like” charges physically repel each other while opposite charges attract. The Plate is positively charged relative to the Cathode by a battery or other voltage source, and the electrons in the Cathode are attracted to the Plate, but are prevented by a natural tendency to hang out inside the Cathode and avoid the vacuum. This is where the heater comes in. When you make the Cathode very hot, these electrons start jumping around, and many of them have enough energy to leave the surface of the Cathode. -

Silver Service ORIGIN Driver Tubes Have Coloured Stickers, Path

AUDION SILVER NIGHT SPECIAL EDITION AUDION SILVER NIGHT SPECIAL EDITION EXOTICA INTEGRATED VALVE AMPLIFIER £4,150 INTEGRATED VALVE AMPLIFIER £4,150 EXOTICA The Silver Night warmth somehow feels more natural to mean-spiritedness and is overcome Special Edition and is accompanied with masses of by using better and thicker silver has attractive airy detail that is highly extended wiring – as I suspect is the case here. designer lines yet very sweet and free from grain, My appetite is whetted so I play the all placed in a wonderfully inky black Bass With Chorus Aria – Eilt, Ihr and silent backdrop. Angefochtnen Seelen from JS Bach’s St Playing Lorde’s Royals on vinyl via my John Passion conducted by Karl Richter Timestep T-01 MC phono stage (HFC on HDCD. 371) is surprising. This track has really I am now better prepared for my deep bass and I’m expecting the Special expectations to be exceeded. Large Edition Silver Night to stumble, but I’m flowing introductory sweeps of the actually the one that’s wrong-footed. orchestra have excellent breadth Bass is deep and far faster than this and tone and the bass vocal rises design has any right to deliver. A single- majestically with real authority and ended 300B amplifier should, by rights luscious body and weight. The struggle here, but this performance has orchestra doesn’t have massive weight, rasp and plenty of taut bass front-to-back depth, but this criticism detail that doesn’t slouch behind the seems churlish, as this rendition is way higher octaves. -

Frequency Characteristics of the Electron-Tube Oscillation Generator

FREQUENCY CHARACTERISTICS OF THE ELECTRON—TUBE OSCILLATION GENERATOR BY RAY STUART QUICK B. S. University of California, 1916 THESIS Submitted in Partial Fulfillment of the Requirements for the Degree of MASTER OF SCIENCE IN ELECTRICAL ENGINEERING IN THE GRADUATE SCHOOL OF THE! UNIVERSITY OF ILLINOIS 1919 UNIVERSITY OF ILLINOIS THE GRADUATE SCHOOL I HEREBY RECOMMEND THAT THE THESIS PREPARED UNDER MY SUPERVISION BY Hay Stuart 4uick ENTITLED Jgraqstaney Character i st.i cs of the Electron-Tube Oscillation Generator BE ACCEPTED AS FULFILLING THIS PART OF THE REQUIREMENTS FOR THE DEGREE OF Master of Snionoe in Eleotri nol Engin eering . \Mm Head of Department Recommendation concurred in :! Committee on Final Examination* *Required for doctor's degree but not for master's 1 CONTENTS I INTRODUCTION Page 1. Scope of work 2 2. Historical review. 2 II THEORETICAL DISCUSSION OP PROBLEM 1. General principles of operation. 4 2. Circuits used. 6 3. Work of previous investigators. 6 4. Mathematical solution of circuits. 8 III APPARATUS AND METHODS 1. Electron- tubes used. 13 2. Circuit properties. 13 3. Frenuency determinations. 13 IV DATA AND EXPERIMENTAL RESULTS 1. Observed conditions necessary for constant eurrent and for oscillating eurrent. 36 2. Oscillograms. 36 3. Experimental results. 37 V CONCLUSIONS 1. Comparison of experimental ^nd theoretical results. 45 2. Suggestions as to future work 45 VI BIBLIOGRAPHY 47 2 I INTRODUCTIOU 1. Scope of Work. The development of the electron- tube ( also called three-electrode vacuum tube, vacuum- tube, thermionic amplifier, audion, etc. ) has brought to light many new and interest- ing problems. In using the tube as a source of continuous oscilla- tions it is desirable to be able to predetermine the frequency, wave-form and amplitude characteristics. -

1999-2018 INDEX This Index Covers Tube Collector Through August 2018, the TCA "Data Cache" DVD- ROM Set, and the Following TCA Special Publications: No

1999-2018 INDEX This index covers Tube Collector through August 2018, the TCA "Data Cache" DVD- ROM set, and the following TCA Special Publications: No. 1 Manhattan College Vacuum Tube Museum - List of Displays .........................1999 No. 2 Triodes in Radar: The Early VHF Era ...............................................................2000 No. 3 Auction Results ....................................................................................................2001 No. 4 A Tribute to George Clark, with audio CD ........................................................2002 No. 5 J. B. Johnson and the 224A CRT.........................................................................2003 No. 6 McCandless and the Audion, with audio CD......................................................2003 No. 7 AWA Tube Collector Group Fact Sheet, Vols. 1-6 ...........................................2004 No. 8 Vacuum Tubes in Telephone Work.....................................................................2004 No. 9 Origins of the Vacuum Tube, with audio CD.....................................................2005 No. 10 Early Tube Development at GE...........................................................................2005 No. 11 Thermionic Miscellany.........................................................................................2006 No. 12 RCA Master Tube Sales Plan, 1950....................................................................2006 No. 13 GE Tungar Bulb Data Manual................................................................. -

1999-2019 INDEX This Index Covers Tube Collector Through April 2019, the TCA "Data Cache" DVD-ROM Set, and the Following TCA Special Publications: No

1999-2019 INDEX This index covers Tube Collector through April 2019, the TCA "Data Cache" DVD-ROM set, and the following TCA Special Publications: No. 1 Manhattan College Vacuum Tube Museum - List of Displays .........................1999 No. 2 Triodes in Radar: The Early VHF Era ...............................................................2000 No. 3 Auction Results ....................................................................................................2001 No. 4 A Tribute to George Clark, with audio CD ........................................................2002 No. 5 J. B. Johnson and the 224A CRT.........................................................................2003 No. 6 McCandless and the Audion, with audio CD......................................................2003 No. 7 AWA Tube Collector Group Fact Sheet, Vols. 1-6 ...........................................2004 No. 8 Vacuum Tubes in Telephone Work.....................................................................2004 No. 9 Origins of the Vacuum Tube, with audio CD.....................................................2005 No. 10 Early Tube Development at GE...........................................................................2005 No. 11 Thermionic Miscellany.........................................................................................2006 No. 12 RCA Master Tube Sales Plan, 1950....................................................................2006 No. 13 GE Tungar Bulb Data Manual................................................................. -

Birth of the Valve.Indd 68 25/01/2019 08:21 Attention to the Problem of Developing an Eff Cient Receiving Detector

Feature by Dr Bruce Taylor HB9ANY ● E-mail: [email protected] Birth of the Thermionic Valve n the archives of Marconi’s Dr Bruce Taylor HB9ANY relates how chance, ingenuity Wireless Telegraph Company and confl ict created the technology that dominated radio for November 1904, there is a handwritten letter that communication for half a century. concludes: “I have not mentioned Ithis to anyone yet, as it may become useful”. The letter is signed by the English scientist John Ambrose Fleming and it describes how he had found a method of detecting oscillatory electrical currents in an antenna using a thermionic valve. “It may become useful” was perhaps the understatement of the century! While the saga of the thermionic valve had a large cast, the two principal roles were initially played by Fleming and the American experimenter Lee de Forest. The characters of these two men could hardly have been more different. De Forest was an enterprising inventor but a f amboyant showman unashamedly motivated by a desire for fame, fortune and a luxurious life style. He was lucky in his discoveries, but not in his private life or his somewhat unethical business practices, and he died in 1961 without achieving the f nancial success of which he dreamed. Fleming, on the other hand, was the careful archetypal physicist, methodical in his investigations and A 1915 advertisement by Elmer Cunningham explains that, unlike the de Forest Audion, his AudioTron motivated to earn the esteem and can be bought alone. recognition of his peers for advancing scientif c knowledge. He achieved his aim, he patented the device as a means for The Fleming Diode and was knighted in 1929, but he wasn’t controlling mains voltage but made no In 1899, Fleming had been appointed interested in vigorously exploiting his mention of its rectifying properties, for he scientif c advisor to Marconi and became discoveries and left Marconi and others was promoting DC rather than AC power responsible for the design of part of the to prof t from their commercialisation. -

The Jersey Broadcaster

The Jersey Broadcaster NEWSLETTER OF THE NEW JERSEY ANTIQUE RADIO CLUB September 2014 Volume 20 Issue 9 MEETING/ MEETING NOTICE ACTIVITY NOTES The next NJARC meeting will take place on Friday, September 12th at 7:30 PM at InfoAge. Directions may be found at the club’s website (http://njarc.org). This month, the club will be treated to a presentation from member John Dilks, K2TQN, which he has titled “Old Transmissions and Voices from the Past.” Reported by This talk was the highlight of the ARRL National Centennial Convention in Marv Beeferman Hartford and the AWA Convention in Rochester. (More on John’s talk below.) We’ll also be auctioning off some more of Dave Sica’s “book haul” (see page 4 The ON-LINE Broadcaster of this month’s Broadcaster.) The New Jersey Broadcaster is now on -line. To date, over 120 of your fellow NJARC members have subscribed, have “cherry picked” their auction wins! waukee. Bob’s museum contains over saving the club and your editor a sig- We are not meeting at the Englishtown 1,000 microphones plus desk and floor nificant amount of money and work. Flea Market. The NJARC is so fortunate stands, microphone enclosures, transform- Interested? Send your e-mail address to have Professor Michael Littman as a ers, preamplifiers and test equipment. to [email protected]. Be sure member, enabling us to meet at prestig- Included are three displays to show the to include your full name. ious Princeton University. We need to service and re-building process of the ear- always make ourselves welcome by re- ly carbon and condenser microphones specting the rules of the facility by re- along with the special apparatus used. -

"Lessons in Electric Circuits, Volume III -- Semiconductors"

Fifth Edition, last update March 29, 2009 2 Lessons In Electric Circuits, Volume III – Semiconductors By Tony R. Kuphaldt Fifth Edition, last update March 29, 2009 i c 2000-2012, Tony R. Kuphaldt This book is published under the terms and conditions of the Design Science License. These terms and conditions allow for free copying, distribution, and/or modification of this document by the general public. The full Design Science License text is included in the last chapter. As an open and collaboratively developed text, this book is distributed in the hope that it will be useful, but WITHOUT ANY WARRANTY; without even the implied warranty of MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the Design Science License for more details. Available in its entirety as part of the Open Book Project collection at: openbookproject.net/electricCircuits PRINTING HISTORY • First Edition: Printed in June of 2000. Plain-ASCII illustrations for universal computer readability. • Second Edition: Printed in September of 2000. Illustrations reworked in standard graphic (eps and jpeg) format. Source files translated to Texinfo format for easy online and printed publication. • Third Edition: Printed in January 2002. Source files translated to SubML format. SubML is a simple markup language designed to easily convert to other markups like LATEX, HTML, or DocBook using nothing but search-and-replace substitutions. • Fourth Edition: Printed in December 2002. New sections added, and error corrections made, since third edition. • Fith Edition: Printed in July 2007. New sections added, and error corrections made, format change. ii Contents 1 AMPLIFIERS AND ACTIVE DEVICES 1 1.1 From electric to electronic ...............................