Radio Frequency Transistors : Principles and Practical 21 Applications / Norman Dye, Helge Granberg.—2Nd Ed

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Maintenance of Remote Communication Facility (Rcf)

ORDER rlll,, J MAINTENANCE OF REMOTE commucf~TIoN FACILITY (RCF) EQUIPMENTS OCTOBER 16, 1989 U.S. DEPARTMENT OF TRANSPORTATION FEDERAL AVIATION AbMINISTRATION Distribution: Selected Airway Facilities Field Initiated By: ASM- 156 and Regional Offices, ZAF-600 10/16/89 6580.5 FOREWORD 1. PURPOSE. direction authorized by the Systems Maintenance Service. This handbook provides guidance and prescribes techni- Referenceslocated in the chapters of this handbook entitled cal standardsand tolerances,and proceduresapplicable to the Standardsand Tolerances,Periodic Maintenance, and Main- maintenance and inspection of remote communication tenance Procedures shall indicate to the user whether this facility (RCF) equipment. It also provides information on handbook and/or the equipment instruction books shall be special methodsand techniquesthat will enablemaintenance consulted for a particular standard,key inspection element or personnel to achieve optimum performancefrom the equip- performance parameter, performance check, maintenance ment. This information augmentsinformation available in in- task, or maintenanceprocedure. struction books and other handbooks, and complements b. Order 6032.1A, Modifications to Ground Facilities, Order 6000.15A, General Maintenance Handbook for Air- Systems,and Equipment in the National Airspace System, way Facilities. contains comprehensivepolicy and direction concerning the development, authorization, implementation, and recording 2. DISTRIBUTION. of modifications to facilities, systems,andequipment in com- This directive is distributed to selectedoffices and services missioned status. It supersedesall instructions published in within Washington headquarters,the FAA Technical Center, earlier editions of maintenance technical handbooksand re- the Mike Monroney Aeronautical Center, regional Airway lated directives . Facilities divisions, and Airway Facilities field offices having the following facilities/equipment: AFSS, ARTCC, ATCT, 6. FORMS LISTING. EARTS, FSS, MAPS, RAPCO, TRACO, IFST, RCAG, RCO, RTR, and SSO. -

Citizens' Band (CB) Radio Spectrum Use – Information and Operation

Citizens’ Band Radio equipment– information and operation Citizens’ Band (CB) radio spectrum use – information and operation Of 364 Guidance Publication date: March 2018 Citizens’ Band Radio equipment– information and operation Contents Section Page 1 Regulatory and equipment information 1 2 Frequently asked questions 5 3 CB operating practice 8 Citizens’ Band Radio equipment– information and operation Section 1 Regulatory and equipment information Citizens’ Band (‘CB’) radio 1.1 Citizens’ Band (‘CB’) radio operates in the 27 MHz band. It is a short-range radio service for both hobby and business use. It is designed to be used without the need for technical qualifications. However, its use must not cause interference to other radio users. Consequently, only radios meeting certain specific requirements may be used. These are described below. How Ofcom authorises the use of CB radio 1.2 Ofcom seeks to reduce regulation, where possible. In 2006, we therefore made exemption regulations1, removing the need for a person to hold a licence to operate CB radio equipment using Angle Modulation (FM/PM). 1.3 In 2014, Ofcom made further exemption regulations2, which permitted the operation of CB radio equipment using two additional modes of Amplitude Modulation (AM) - Double Side Band (DSB) and Single Side Band (SSB). This followed an international agreement3 made in 2011.”. 1.4 CB users share spectrum in a frequency band used by the Ministry of Defence (MOD). CB users must therefore accept incoming interference caused by use of this spectrum by the MOD. 1.5 CB radio equipment must be operated on a 'non-interference’ basis. -

Recommendation ITU-R V.573-4

Rec. ITU-R V.573-5 1 RECOMMENDATION ITU-R V.573-5* Radiocommunication vocabulary (1978-1982-1986-1990-2000-2007) Scope This Recommendation provides the main vocabulary reference, giving synonymous terms in three languages and the associated definitions. It includes terms given in Article 1 of the Radio Regulations (RR) and extends the list to technical terms defined in texts of the ITU-R. The ITU Radiocommunication Assembly, considering a) that Article 1 of the Radio Regulations (RR) contains the definitions of terms for regulatory purposes; b) that the Radiocommunication Study Groups have a need to establish new and amended definitions for technical terms that do not appear in RR Article 1 or that are so defined as to be unsuitable for Radiocommunication Study Group purposes; c) that it would be desirable for some of these terms and definitions established by the Radiocommunication Study Groups to be more widely used within the ITU-R, recommends that the terms listed in RR Article 1 and in Annex 1 below should be used as far as possible with the meaning ascribed to them in the corresponding definition. NOTE 1 – Study Groups are invited, where there is a difficulty in using any of the terms with the meaning given in the corresponding definition, to forward to the Coordination Committee for Vocabulary (CCV) a proposal for revision or alternative application, accompanied by substantiating argument. NOTE 2 – A number of terms in this Recommendation appear also in RR Article 1 with a different definition. These terms are identified by (RR . ., MOD) or (RR . .(MOD)) if the modifications consist only of editorial changes. -

Amateur Radio Notes

Ham Radio – General Exam – Study Notes Frequency: 300/meter = MHz or 300/MHz = meters Dipole Antenna: ½ Wave dipole antennas = 468/Frequency Silicon – Seven letters = diode threshold of .07v Geranium – 3x3 letters = diode threshold of .03v NAND and ZERO both four letters QRQ = Quicker QRS = Slower QRV = ReceiVe CapACitors pass AC inDuCtors pass DC Fifteen amp fuse for Fourteen gauge wire Twenty amp fuse for Twelve gauge wire AC frequencies increases: – Coil springs higher (reactance increases) - Capacitor holds back (reactance decreases) AM – Product Detector Audio – Discriminator BFO – Product Detector Heterodyne receiver - Mixer Balanced Modulator + Mixer - Filter 20m Data band – 14.070 – 14.100 LC Oscillator – Tank Circuit CW Bandwidth = 150 Hz SBB Bandwidth = 2,300 Hz FM Bandwidth = +/- 5KHz or +/- 15 KHz Ohm’s Law: E/I*R Unit Measures Power Law: P/E*I Amp Current E – Voltage in Volts Farad Capacitance I – Current in Amps Henry Inductance R – Resistance in Ohms Hertz Frequency P – Power in Watts Ohm Resistance Series Parallel Watt Power Resistor Add Less Volt Voltage Inductor Add Less Capacitor Less Add Designation Frequency Wavelength ELF extremely low frequency 3Hz to 30Hz 100'000km to 10'000 km SLF superlow frequency 30Hz to 300Hz 10'000km to 1'000km ULF ultralow frequency 300Hz to 3000Hz 1'000km to 100km VLF very low frequency 3kHz to 30kHz 100km to 10km LF low frequency 30kHz to 300kHz 10km to 1km MF medium frequency 300kHz to 3000kHz 1km to 100m HF high frequency 3MHz to 30MHz 100m to 10m VHF very high frequency 30MHz to 300MHz -

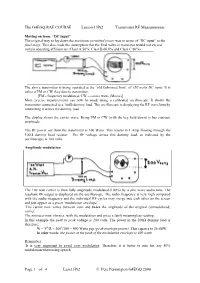

DC Input” the Original Way to Lay Down the Maximum Permitted Power Was in Terms of “DC Input” to the Final Stage

The G4EGQ RAE COURSE Lesson 13Pt2 Transmitter RF Measurements Moving on from “DC input” The original way to lay down the maximum permitted power was in terms of “DC input” to the final stage. This also made the assumption that the final valve or transistor would not exceed certain operating efficiencies (Class A 50%; Class B 66.6% and Class C 80%) The above transmitter is being operated at the “old fashioned limit” of 150 watts DC input. It is either a FM or CW (key down) transmitter. [FM= frequency modulated; CW = carrier wave (Morse)] More precise measurements can now be made using a calibrated oscilloscope. It shows the transmitter connected to a 100Ω dummy load. The oscilloscope is displaying the RF waveform by connecting it across the dummy load. The display shows the carrier wave. Being FM or CW (with the key held down) is has constant amplitude. The RF power out from the transmitter is 100 Watts. This results in 1 Amp flowing through the 100Ω dummy load resistor. The RF voltage across this dummy load, as indicated by the oscilloscope, is 100 volts. Amplitude modulation The 100 watt carrier is then fully amplitude modulated.(100%) by a sine wave audio tone. The resultant RF output is displayed on the oscilloscope. The radio frequency is very high compared with the audio frequency and the individual RF cycles may merge into each other on the screen and just appear as a green “modulation envelope”. The carrier now varies between zero and twice the amplitude of the original (unmodulated) carrier. -

The Crest Factor in DVB-T (OFDM) Transmitter Systems and Its Influence on the Dimensioning of Power Components

® ® ® ® ® ® Products: R&S NV7000, R&S NV7001, R&S NV8200, R&S SV7000, R&S SV7002, R&S SV8000 ® ® ® DTV transmitters, R&S EFA, R&S FSP, R&S FSU test instruments The Crest Factor in DVB-T (OFDM) Transmitter Systems and its Influence on the Dimensioning of Power Components Application Note 7TS02 Are there really power peaks that are 20 dB above the average value? Yes, there are. Ever since the intro- duction of digital transmission technology, it has been necessary to deal with such orders of magnitude. RF power components must be suitably dimensioned to handle the expected voltage peaks and avoid break- ing down. If we can determine the crest factor, i.e. the ratio of the peak value to the average or RMS value, with sufficient accuracy (even though it can only be assessed statistically), then we will have solved the question of dimensioning power components. This Application Note is intended to help with this problem by providing some useful insights including basic formulas, some statistical background and a practical look at the limiting factors when it comes to dealing with real transmitter systems. Subject to change – Bernhard Kaehs, January 2007 – 7TS02_2E Introduction Contents 1 Introduction ............................................................................................. 2 2 Determination and Usage of the Crest Factor ........................................ 3 The crest factor of a modulated RF signal......................................... 3 Crest factor for multiple superimposed signals.................................. 5 Crest factor measurement ................................................................. 6 Output signal from a DVB-T transmitter............................................. 9 Output bandpass.............................................................................. 11 Interconnection of multiple transmitters on an antenna................... 12 3 The Crest Factor During Generation of a DVB-T Signal ..................... -

Federal Communications Commission § 2.1047

Pt. 1, App. C 47 CFR Ch. I (10–1–20 Edition) 4. Request from the Applicant a summary application of this Nationwide Agreement of the steps taken to comply with the re- within a State or with regard to the review quirements of Section 106 as set forth in this of individual Undertakings covered or ex- Nationwide Agreement, particularly the ap- cluded under the terms of this Agreement. plication of the Criteria of Adverse Effect; Comments related to telecommunications 5. Request from the Applicant copies of activities shall be directed to the Wireless any documents regarding the planning or Telecommunications Bureau and those re- construction of the Facility, including cor- lated to broadcast facilities to the Media Bu- respondence, memoranda, and agreements; reau. The Commission will consider public 6. If the Facility was constructed prior to comments and following consultation with full compliance with the requirements of the SHPO/THPO, potentially affected Indian Section 106, request from the Applicant an tribes and NHOs, or Council, where appro- explanation for such failure, and possible priate, take appropriate actions. The Com- measures that can be taken to mitigate any mission shall notify the objector of the out- resulting adverse effects on Historic Prop- come of its actions. erties. D. If the Commission concludes that there XII. AMENDMENTS is a probable violation of Section 110(k) (i.e., The signatories may propose modifications that ‘‘with intent to avoid the requirements or other amendments to this Nationwide of Section 106, [an Applicant] has inten- Agreement. Any amendment to this Agree- tionally significantly adversely affected a ment shall be subject to appropriate public Historic Property’’), the Commission shall notice and comment and shall be signed by notify the Applicant and forward a copy of the Commission, the Council, and the Con- the documentation set forth in Section X.C. -

Advanced Course Ch. 9 Transmitters De VE1FA, 2019

Advanced Course Ch. 9 Transmitters de VE1FA, 2019 1915 1929 1952 1990s Untangling RF power terms Carrier power = PEP (peak envelope power) = average power in steady carrier modes, like CW, FM, FSK, RTTY, JT-9, JT-65, but not in varying carrier modes like AM and SSB. RMS power = 0.707 of PEP in steady carrier modes RMS watts = DC power watts = “power company watts” PEP: highest envelope power supplied to Z-matched TX-line delivering complete undistorted cycles. PEP in 100% modulated AM (DSB + carrier) = 4 x average power PEP in SSB = 3-10 x average power (varies with ALC, mic used, and voice) Current Canadian Amateur Transmitter Power Regulations RBR-4, Issue 2, 22 January, 2014 10. Restrictions on Capacity and Power Output The transmitting power of an amplifier installed in an amateur station shall not be capable of exceeding by more than 3 dB the transmitting power limits described in this section. 10.1 Amateur Radio Operator Certificate with Basic Qualification The holder of an Amateur Radio Certificate with Basic Qualification is limited to a maximum transmitting power of: (a) where expressed as direct current power, 250W to the anode or collector circuit of the transmitter stage that supplies radio frequency energy to the antenna; or (b) where expressed as radio frequency output power measured across an impedance-matched load, (i) 560W peak envelope power for transmitters that produce any type of single sideband emission, or (ii) 190W carrier power for transmitters that produce any other type of emission. 10.2 Amateur Radio Operator -

EN 302 288-1 V1.1.1 (2004-03) European Standard (Telecommunications Series)

Draft ETSI EN 302 288-1 V1.1.1 (2004-03) European Standard (Telecommunications series) Electromagnetic compatibility and Radio spectrum Matters (ERM); Short Range Devices; Road Transport and Traffic Telematics (RTTT); Short range radar equipment operating in the 24 GHz range; Part 1: Technical requirements and methods of measurement 2 Draft ETSI EN 302 288-1 V1.1.1 (2004-03) Reference DEN/ERM-TG31B-002-1 Keywords radar, radio, testing, SRD, RTTT ETSI 650 Route des Lucioles F-06921 Sophia Antipolis Cedex - FRANCE Tel.: +33 4 92 94 42 00 Fax: +33 4 93 65 47 16 Siret N° 348 623 562 00017 - NAF 742 C Association à but non lucratif enregistrée à la Sous-Préfecture de Grasse (06) N° 7803/88 Important notice Individual copies of the present document can be downloaded from: http://www.etsi.org The present document may be made available in more than one electronic version or in print. In any case of existing or perceived difference in contents between such versions, the reference version is the Portable Document Format (PDF). In case of dispute, the reference shall be the printing on ETSI printers of the PDF version kept on a specific network drive within ETSI Secretariat. Users of the present document should be aware that the document may be subject to revision or change of status. Information on the current status of this and other ETSI documents is available at http://portal.etsi.org/tb/status/status.asp If you find errors in the present document, send your comment to: [email protected] Copyright Notification No part may be reproduced except as authorized by written permission. -

April 27, 2017 * This Document Is Being Released As Part of a "Permit-But-Disclose" Proceeding. Any Presentations Or V

April 27, 2017 FCC FACT SHEET* Part 95 Personal Radio Service Reform Report and Order - WT Docket No. 10-119 Background: The Commission’s Part 95 Personal Radio Services (PRS) rules address a wide variety of wireless devices that are used by the general public to satisfy personal communications needs. These devices generally use low-power transmitters, communicate over shared radio frequencies, and (with a few exceptions) do not require an individual FCC license for each user. Some common examples of PRS devices include walkie-talkies; radio control toy cars, boats, and planes; hearing assistance devices; CB radios; medical implant devices; and Personal Locator Beacons. This draft Report and Order completes a thorough review of the PRS rules in order to modernize them, remove outdated requirements, and reorganize them to make it easier to find information. As a result of this effort, the rules will become consistent, clear, and concise. What the Rules Would Do: GMRS/FRS Reform. General Mobile Radio Service (GMRS) and Family Radio Service (FRS) devices are both used for personal communications over several miles. The public may be most familiar with FRS walkie-talkies. While GMRS and FRS share spectrum, GMRS provides for greater communications range and requires an FCC license, while FRS does not require a license. The rules will increase the number of communications channels for both GMRS and FRS, expand digital capabilities to GMRS (currently allowed for FRS), and increase the power/range for certain FRS channels to meet consumer demands for longer range communications (while maintaining higher power capabilities for licensed GMRS). -

Draft ETSI EN 301 489-15 V2.1.0 (2016-04)

Draft ETSI EN 301 489-15 V2.1.0 (2016-04) HARMONISED EUROPEAN STANDARD ElectroMagnetic Compatibility (EMC) standard for radio equipment and services; Part 15: Specific conditions for commercially available amateur radio equipment; Harmonised Standard covering the essential requirements of article 3.1(b) of the Directive 2014/53/EU 2 Draft ETSI EN 301 489-15 V2.1.0 (2016-04) Reference REN/ERM-EMC-344 Keywords amateur, EMC, Harmonised standard, radio ETSI 650 Route des Lucioles F-06921 Sophia Antipolis Cedex - FRANCE Tel.: +33 4 92 94 42 00 Fax: +33 4 93 65 47 16 Siret N° 348 623 562 00017 - NAF 742 C Association à but non lucratif enregistrée à la Sous-Préfecture de Grasse (06) N° 7803/88 Important notice The present document can be downloaded from: http://www.etsi.org/standards-search The present document may be made available in electronic versions and/or in print. The content of any electronic and/or print versions of the present document shall not be modified without the prior written authorization of ETSI. In case of any existing or perceived difference in contents between such versions and/or in print, the only prevailing document is the print of the Portable Document Format (PDF) version kept on a specific network drive within ETSI Secretariat. Users of the present document should be aware that the document may be subject to revision or change of status. Information on the current status of this and other ETSI documents is available at https://portal.etsi.org/TB/ETSIDeliverableStatus.aspx If you find errors in the present document, please send your comment to one of the following services: https://portal.etsi.org/People/CommiteeSupportStaff.aspx Copyright Notification No part may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm except as authorized by written permission of ETSI. -

Swiss National Frequency Allocation Plan and Specific Assignments

Federal Department of the Environment Transport, Energy, and Communication DETEC Federal Office of Communications OFCOM Licenses and Frequency Management / Frequency Planning Swiss National Frequency Allocation Plan and Specific Assignments Edition 2021 Publisher: Federal Office of Communications OFCOM Licenses and Frequency Management / Frequency Planning Zukunftstrasse 44 CH - 2501 Biel – Bienne Switzerland http://www.bakom.ch https://www.bakom.admin.ch/bakom/en/homepage/frequencies-and-antennas/national- frequency-allocation-plan.html © OFCOM Switzerland / Issue January 1st 2021 Date: 29.10.2020 / © OFCOM Switzerland / Issue January 1st 2021 Page 2 of 195 Contents 1 Introduction .......................................................................... 5 2 Principles of spectrum management ................................. 6 2.1 National level ............................................................................................................ 6 2.2 International level ...................................................................................................... 6 3 Explanatory notes to the frequency allocation plan ........ 8 4 Frequency Allocation plan ................................................ 11 5 Annexes and Appendices ............................................... 130 5.1 Annex 1: List of frequency bands for UWB and Wideband SRD applications ....... 130 5.2 Annex 2: List of specific assignments ................................................................... 132 5.3 Annex 3: List of technical interface