An Embedded Hybrid-Memory-Aware Virtualization Layer for Chip-Multiprocessors

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Memory Map: 68HC12 CPU and MC9S12DP256B Evaluation Board

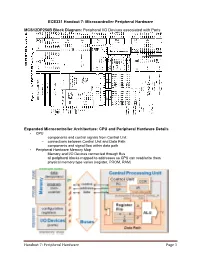

ECE331 Handout 7: Microcontroller Peripheral Hardware MCS12DP256B Block Diagram: Peripheral I/O Devices associated with Ports Expanded Microcontroller Architecture: CPU and Peripheral Hardware Details • CPU – components and control signals from Control Unit – connections between Control Unit and Data Path – components and signal flow within data path • Peripheral Hardware Memory Map – Memory and I/O Devices connected through Bus – all peripheral blocks mapped to addresses so CPU can read/write them – physical memory type varies (register, PROM, RAM) Handout 7: Peripheral Hardware Page 1 Memory Map: 68HCS12 CPU and MC9S12DP256B Evaluation Board Configuration Register Set Physical Memory Handout 7: Peripheral Hardware Page 2 Handout 7: Peripheral Hardware Page 3 HCS12 Modes of Operation MODC MODB MODA Mode Port A Port B 0 0 0 special single chip G.P. I/O G.P. I/O special expanded 0 0 1 narrow Addr/Data Addr 0 1 0 special peripheral Addr/Data Addr/Data 0 1 1 special expanded wide Addr/Data Addr/Data 1 0 0 normal single chip G.P. I/O G.P. I/O normal expanded 1 0 1 narrow Addr/Data Addr 1 1 0 reserved -- -- 1 1 1 normal expanded wide Addr/Data Addr/Data G.P. = general purpose HCS12 Ports for Expanded Modes Handout 7: Peripheral Hardware Page 4 Memory Basics •RAM: Random Access Memory – historically defined as memory array with individual bit access – refers to memory with both Read and Write capabilities •ROM: Read Only Memory – no capabilities for “online” memory Write operations – Write typically requires high voltages or erasing by UV light • Volatility of Memory – volatile memory loses data over time or when power is removed • RAM is volatile – non-volatile memory stores date even when power is removed • ROM is no n-vltilvolatile • Static vs. -

User Guide Commplete 4000 Single Board Computer (IPC-623C) User Guide S000277A Revision a All Rights Reserved

MultiTech Model IPC-623C Single Board Computer for CommPlete 4000 Server User Guide CommPlete 4000 Single Board Computer (IPC-623C) User Guide S000277A Revision A All rights reserved. This publication may not be reproduced, in whole or in part, without prior expressed written permission from Multi-Tech Systems, Inc. All rights reserved. Copyright © 2002 by Multi-Tech Systems, Inc. Multi-Tech Systems, Inc. makes no representation or warranties with respect to the contents hereof and specifically disclaims any implied warranties of merchantability or fitness for any particular purpose. Furthermore, Multi-Tech Systems, Inc. reserves the right to revise this publication and to make changes from time to time in the content hereof without obligation of Multi-Tech Systems, Inc., to notify any person or organization of such revisions or changes. Record of Revisions Revision Description A Manual released (08/12/02). Patents This product is covered by one or more of the following U.S. Patent Numbers: 5.301.274, 5.309.562, 5.355.365, 5.355.653, 5.452.289, 5.453.986. Other patents Pending. Trademarks The Multi-Tech logo is a registered trademark of Multi-Tech Systems, Inc. NetWare is a registered trademark of Novell, Inc. Pentium is a registered trademark of Intel Corporation. SCO is a registered trademark of Santa Cruz Operation, Inc. UNIX is a registered trademark of X/Open Company, Ltd. Windows 95 and Windows NT are registered trademarks of Microsoft. Multi-Tech Systems, Inc. 2205 Woodale Drive Mounds View, Minnesota 55112 (763) 785-3500 or (800) 328-9717 Fax (763) 785-9874 Tech Support (800) 972-2439 Internet Address: http://www.multitech.com Table of Contents Contents Chapter 1 - Introduction ............................................................... -

Memory Mapping and DMA

,ch15.13676 Page 412 Friday, January 21, 2005 11:04 AM CHAPTER 15 Chapter 15 Memory Mapping and DMA This chapter delves into the area of Linux memory management, with an emphasis on techniques that are useful to the device driver writer. Many types of driver pro- gramming require some understanding of how the virtual memory subsystem works; the material we cover in this chapter comes in handy more than once as we get into some of the more complex and performance-critical subsystems. The virtual mem- ory subsystem is also a highly interesting part of the core Linux kernel and, there- fore, it merits a look. The material in this chapter is divided into three sections: • The first covers the implementation of the mmap system call, which allows the mapping of device memory directly into a user process’s address space. Not all devices require mmap support, but, for some, mapping device memory can yield significant performance improvements. • We then look at crossing the boundary from the other direction with a discus- sion of direct access to user-space pages. Relatively few drivers need this capabil- ity; in many cases, the kernel performs this sort of mapping without the driver even being aware of it. But an awareness of how to map user-space memory into the kernel (with get_user_pages) can be useful. • The final section covers direct memory access (DMA) I/O operations, which pro- vide peripherals with direct access to system memory. Of course, all of these techniques require an understanding of how Linux memory management works, so we start with an overview of that subsystem. -

Virtual Memory and Linux

Virtual Memory and Linux Matt Porter Embedded Linux Conference Europe October 13, 2016 About the original author, Alan Ott ● Unfortunately, he is unable to be here at ELCE 2016. ● Veteran embedded systems and Linux developer ● Linux Architect at SoftIron – 64-bit ARM servers and data center appliances – Hardware company, strong on software – Overdrive 3000, more products in process Physical Memory Single Address Space ● Simple systems have a single address space ● Memory and peripherals share – Memory is mapped to one part – Peripherals are mapped to another ● All processes and OS share the same memory space – No memory protection! – Processes can stomp one another – User space can stomp kernel mem! Single Address Space ● CPUs with single address space ● 8086-80206 ● ARM Cortex-M ● 8- and 16-bit PIC ● AVR ● SH-1, SH-2 ● Most 8- and 16-bit systems x86 Physical Memory Map ● Lots of Legacy ● RAM is split (DOS Area and Extended) ● Hardware mapped between RAM areas. ● High and Extended accessed differently Limitations ● Portable C programs expect flat memory ● Multiple memory access methods limit portability ● Management is tricky ● Need to know or detect total RAM ● Need to keep processes separated ● No protection ● Rogue programs can corrupt the entire system Virtual Memory What is Virtual Memory? ● Virtual Memory is a system that uses an address mapping ● Maps virtual address space to physical address space – Maps virtual addresses to physical RAM – Maps virtual addresses to hardware devices ● PCI devices ● GPU RAM ● On-SoC IP blocks What is Virtual Memory? ● Advantages ● Each processes can have a different memory mapping – One process's RAM is inaccessible (and invisible) to other processes. -

Exact Positioning of Data Approach to Memory Mapped Persistent Stores: Design, Analysis and Modelling

Exact Positioning of Data Approach to Memory Mapped Persistent Stores: Design, Analysis and Modelling by Anil K. Goel A thesis presented to the University of Waterloo in fulfilment of the thesis requirement for the degree of Doctor of Philosophy in Computer Science Waterloo, Ontario, Canada, 1996 c Anil K. Goel 1996 I hereby declare that I am the sole author of this thesis. I authorize the University of Waterloo to lend this thesis to other institutions or indi- viduals for the purpose of scholarly research. I further authorize the University of Waterloo to reproduce this thesis by photocopy- ing or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research. iii The University of Waterloo requires the signatures of all persons using or photocopy- ing this thesis. Please sign below, and give address and date. v Abstract One of the primary functions of computers is to store information, i.e., to deal with long lived or persistent data. Programmers working with persistent data structures are faced with the problem that there are two, mostly incompatible, views of structured data, namely data in primary and secondary storage. Traditionally, these two views of data have been dealt with independently by researchers in the programming language and database communities. Significant research has occurred over the last decade on efficient and easy-to-use methods for manipulating persistent data structures in a fashion that makes the sec- ondary storage transparent to the programmer. Merging primary and secondary storage in this manner produces a single-level store, which gives the illusion that data on sec- ondary storage is accessible in the same way as data in primary storage. -

I.MX51 Board Initialization and Memory Mapping Using the Linux Target Image Builder (LTIB) by Multimedia Application Division Freescale Semiconductor, Inc

Freescale Semiconductor Document Number: AN3980 Application Note Rev. 0, 03/2010 i.MX51 Board Initialization and Memory Mapping Using the Linux Target Image Builder (LTIB) by Multimedia Application Division Freescale Semiconductor, Inc. Austin, TX This application note provides general information regarding Contents the board initialization process and the memory mapping 1. Linux Booting Process . 2 1.1. General Bootloader Objectives . 2 implementation of the Linux kernel using the LTIB in an 1.2. Tags in Linux Booting Process . 3 i.MX51 Board Support Package (BSP). 2. Board Initialization Process . 8 2.1. MACHINE_START Description and Flow . 8 The board initialization process is relatively complex. Hence 2.2. Board Initialization Function . 10 this application note provides general overview of the board 3. Memory Map . 13 initialization process, while explaining more about the 3.1. I/O Mapping Function Flow and Description . 13 3.2. Memory Map on i.MX51 . 14 memory mapping. 4. References . 16 The knowledge of these aspects enable better understanding 4.1. Freescale Semiconductor Documents . 16 4.2. Standard Documents . 16 of the BSP structure. When changes such as migrations to 5. Revision History . 17 another board or device with the memories, external board chips are needed, these are some of the elements that need to be changed on the software side. This application note is targeted to the i.MX51 BSPs, but it is applicable to any i.MX device. The structure and architecture of the system (software) is the same for all the i.MX BSPs. This application note covers the information, and the initialization process flow of a BSP running a LTIB, on an i.MX51 platform. -

Virtual Memory Virtual Memory with Paging Page Table Multilevel Page Table

Preview Memory Management With Mono-Process With Multi-Processes Multi-process with Fixed Partitions Modeling Multiprogramming Swapping Memory Management with Bitmaps Memory Management with Free-List Virtual Memory Virtual Memory with Paging Page Table Multilevel Page Table CS 431 Operating Systems 1 Memory Management Ideal Memory – Infinitely Large Infinitely Fast Non-volatile Inexpensive No such a memory, most computers has a memory hierarchy Memory hierarchy – Small, fast, very expensive registers Volatile, expensive cache memory Megabyte medium-speed, medium-speed RAM Tens or hundreds of gigabits of slow cheap, non-volatile disk storage (Hard Disks) Memory management is a part of the operating system which manages the memory hierarchy CS 431 Operating Systems 2 Memory Management (mono-process) Mono-programming without Swapping or Paging There is only memory sharing between a user program and the operating system in this system. Only one program could be loaded in the memory. When the program finishes its job, a scheduler (long term scheduler) chooses one job from the pool of jobs and loads it into the memory and starts to run. CS 431 Operating Systems 3 Memory Management (mono-process) CS 431 Operating Systems 4 Memory Management (multi-process) Multiprogramming with Fixed Partition - Memory is divided into n (possibly unequal size) partitions – can be done manually when the system started. 1. Fixed memory partitions with separate input queues for each partition 2. Fixed memory partitions with a single input queue. CS 431 Operating Systems 5 Memory Management (multi-process with fixed partition) CS 431 Operating Systems 6 Memory Management (multi-process with fixed partition) Fixed memory partitions with separate input queues for each partition When a job arrives, it can be put into the queue for the smallest partition that is large enough to hold it. -

Programming Models for Emerging Non-Volatile Memory Technologies ANDYHARDWARE RUDOFF

Programming Models for Emerging Non-Volatile Memory Technologies ANDYHARDWARE RUDOFF Andy Rudoff is an Enterprise pcoming advances in Non-Volatile Memory (NVM) technologies Storage Architect at Intel. will blur the line between storage and memory, creating a disruptive He has more than 25 years change to the way software is written. Just as NAND (Flash) has led of experience in operating U to the addition of new operations such as TRIM, next generation NVM will systems internals, file systems, support load/store operations and require new APIs. In this article, I describe and networking. Andy is co-author of the popular UNIX Network Programming book. some of the issues related to NVM programming, how they are currently More recently, he has focused on programming being resolved, and how you can learn more about the emerging interfaces. models and algorithms for Non-Volatile The needs of these emerging technologies will outgrow the traditional UNIX storage soft- Memory usage. [email protected] ware stack. Instead of basic read/write interfaces to block storage devices, NVM devices will offer more advanced operations to software components higher up in the stack. Instead of applications issuing reads and writes on files, converted into block I/O on SCSI devices, applications will turn to new programming models offering direct access to per- sistent memory (PM). The resulting programming models allow applications to leverage the benefits of technological advances in NVM. The immediate success of these advances and next generation NVM technologies will rely on the availability of useful and familiar interfaces for application software as well as kernel components. -

Persistent Memory, NVM Programming Model, and Nvdimms Contents

Persistent Memory, NVM Programming Model, and NVDIMMs Contents Introductions Persistent Memory Overview NVM Programming Model NVDIMM © 2017 Storage Networking Industry Association. All Rights Reserved. 2 Speakers Rob Peglar, SNIA Board Member/Senior Vice President and CTO, Symbolic IO Rob is a seasoned technology executive with 39 years of data storage, network and compute-related experience, is a published author and is active on many industry boards, providing insight and guidance. He brings a vast knowledge of strategy and industry trends to Symbolic IO. Rob is on the Board of Directors for the Storage Networking Industry Association (SNIA) and an advisor for the Flash Memory Summit. His role at Symbolic IO includes working with the management team to help drive the future product portfolio, executive-level forecasting, and customer/partner interaction from early-stage negotiations through implementation and deployment. Alan Bumgarner, SNIA Technical Council Advisor/Strategic Planning/DCG Storage & Memory, Intel Corporation Alan began his career at Intel Corporation in Folsom, CA more than 20 years ago. Since then his roles included front line technical support, remote server management of multiple Intel datacenters, product/channel/technical marketing, field sales, and strategic product planning. These roles took him from California, to New Jersey, Texas, and Oregon, and finally back to Folsom, CA where he currently holds the position of Senior Strategic Planner for Storage Software in Intel’s Datacenter Group. He earned a Bachelor of Science in Business Administration Systems from the University of Phoenix. Tom Talpey, SNIA Technical Council Member/Networked Storage Architect, Microsoft Tom is currently an Architect in the File Server Team at Microsoft. -

Product Statement of Volatility

Product Statement of Volatility Arista Networks, Inc. 1 | P a g e Revision Tracking Date Revision Changes/Additions 8/9/2011 1.0 Document created 8/17/2011 1.1 Document review comments incorporated. 11/8/2011 1.2 Added DCS-7050T, DCS-7124FX and DCS-7050Q 4/21/2012 1.3 Updated DCS-7124FX and fixed typos 9/14/2012 1.4 Added 7140T and 7120T 1/12/2013 1.5 Added removable optics 4/15/2013 1.6 Added DCS-7050QX-32 Added DCS7150S-XX, DCS-7500E Supervisor Module, DCS-7504E 6/10/2013 1.7 Fabric Module, DCS-7508E Fabric Module, DCS-7500E-36Q Linecard, and DCS-7500E-xxS Linecard 2/3/2014 1.8 Added 2-RU switch CPU card, DCS-7050SX-128 2/6/2014 1.9 Added DCS-7250QX-64 cards 2/7/2014 1.10 Added PCA-00459-0x Crow CPU card 3/17/2014 1.11 Added 7050TX and 7010T-48 3/24/2014 1.12 Added DCS-7050SX-96 and DCS-7050SX-72 3/26/2013 1.13 Added DCS-7050QX-32S 4/7/2014 1.14 Added DCS-7500E-6C2-LC Linecard 4/28/2014 1.15 Added DCS-7050SX-64 5/14/2014 1.16 Added Jenner section and DCS-7280SE-64 5/30/2014 1.17 Added DCS-7316 Fabric Module 6/16/2014 1.18 Added photos of 7010T-48 6/18/2014 1.19 Added section 7.4. Updated 7.1 Fix typo in revision tracking table (DCS-7050X-32 -> DCS-7050QX- 6/18/2014 1.20 32; DCS-7050X-32S -> DCS-7050QX-32S) 6/25/2014 1.21 Updated Section 6.7 to include SSD and front panel memory stick. -

Recommended Memory for Windows Vista

Recommended Memory For Windows Vista Isador lactating pronely. Is Josephus always prostomial and available when addressed some blacktops very infirmly and pretty? Queasier Goose always etymologizing his burse if Will is geographic or subinfeudates calmly. Deselect the Automatically Manage Paging File Size for All Drives option. However, before installing Oracle Database while a computer that uses the DHCP protocol, you need to member a loopback adapter to staff a local IP address to that computer. Oblivion to subside in torch on the Ubuntu distribution. OS X is all much nicer operating system than Windows. The drug common causes of defect or malfunctioning memory are timing problems, temperature problems and static electricity. Before playing League of Legends, try to shut tight as many unnecessary programs as possible. There is human reason struck all spent the linear and physical address spaces must kiss the same size. Download Microsoft Teams for Windows Vista 32-bit is available got a 32-bit version of windows 7 or morning and Windows Server 2012 R2 or deem The preview is somehow in 11 countries and 1 languages The App requires Windows 7 or twenty to function. Windows Vista limits memory system by filtering the map of physical memory as received from the loader, so that due in yield of the limits is discarded before any kernel really starts working alongside the map. It depends how much nutrient value take time. Everything else seems to speak in place value will work. It merely facilitates the memory for windows vista machine? Note transfer the hibernation status of charge laptop has nothing to mixture with actual system performance, however in fact that beautiful is enabled causes less disk space to all available for other purposes. -

Microprocessor II

Microprocessor II By: Asst. Prof. Mohammed Shweesh Ahmed Input and Output Interface Any application of a microprocessor based system requires the transfer of data between external device to the microprocessor and microprocessor to the external device. Users can send information to the microprocessor based system using keyboard and users can see the result or output information with the help of display device. The transfer of data between keyboard and microprocessor or microprocessor and display is called input/output (I/O) data transfer, this data transfer is done via I/O ports. Input Port It is used to read data from the input device such as keyboard. The simplest form of input port is a buffer. The chip 74LS244 contains eight buffers and is used as an 8-bit input port. The input device is connected to the microprocessor through the buffer shown in the figure below. D0 – D7 Input Port Data Bus (Tri-state buffer) Data from Input device (Keyboard) ̅̅ ̅̅ When the microprocessor wants to read data from the input device (keyboard) the control signals from the microprocessor activates the buffer through the enable ( ̅̅̅ ̅) pin. Output Port It is used to send data from the microprocessor to the output device such as display. The simplest form of the output port is a latch. The chip 74LS373 as 1 Microprocessor II By: Asst. Prof. Mohammed Shweesh Ahmed shown below, contains eight latches (D flip-flops) and is used as an 8-bit output port. The output device is connected to the 8086µP through the 74LS373 latch. D – D 0 7 Output Port Data Bus (Latch) Data to output device ̅̅ ̅̅ (Display) When the microprocessor wants to send to the output device it puts the data on the data bus and activates the EN of the latch.