Optimizing Memory-Mapped I/O for Fast Storage Devices

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Beej's Guide to Unix IPC

Beej's Guide to Unix IPC Brian “Beej Jorgensen” Hall [email protected] Version 1.1.3 December 1, 2015 Copyright © 2015 Brian “Beej Jorgensen” Hall This guide is written in XML using the vim editor on a Slackware Linux box loaded with GNU tools. The cover “art” and diagrams are produced with Inkscape. The XML is converted into HTML and XSL-FO by custom Python scripts. The XSL-FO output is then munged by Apache FOP to produce PDF documents, using Liberation fonts. The toolchain is composed of 100% Free and Open Source Software. Unless otherwise mutually agreed by the parties in writing, the author offers the work as-is and makes no representations or warranties of any kind concerning the work, express, implied, statutory or otherwise, including, without limitation, warranties of title, merchantibility, fitness for a particular purpose, noninfringement, or the absence of latent or other defects, accuracy, or the presence of absence of errors, whether or not discoverable. Except to the extent required by applicable law, in no event will the author be liable to you on any legal theory for any special, incidental, consequential, punitive or exemplary damages arising out of the use of the work, even if the author has been advised of the possibility of such damages. This document is freely distributable under the terms of the Creative Commons Attribution-Noncommercial-No Derivative Works 3.0 License. See the Copyright and Distribution section for details. Copyright © 2015 Brian “Beej Jorgensen” Hall Contents 1. Intro................................................................................................................................................................1 1.1. Audience 1 1.2. Platform and Compiler 1 1.3. -

Mmap and Dma

CHAPTER THIRTEEN MMAP AND DMA This chapter delves into the area of Linux memory management, with an emphasis on techniques that are useful to the device driver writer. The material in this chap- ter is somewhat advanced, and not everybody will need a grasp of it. Nonetheless, many tasks can only be done through digging more deeply into the memory man- agement subsystem; it also provides an interesting look into how an important part of the kernel works. The material in this chapter is divided into three sections. The first covers the implementation of the mmap system call, which allows the mapping of device memory directly into a user process’s address space. We then cover the kernel kiobuf mechanism, which provides direct access to user memory from kernel space. The kiobuf system may be used to implement ‘‘raw I/O’’ for certain kinds of devices. The final section covers direct memory access (DMA) I/O operations, which essentially provide peripherals with direct access to system memory. Of course, all of these techniques requir e an understanding of how Linux memory management works, so we start with an overview of that subsystem. Memor y Management in Linux Rather than describing the theory of memory management in operating systems, this section tries to pinpoint the main features of the Linux implementation of the theory. Although you do not need to be a Linux virtual memory guru to imple- ment mmap, a basic overview of how things work is useful. What follows is a fairly lengthy description of the data structures used by the kernel to manage memory. -

An Introduction to Linux IPC

An introduction to Linux IPC Michael Kerrisk © 2013 linux.conf.au 2013 http://man7.org/ Canberra, Australia [email protected] 2013-01-30 http://lwn.net/ [email protected] man7 .org 1 Goal ● Limited time! ● Get a flavor of main IPC methods man7 .org 2 Me ● Programming on UNIX & Linux since 1987 ● Linux man-pages maintainer ● http://www.kernel.org/doc/man-pages/ ● Kernel + glibc API ● Author of: Further info: http://man7.org/tlpi/ man7 .org 3 You ● Can read a bit of C ● Have a passing familiarity with common syscalls ● fork(), open(), read(), write() man7 .org 4 There’s a lot of IPC ● Pipes ● Shared memory mappings ● FIFOs ● File vs Anonymous ● Cross-memory attach ● Pseudoterminals ● proc_vm_readv() / proc_vm_writev() ● Sockets ● Signals ● Stream vs Datagram (vs Seq. packet) ● Standard, Realtime ● UNIX vs Internet domain ● Eventfd ● POSIX message queues ● Futexes ● POSIX shared memory ● Record locks ● ● POSIX semaphores File locks ● ● Named, Unnamed Mutexes ● System V message queues ● Condition variables ● System V shared memory ● Barriers ● ● System V semaphores Read-write locks man7 .org 5 It helps to classify ● Pipes ● Shared memory mappings ● FIFOs ● File vs Anonymous ● Cross-memory attach ● Pseudoterminals ● proc_vm_readv() / proc_vm_writev() ● Sockets ● Signals ● Stream vs Datagram (vs Seq. packet) ● Standard, Realtime ● UNIX vs Internet domain ● Eventfd ● POSIX message queues ● Futexes ● POSIX shared memory ● Record locks ● ● POSIX semaphores File locks ● ● Named, Unnamed Mutexes ● System V message queues ● Condition variables ● System V shared memory ● Barriers ● ● System V semaphores Read-write locks man7 .org 6 It helps to classify ● Pipes ● Shared memory mappings ● FIFOs ● File vs Anonymous ● Cross-memoryn attach ● Pseudoterminals tio a ● proc_vm_readv() / proc_vm_writev() ● Sockets ic n ● Signals ● Stream vs Datagram (vs uSeq. -

Table of Contents

TABLE OF CONTENTS Chapter 1 Introduction ............................................................................................. 3 Chapter 2 Examples for FPGA ................................................................................. 4 2.1 Factory Default Code ................................................................................................................................. 4 2.2 Nios II Control for Programmable PLL/ Temperature/ Power/ 9-axis ....................................................... 6 2.3 Nios DDR4 SDRAM Test ........................................................................................................................ 12 2.4 RTL DDR4 SDRAM Test ......................................................................................................................... 14 2.5 USB Type-C DisplayPort Alternate Mode ............................................................................................... 15 2.6 USB Type-C FX3 Loopback .................................................................................................................... 17 2.7 HDMI TX and RX in 4K Resolution ........................................................................................................ 21 2.8 HDMI TX in 4K Resolution ..................................................................................................................... 26 2.9 Low Latency Ethernet 10G MAC Demo .................................................................................................. 29 2.10 Socket -

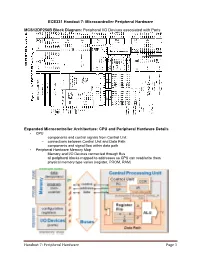

Memory Map: 68HC12 CPU and MC9S12DP256B Evaluation Board

ECE331 Handout 7: Microcontroller Peripheral Hardware MCS12DP256B Block Diagram: Peripheral I/O Devices associated with Ports Expanded Microcontroller Architecture: CPU and Peripheral Hardware Details • CPU – components and control signals from Control Unit – connections between Control Unit and Data Path – components and signal flow within data path • Peripheral Hardware Memory Map – Memory and I/O Devices connected through Bus – all peripheral blocks mapped to addresses so CPU can read/write them – physical memory type varies (register, PROM, RAM) Handout 7: Peripheral Hardware Page 1 Memory Map: 68HCS12 CPU and MC9S12DP256B Evaluation Board Configuration Register Set Physical Memory Handout 7: Peripheral Hardware Page 2 Handout 7: Peripheral Hardware Page 3 HCS12 Modes of Operation MODC MODB MODA Mode Port A Port B 0 0 0 special single chip G.P. I/O G.P. I/O special expanded 0 0 1 narrow Addr/Data Addr 0 1 0 special peripheral Addr/Data Addr/Data 0 1 1 special expanded wide Addr/Data Addr/Data 1 0 0 normal single chip G.P. I/O G.P. I/O normal expanded 1 0 1 narrow Addr/Data Addr 1 1 0 reserved -- -- 1 1 1 normal expanded wide Addr/Data Addr/Data G.P. = general purpose HCS12 Ports for Expanded Modes Handout 7: Peripheral Hardware Page 4 Memory Basics •RAM: Random Access Memory – historically defined as memory array with individual bit access – refers to memory with both Read and Write capabilities •ROM: Read Only Memory – no capabilities for “online” memory Write operations – Write typically requires high voltages or erasing by UV light • Volatility of Memory – volatile memory loses data over time or when power is removed • RAM is volatile – non-volatile memory stores date even when power is removed • ROM is no n-vltilvolatile • Static vs. -

IPC: Mmap and Pipes

Interprocess Communication: Memory mapped files and pipes CS 241 April 4, 2014 University of Illinois 1 Shared Memory Private Private address OS address address space space space Shared Process A segment Process B Processes request the segment OS maintains the segment Processes can attach/detach the segment 2 Shared Memory Private Private Private address address space OS address address space space space Shared Process A segment Process B Can mark segment for deletion on last detach 3 Shared Memory example /* make the key: */ if ((key = ftok(”shmdemo.c", 'R')) == -1) { perror("ftok"); exit(1); } /* connect to (and possibly create) the segment: */ if ((shmid = shmget(key, SHM_SIZE, 0644 | IPC_CREAT)) == -1) { perror("shmget"); exit(1); } /* attach to the segment to get a pointer to it: */ data = shmat(shmid, (void *)0, 0); if (data == (char *)(-1)) { perror("shmat"); exit(1); } 4 Shared Memory example /* read or modify the segment, based on the command line: */ if (argc == 2) { printf("writing to segment: \"%s\"\n", argv[1]); strncpy(data, argv[1], SHM_SIZE); } else printf("segment contains: \"%s\"\n", data); /* detach from the segment: */ if (shmdt(data) == -1) { perror("shmdt"); exit(1); } return 0; } Run demo 5 Memory Mapped Files Memory-mapped file I/O • Map a disk block to a page in memory • Allows file I/O to be treated as routine memory access Use • File is initially read using demand paging ! i.e., loaded from disk to memory only at the moment it’s needed • When needed, a page-sized portion of the file is read from the file system -

A Machine-Independent DMA Framework for Netbsd

AMachine-Independent DMA Framework for NetBSD Jason R. Thorpe1 Numerical Aerospace Simulation Facility NASA Ames Research Center Abstract 1.1. Host platform details One of the challenges in implementing a portable In the example platforms listed above,there are at kernel is finding good abstractions for semantically- least three different mechanisms used to perform DMA. similar operations which often have very machine- The first is used by the i386 platform. This mechanism dependent implementations. This is especially impor- can be described as "what you see is what you get": the tant on modern machines which share common archi- address that the device uses to perform the DMA trans- tectural features, e.g. the PCI bus. fer is the same address that the host CPU uses to access This paper describes whyamachine-independent the memory location in question. DMA mapping abstraction is needed, the design consid- DMA address Host address erations for such an abstraction, and the implementation of this abstraction in the NetBSD/alpha and NetBSD/i386 kernels. 1. Introduction NetBSD is a portable, modern UNIX-likeoperat- ing system which currently runs on eighteen platforms covering nine processor architectures. Some of these platforms, including the Alpha and i3862,share the PCI busasacommon architectural feature. In order to share device drivers for PCI devices between different platforms, abstractions that hide the details of bus access must be invented. The details that must be hid- den can be broken down into twoclasses: CPU access Figure 1 - WYSIWYG DMA to devices on the bus (bus_space)and device access to host memory (bus_dma). Here we will discuss the lat- The second mechanism, employed by the Alpha, ter; bus_space is a complicated topic in and of itself, is very similar to the first; the address the host CPU and is beyond the scope of this paper. -

Interprocess Communication

06 0430 CH05 5/22/01 10:22 AM Page 95 5 Interprocess Communication CHAPTER 3,“PROCESSES,” DISCUSSED THE CREATION OF PROCESSES and showed how one process can obtain the exit status of a child process.That’s the simplest form of communication between two processes, but it’s by no means the most powerful.The mechanisms of Chapter 3 don’t provide any way for the parent to communicate with the child except via command-line arguments and environment variables, nor any way for the child to communicate with the parent except via the child’s exit status. None of these mechanisms provides any means for communicating with the child process while it is actually running, nor do these mechanisms allow communication with a process outside the parent-child relationship. This chapter describes means for interprocess communication that circumvent these limitations.We will present various ways for communicating between parents and chil- dren, between “unrelated” processes, and even between processes on different machines. Interprocess communication (IPC) is the transfer of data among processes. For example, a Web browser may request a Web page from a Web server, which then sends HTML data.This transfer of data usually uses sockets in a telephone-like connection. In another example, you may want to print the filenames in a directory using a command such as ls | lpr.The shell creates an ls process and a separate lpr process, connecting 06 0430 CH05 5/22/01 10:22 AM Page 96 96 Chapter 5 Interprocess Communication the two with a pipe, represented by the “|” symbol.A pipe permits one-way commu- nication between two related processes.The ls process writes data into the pipe, and the lpr process reads data from the pipe. -

Real-Time Streaming Video and Image Processing on Inexpensive Hardware with Low Latency

University of Nebraska - Lincoln DigitalCommons@University of Nebraska - Lincoln Theses, Dissertations, and Student Research Electrical & Computer Engineering, Department from Electrical & Computer Engineering of Spring 5-2018 Real-Time Streaming Video and Image Processing on Inexpensive Hardware with Low Latency Richard L. Gregg University of Nebraska - Lincoln, [email protected] Follow this and additional works at: https://digitalcommons.unl.edu/elecengtheses Part of the Computer Engineering Commons, and the Other Electrical and Computer Engineering Commons Gregg, Richard L., "Real-Time Streaming Video and Image Processing on Inexpensive Hardware with Low Latency" (2018). Theses, Dissertations, and Student Research from Electrical & Computer Engineering. 93. https://digitalcommons.unl.edu/elecengtheses/93 This Article is brought to you for free and open access by the Electrical & Computer Engineering, Department of at DigitalCommons@University of Nebraska - Lincoln. It has been accepted for inclusion in Theses, Dissertations, and Student Research from Electrical & Computer Engineering by an authorized administrator of DigitalCommons@University of Nebraska - Lincoln. Real-Time Streaming Video And Image Processing On Inexpensive Hardware With Low Latency by Richard L. Gregg A THESIS Presented to the Faculty of The Graduate College at the University of Nebraska In Partial Fulfillment of Requirements For the Degree of Master of Science Major: Telecommunications Engineering Under the Supervision of Professor Dongming Peng Lincoln, Nebraska May 2018 REAL-TIME STREAMING VIDEO AND IMAGE PROCESSING ON INEXPENSIVE HARDWARE WITH LOW LATENCY Richard L. Gregg, M.S. University of Nebraska, 2018 Advisor: Dongming Peng The use of resource constrained inexpensive hardware places restrictions on the design of streaming video and image processing system performance. -

Lecture 14: Paging

Lecture 14: Paging Fall 2018 Jason Tang Slides based upon Operating System Concept slides, http://codex.cs.yale.edu/avi/os-book/OS9/slide-dir/index.html Copyright Silberschatz, Galvin, and Gagne, 2013 "1 Topics • Memory Mappings! • Page Table! • Translation Lookaside Bu$ers! • Page Protection "2 Memory Mapped • Logical address translated not to memory but some other location! • Memory-mapped I/O (MMIO): hardware redirects read/write of certain addresses to physical device! • For example, on x86, address 0x3F8 usually mapped to first serial port! • Memory-mapped file (mmap): OS redirects read/write of mapped memory region to file on disk! • Every call to read() / write() involves a system call! • Writing to a pointer faster, and OS can translate in the background (also see upcoming lecture) "3 Memory-Mapped File • In Linux, typical pattern is to:! • Open file, using open() function! • Optional: preallocate file size, using ftruncate()! • Create memory mapping, using mmap() function! • Do work, and then release mapping using munmap() function! • Kernel might not write data to disk until munmap() "4 mmap() function void *mmap(void *addr, size_t length, int prot, int flags, int fd, off_t offset) • addr is target address of mapping, or NULL to let kernel decide! • length is number of bytes to map! • prot defines what mapping protection (read-only or read/write)! • flags sets other options! • fd is file descriptor that was returned by open()! • offset is o$set into file specified by fd "5 mmap() example part 1 • See man page for each of these functions -

Process Address Spaces and Binary Formats

2/5/20 COMP 790: OS Implementation COMP 790: OS Implementation Logical Diagram Binary Memory Process Address Spaces Threads Formats AllocatorsToday’s and Binary Formats Lecture User System Calls Kernel Don Porter RCU File System Networking Sync Memory Device CPU Management Drivers Scheduler Hardware Interrupts Disk Net Consistency 1 2 1 2 COMP 790: OS Implementation COMP 790: OS Implementation Review Definitions (can vary) • We’ve seen how paging and segmentation work on • Process is a virtual address space x86 – 1+ threads of execution work within this address space – Maps logical addresses to physical pages • A process is composed of: – These are the low-level hardware tools – Memory-mapped files • This lecture: build up to higher-level abstractions • Includes program binary • Namely, the process address space – Anonymous pages: no file backing • When the process exits, their contents go away 3 4 3 4 COMP 790: OS Implementation COMP 790: OS Implementation Address Space Layout Simple Example • Determined (mostly) by the application • Determined at compile time Virtual Address Space – Link directives can influence this hello heap stk libc.so • See kern/kernel.ld in JOS; specifies kernel starting address • OS usually reserves part of the address space to map 0 0xffffffff itself • “Hello world” binary specified load address – Upper GB on x86 Linux • Also specifies where it wants libc • Application can dynamically request new mappings from the OS, or delete mappings • Dynamically asks kernel for “anonymous” pages for its heap and stack 5 6 5 6 1 2/5/20 COMP 790: OS Implementation COMP 790: OS Implementation In practice Problem 1: How to represent in the kernel? • You can see (part of) the requested memory layout • What is the best way to represent the components of of a program using ldd: a process? $ ldd /usr/bin/git – Common question: is mapped at address x? linux-vdso.so.1 => (0x00007fff197be000) • Page faults, new memory mappings, etc. -

User Guide Commplete 4000 Single Board Computer (IPC-623C) User Guide S000277A Revision a All Rights Reserved

MultiTech Model IPC-623C Single Board Computer for CommPlete 4000 Server User Guide CommPlete 4000 Single Board Computer (IPC-623C) User Guide S000277A Revision A All rights reserved. This publication may not be reproduced, in whole or in part, without prior expressed written permission from Multi-Tech Systems, Inc. All rights reserved. Copyright © 2002 by Multi-Tech Systems, Inc. Multi-Tech Systems, Inc. makes no representation or warranties with respect to the contents hereof and specifically disclaims any implied warranties of merchantability or fitness for any particular purpose. Furthermore, Multi-Tech Systems, Inc. reserves the right to revise this publication and to make changes from time to time in the content hereof without obligation of Multi-Tech Systems, Inc., to notify any person or organization of such revisions or changes. Record of Revisions Revision Description A Manual released (08/12/02). Patents This product is covered by one or more of the following U.S. Patent Numbers: 5.301.274, 5.309.562, 5.355.365, 5.355.653, 5.452.289, 5.453.986. Other patents Pending. Trademarks The Multi-Tech logo is a registered trademark of Multi-Tech Systems, Inc. NetWare is a registered trademark of Novell, Inc. Pentium is a registered trademark of Intel Corporation. SCO is a registered trademark of Santa Cruz Operation, Inc. UNIX is a registered trademark of X/Open Company, Ltd. Windows 95 and Windows NT are registered trademarks of Microsoft. Multi-Tech Systems, Inc. 2205 Woodale Drive Mounds View, Minnesota 55112 (763) 785-3500 or (800) 328-9717 Fax (763) 785-9874 Tech Support (800) 972-2439 Internet Address: http://www.multitech.com Table of Contents Contents Chapter 1 - Introduction ...............................................................