Minimal Intel Architecture Boot Loader White Paper

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Linkers and Loaders Hui Chen Department of Computer & Information Science CUNY Brooklyn College

CISC 3320 MW3 Linkers and Loaders Hui Chen Department of Computer & Information Science CUNY Brooklyn College CUNY | Brooklyn College: CISC 3320 9/11/2019 1 OS Acknowledgement • These slides are a revision of the slides by the authors of the textbook CUNY | Brooklyn College: CISC 3320 9/11/2019 2 OS Outline • Linkers and linking • Loaders and loading • Object and executable files CUNY | Brooklyn College: CISC 3320 9/11/2019 3 OS Authoring and Running a Program • A programmer writes a program in a programming language (the source code) • The program resides on disk as a binary executable file translated from the source code of the program • e.g., a.out or prog.exe • To run the program on a CPU • the program must be brought into memory, and • create a process for it • A multi-step process CUNY | Brooklyn College: CISC 3320 9/11/2019 4 OS CUNY | Brooklyn College: CISC 3320 9/11/2019 5 OS Compilation • Source files are compiled into object files • The object files are designed to be loaded into any physical memory location, a format known as an relocatable object file. CUNY | Brooklyn College: CISC 3320 9/11/2019 6 OS Relocatable Object File • Object code: formatted machine code, but typically non-executable • Many formats • The Executable and Linkable Format (ELF) • The Common Object File Format (COFF) CUNY | Brooklyn College: CISC 3320 9/11/2019 7 OS Examining an Object File • In Linux/UNIX, $ file main.o main.o: ELF 64-bit LSB relocatable, x86-64, version 1 (SYSV), not stripped $ nm main.o • Also use objdump, readelf, elfutils, hexedit • You may need # apt-get install hexedit # apt-get install elfutils CUNY | Brooklyn College: CISC 3320 9/11/2019 8 OS Linking • During the linking phase, other object files or libraries may be included as well • Example: $ g++ -o main -lm main.o sumsine.o • A program consists of one or more object files. -

6 Boot Loader

BootBoot LoaderLoader 66 6.1 INTRODUCTION The Boot Loader is a utility program supplied with the ADSP-21000 Family Development Software. The loader converts an ADSP-21xxx executable program, generated by the linker, into a format which can be used to boot a target hardware system and initialize its memory. The loader’s invocation command is LDR21K. The boot loader replaces the MEM21K memory initializer used with the ADSP-21020 processor. Any executable file to be processed with the LDR21K boot loader must not be processed by MEM21K. The -nomem switch of the C compiler should be used when compiling any C source files—this switch prevents the compiler from running MEM21K. The following naming conventions are used throughout this chapter: The loader refers to LDR21K contained in the software release. The boot loader refers to the executable file that performs the memory initialization on the target. The boot file refers to the output of the loader that contains the boot loader and the formatted system configurations. Booting refers to the process of loading the boot loader, initialization system memory, and starting the application on the target. Memory is referred to as being either data memory, program memory, or internal memory. Remember that the ADSP-21020 processor has separate external program and data memories, but does not have any internal memory. The ADSP-2106x SHARC has both internal and external memory. 6 – 1 66 BootBoot LoaderLoader To use the loader, you should be familiar with the hardware requirements of booting an ADSP-21000 target. See Chapter 11 of the ADSP-2106x SHARC User’s Manual or Chapter 9 of the ADSP-21020 User’s Manual for further information. -

October 1998

OCTOBER 1998 GAME DEVELOPER MAGAZINE V GAME PLAN It’s First and Goal for EDITOR IN CHIEF Alex Dunne [email protected] MANAGING EDITOR Tor D. Berg [email protected] Fantasy Sports DEPARTMENTS EDITOR Wesley Hall whall@mfi.com his fall, as the leaves turn success stories. Unlike the traditional ART DIRECTOR Laura Pool lpool@mfi.com shades of orange and the days studio’s royalty revenue model, SWS has EDITOR-AT-LARGE Chris Hecker grow shorter, one of the two revenue streams: a two-year licens- [email protected] largest, most massively multi- ing agreement to develop more than 40 CONTRIBUTING EDITORS Jeff Lander T [email protected] player games picks up steam and sucks online games for CNN/SI (http://base- in participants. It’s a role-playing game ball.cnnsi.com), plus revenue from ban- Mel Guymon [email protected] that draws tens of thousands (gads, ner advertising displayed on the CNN/SI Omid Rahmat probably more) of players, and if my game’s web pages, which garner 50 mil- [email protected] predictions are right, it will be one of lion page views per month. Surprisingly, ADVISORY BOARD Hal Barwood the most popular attractions on the and in contrast to most commercial fan- Noah Falstein eventual TV set-top box. I’m talking tasy leagues, some of the CNN/SI Brian Hook about fantasy football leagues. leagues are free for participants and Susan Lee-Merrow It’s taken quite a bit of time for me to offer cash prizes for winners. These are Mark Miller 2 accept the fact that fantasy league sports the guppy leagues which, hopefully, (there are also fantasy leagues for base- entice the most enthusiastic players to COVER IMAGE Epic MegaGames ball, hockey, and perhaps even pro join the premiere leagues for $15. -

P72 User Guide

P72 User Guide Note: Before using this information and the product it supports, ensure that you read and understand the following: • Safety and Warranty Guide • Setup Guide • “Important safety information” on page iii Lenovo makes constant improvement on the documentation of your computer, including this User Guide. To get all the latest documents, go to: https://support.lenovo.com Depending on the version of operating systems, some user interface instructions might not be applicable to your computer. Second Edition (April 2019) © Copyright Lenovo 2019. LIMITED AND RESTRICTED RIGHTS NOTICE: If data or software is delivered pursuant to a General Services Administration “GSA” contract, use, reproduction, or disclosure is subject to restrictions set forth in Contract No. GS- 35F-05925. Contents Important safety information . iii Using the TrackPoint pointing device. 19 Read this first. iii Using the trackpad with buttons . 20 Important information about using your computer . iii Using the trackpad touch gestures . 20 Conditions that require immediate action . v Customizing the ThinkPad pointing device . 21 Service and upgrades . vi Replacing the cap on the pointing stick . 21 Power cords and power adapters . vii Power management . 22 Extension cords and related devices. vii Using the ac power adapter . 22 Plugs and outlets . viii Using the battery . 22 Power supply statement . viii Managing the battery power . 24 External devices . ix Power-saving modes . 24 General battery notice . ix Cabled Ethernet connections . 24 Notice for built-in rechargeable battery. ix Wireless connections . 25 Notice for non-rechargeable coin-cell battery . x Using the wireless-LAN connection . 25 Heat and product ventilation . xi Using the Bluetooth connection. -

North American Company Profiles 8X8

North American Company Profiles 8x8 8X8 8x8, Inc. 2445 Mission College Boulevard Santa Clara, California 95054 Telephone: (408) 727-1885 Fax: (408) 980-0432 Web Site: www.8x8.com Email: [email protected] Fabless IC Supplier Regional Headquarters/Representative Locations Europe: 8x8, Inc. • Bucks, England U.K. Telephone: (44) (1628) 402800 • Fax: (44) (1628) 402829 Financial History ($M), Fiscal Year Ends March 31 1992 1993 1994 1995 1996 1997 1998 Sales 36 31 34 20 29 19 50 Net Income 5 (1) (0.3) (6) (3) (14) 4 R&D Expenditures 7 7 7 8 8 11 12 Capital Expenditures — — — — 1 1 1 Employees 114 100 105 110 81 100 100 Ownership: Publicly held. NASDAQ: EGHT. Company Overview and Strategy 8x8, Inc. is a worldwide leader in the development, manufacture and deployment of an advanced Visual Information Architecture (VIA) encompassing A/V compression/decompression silicon, software, subsystems, and consumer appliances for video telephony, videoconferencing, and video multimedia applications. 8x8, Inc. was founded in 1987. The “8x8” refers to the company’s core technology, which is based upon Discrete Cosine Transform (DCT) image compression and decompression. In DCT, 8-pixel by 8-pixel blocks of image data form the fundamental processing unit. 2-1 8x8 North American Company Profiles Management Paul Voois Chairman and Chief Executive Officer Keith Barraclough President and Chief Operating Officer Bryan Martin Vice President, Engineering and Chief Technical Officer Sandra Abbott Vice President, Finance and Chief Financial Officer Chris McNiffe Vice President, Marketing and Sales Chris Peters Vice President, Sales Michael Noonen Vice President, Business Development Samuel Wang Vice President, Process Technology David Harper Vice President, European Operations Brett Byers Vice President, General Counsel and Investor Relations Products and Processes 8x8 has developed a Video Information Architecture (VIA) incorporating programmable integrated circuits (ICs) and compression/decompression algorithms (codecs) for audio/video communications. -

Performance Best Practices for Vmware Workstation Vmware Workstation 7.0

Performance Best Practices for VMware Workstation VMware Workstation 7.0 This document supports the version of each product listed and supports all subsequent versions until the document is replaced by a new edition. To check for more recent editions of this document, see http://www.vmware.com/support/pubs. EN-000294-00 Performance Best Practices for VMware Workstation You can find the most up-to-date technical documentation on the VMware Web site at: http://www.vmware.com/support/ The VMware Web site also provides the latest product updates. If you have comments about this documentation, submit your feedback to: [email protected] Copyright © 2007–2009 VMware, Inc. All rights reserved. This product is protected by U.S. and international copyright and intellectual property laws. VMware products are covered by one or more patents listed at http://www.vmware.com/go/patents. VMware is a registered trademark or trademark of VMware, Inc. in the United States and/or other jurisdictions. All other marks and names mentioned herein may be trademarks of their respective companies. VMware, Inc. 3401 Hillview Ave. Palo Alto, CA 94304 www.vmware.com 2 VMware, Inc. Contents About This Book 5 Terminology 5 Intended Audience 5 Document Feedback 5 Technical Support and Education Resources 5 Online and Telephone Support 5 Support Offerings 5 VMware Professional Services 6 1 Hardware for VMware Workstation 7 CPUs for VMware Workstation 7 Hyperthreading 7 Hardware-Assisted Virtualization 7 Hardware-Assisted CPU Virtualization (Intel VT-x and AMD AMD-V) -

Product Change Notification #111151

Product Change Notification #111151 - 01 Information in this document is provided in connection with Intel® products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel’s Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications. Intel may make changes to specifications and product descriptions at any time, without notice. Should you have any issues with the timeline or content of this change, please contact the Intel Representative(s) for your geographic location listed below. No response from customers will be deemed as acceptance of the change and the change will be implemented pursuant to the key milestones set forth in this attached PCN. Americas Contact: [email protected] Asia Pacific Contact: [email protected] Europe Email: [email protected] Japan Email: [email protected] Copyright © Intel Corporation 2011. Other names and brands may be claimed as the property of others. BunnyPeople, Celeron, Celeron Inside, Centrino, Centrino Inside, Cilk, Core Inside, i960, Intel, the Intel logo, Intel AppUp, Intel Atom, Intel Atom Inside, Intel Core, -

Memory Map: 68HC12 CPU and MC9S12DP256B Evaluation Board

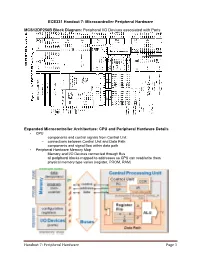

ECE331 Handout 7: Microcontroller Peripheral Hardware MCS12DP256B Block Diagram: Peripheral I/O Devices associated with Ports Expanded Microcontroller Architecture: CPU and Peripheral Hardware Details • CPU – components and control signals from Control Unit – connections between Control Unit and Data Path – components and signal flow within data path • Peripheral Hardware Memory Map – Memory and I/O Devices connected through Bus – all peripheral blocks mapped to addresses so CPU can read/write them – physical memory type varies (register, PROM, RAM) Handout 7: Peripheral Hardware Page 1 Memory Map: 68HCS12 CPU and MC9S12DP256B Evaluation Board Configuration Register Set Physical Memory Handout 7: Peripheral Hardware Page 2 Handout 7: Peripheral Hardware Page 3 HCS12 Modes of Operation MODC MODB MODA Mode Port A Port B 0 0 0 special single chip G.P. I/O G.P. I/O special expanded 0 0 1 narrow Addr/Data Addr 0 1 0 special peripheral Addr/Data Addr/Data 0 1 1 special expanded wide Addr/Data Addr/Data 1 0 0 normal single chip G.P. I/O G.P. I/O normal expanded 1 0 1 narrow Addr/Data Addr 1 1 0 reserved -- -- 1 1 1 normal expanded wide Addr/Data Addr/Data G.P. = general purpose HCS12 Ports for Expanded Modes Handout 7: Peripheral Hardware Page 4 Memory Basics •RAM: Random Access Memory – historically defined as memory array with individual bit access – refers to memory with both Read and Write capabilities •ROM: Read Only Memory – no capabilities for “online” memory Write operations – Write typically requires high voltages or erasing by UV light • Volatility of Memory – volatile memory loses data over time or when power is removed • RAM is volatile – non-volatile memory stores date even when power is removed • ROM is no n-vltilvolatile • Static vs. -

Virtual Table Hijacking Protection Enhancement for CFG

Liberation Guard: Virtual Table Hijacking Protection Enhancement for CFG Eyal Itkin [email protected] eyalitkin.wordpress.com Abstract—Control Flow Guard (CFG) is an advanced defense mechanism by Microsoft, that aims to mitigate exploiting tech- niques using control flow integrity checks. In this paper we1 present a proposed enhancement of CFG, that adds virtual table integrity checks which will mitigate most virtual table hijacking exploits. The proposed defense creates a strong differentiation between ordinary and virtual functions, thus significantly nar- rowing the exploit options available when controlling an indirect virtual call. This differentiation will impose strong restrictions over current virtual table hijacking exploits, thus significantly raising the protection CFG can offer to protected programs2. I. PRELIMINARIES Fig. 1. Example of address translation for an unaligned address (at the top) and an aligned address (at the bottom). A. Control Flow Guard Overview Control Flow Guard (CFG) is an advanced control flow integrity (CFI) defense mechanism introduced by Microsoft in In order to use this CFI knowledge, the compiler adds Windows 8.1 and Windows 10 [4]. CFG aims to significantly a validation check prior to each indirect call (only call restrict the allowed control flow in the cases of indirect calls, assembly opcode, and not jump opcodes). This function is and is supported in Visual Studio 2015. stored in ntdll.dll, and exported to the rest of the DLLs. This defense mechanism is based on the fact that during The function verifies the requested address against the stored compilation time the compiler ”learns” where ”legitimate” bitmap, while acting as a NOP in case the bit is ”1” and crashes functions start, and records these addresses in the compiled the program in case the bit is ”0”. -

IXP400 Software's Programmer's Guide

Intel® IXP400 Software Programmer’s Guide June 2004 Document Number: 252539-002c Intel® IXP400 Software Contents INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO SALE AND/OR USE OF INTEL PRODUCTS, INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT, OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel Corporation may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights. Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications. The Intel® IXP400 Software v1.2.2 may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request. MPEG is an international standard for video compression/decompression promoted by ISO. Implementations of MPEG CODECs, or MPEG enabled platforms may require licenses from various entities, including Intel Corporation. This document and the software described in it are furnished under license and may only be used or copied in accordance with the terms of the license. The information in this document is furnished for informational use only, is subject to change without notice, and should not be construed as a commitment by Intel Corporation. -

Product Change Notification 111325

Product Change Notification 111325 - 01 Information in this document is provided in connection with Intel® products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel’s Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications. Intel may make changes to specifications and product descriptions at any time, without notice. Should you have any issues with the timeline or content of this change, please contact the Intel Representative(s) for your geographic location listed below. No response from customers will be deemed as acceptance of the change and the change will be implemented pursuant to the key milestones set forth in this attached PCN. Americas Contact: [email protected] Asia Pacific/PRC Contact: [email protected] Europe Email: [email protected] Japan Email: [email protected] Copyright © Intel Corporation 2012. Other names and brands may be claimed as the property of others. BunnyPeople, Celeron, Celeron Inside, Centrino, Centrino Inside, Cilk, Core Inside, i960, Intel, the Intel logo, Intel AppUp, Intel Atom, Intel Atom Inside, Intel Core, -

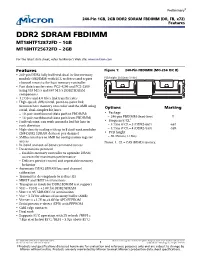

DDR2 SDRAM FBDIMM (DR, FB, X72) Features DDR2 SDRAM FBDIMM MT18HTF12872FD – 1GB MT18HTF25672FD – 2GB

Preliminary‡ 240-Pin 1GB, 2GB DDR2 SDRAM FBDIMM (DR, FB, x72) Features DDR2 SDRAM FBDIMM MT18HTF12872FD – 1GB MT18HTF25672FD – 2GB For the latest data sheet, refer to Micron’s Web site: www.micron.com Features Figure 1: 240-Pin FBDIMM (MO-256 R/C B) • 240-pin DDR2 fully buffered, dual in-line memory module (FBDIMM) with ECC to detect and report PCB height: 30.35mm (1.19in) channel errors to the host memory controller • Fast data transfer rates: PC2-4200 and PC2-5300 using 533 MT/s and 667 MT/s DDR2 SDRAM components • 3.2 Gb/s and 4.0 Gb/s link transfer rates • High-speed, differential, point-to-point link between host memory controller and the AMB using Options Marking serial, dual-simplex bit lanes – 10-pair southbound (data path to FBDIMM) •Package – 240-pin FBDIMM (lead-free) Y – 14-pair northbound (data path from FBDIMM) 1 • Fault tolerant; can work around a bad bit lane in •Frequency/CL each direction – 3.75ns @ CL = 5 (DDR2-667) -667 • High-density scaling with up to 8 dual-rank modules – 3.75ns @ CL = 4 (DDR2-533) -53E (288 DDR2 SDRAM devices) per channel •PCB height • SMBus interface to AMB for configuration register – 30.35mm (1.19in) access Notes: 1. CL = CAS (READ) latency. • In-band and out-of-band command access • Deterministic protocol – Enables memory controller to optimize DRAM accesses for maximum performance – Delivers precise control and repeatable memory behavior •Automatic DDR2 SDRAM bus and channel calibration • Transmitter de-emphasis to reduce ISI • MBIST and IBIST test functions • Transparent mode for DDR2 SDRAM test support •VDD = VDDQ = +1.8V for DDR2 SDRAM •VREF = 0 .9V SDRAM C/A termination •VCC = 1.5V for advanced memory buffer (AMB) •VDDSPD = +1.7V to +3.6V for SPD EEPROM • Serial presence-detect (SPD) with EEPROM • Gold edge contacts •Dual rank • Supports 95°C operation with 2X refresh (tREFI = 7.8µs at or below 85°C; tREFI = 3.9µs above 85°C) PDF: 09005aef81a2f20c/Source: 09005aef81a2f25b Micron Technology, Inc., reserves the right to change products or specifications without notice.