Efficient Memory Mapped File I/O for In-Memory File Systems

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Model Driven Scheduling for Virtualized Workloads

Model Driven Scheduling for Virtualized Workloads Proefschrift voorgelegd op 28 juni 2013 tot het behalen van de graad van Doctor in de Wetenschappen – Informatica, bij de faculteit Wetenschappen, aan de Universiteit Antwerpen. PROMOTOREN: prof. dr. Jan Broeckhove dr. Kurt Vanmechelen Sam Verboven RESEARCH GROUP COMPUTATIONAL MODELINGAND PROGRAMMING Dankwoord Het behalen van een doctoraat is een opdracht die zonder hulp onmogelijk tot een goed einde kan gebracht worden. Gelukkig heb ik de voorbije jaren de kans gekregen om samen te werken met talrijke stimulerende collega’s. Stuk voor stuk hebben zij bijgedragen tot mijn professionele en persoonlijke ontwikkeling. Hun geduldige hulp en steun was essentieel bij het overwinnen van de vele uitdagingen die met een doctoraat gepaard gaan. Graag zou ik hier dan ook enkele woorden van dank neerschrijven. Allereerst zou ik graag prof. dr. Jan Broeckhove en em. prof. dr. Frans Arickx bedanken om mij de kans te geven een gevarieerde en boeiend academisch traject te starten. Bij het beginnen van mijn doctoraat heeft Frans mij niet alleen geholpen om een capabel onderzoeker te worden, ook bij het lesgeven heeft hij mij steeds met raad en daad bijgestaan. Na het emiraat van Frans heeft Jan deze begeleiding overgenomen en er voor gezorgd dat ik het begonnen traject ook succesvol kon beeïndigen. Beiden hebben ze mij steeds grote vrijheid gegeven in mijn zoektocht om interessante onderzoeksvragen te identificeren en beantwoorden. Vervolgens zou ik graag dr. Peter Hellinckx en dr. Kurt Vanmechelen bedanken voor hun persoonlijke en vaak intensieve begeleiding. Zelfs voor de start van mijn academische carrière, bij het schrijven van mijn Master thesis, heeft Peter mij klaar- gestoomd voor een vlotte start als onderzoeker. -

Towards Better Performance Per Watt in Virtual Environments on Asymmetric Single-ISA Multi-Core Systems

Towards Better Performance Per Watt in Virtual Environments on Asymmetric Single-ISA Multi-core Systems Viren Kumar Alexandra Fedorova Simon Fraser University Simon Fraser University 8888 University Dr 8888 University Dr Vancouver, Canada Vancouver, Canada [email protected] [email protected] ABSTRACT performance per watt than homogeneous multicore proces- Single-ISA heterogeneous multicore architectures promise to sors. As power consumption in data centers becomes a grow- deliver plenty of cores with varying complexity, speed and ing concern [3], deploying ASISA multicore systems is an performance in the near future. Virtualization enables mul- increasingly attractive opportunity. These systems perform tiple operating systems to run concurrently as distinct, in- at their best if application workloads are assigned to het- dependent guest domains, thereby reducing core idle time erogeneous cores in consideration of their runtime proper- and maximizing throughput. This paper seeks to identify a ties [4][13][12][18][24][21]. Therefore, understanding how to heuristic that can aid in intelligently scheduling these vir- schedule data-center workloads on ASISA systems is an im- tualized workloads to maximize performance while reducing portant problem. This paper takes the first step towards power consumption. understanding the properties of data center workloads that determine how they should be scheduled on ASISA multi- We propose that the controlling domain in a Virtual Ma- core processors. Since virtual machine technology is a de chine Monitor or hypervisor is relatively insensitive to changes facto standard for data centers, we study virtual machine in core frequency, and thus scheduling it on a slower core (VM) workloads. saves power while only slightly affecting guest domain per- formance. -

Memory Map: 68HC12 CPU and MC9S12DP256B Evaluation Board

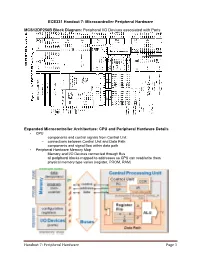

ECE331 Handout 7: Microcontroller Peripheral Hardware MCS12DP256B Block Diagram: Peripheral I/O Devices associated with Ports Expanded Microcontroller Architecture: CPU and Peripheral Hardware Details • CPU – components and control signals from Control Unit – connections between Control Unit and Data Path – components and signal flow within data path • Peripheral Hardware Memory Map – Memory and I/O Devices connected through Bus – all peripheral blocks mapped to addresses so CPU can read/write them – physical memory type varies (register, PROM, RAM) Handout 7: Peripheral Hardware Page 1 Memory Map: 68HCS12 CPU and MC9S12DP256B Evaluation Board Configuration Register Set Physical Memory Handout 7: Peripheral Hardware Page 2 Handout 7: Peripheral Hardware Page 3 HCS12 Modes of Operation MODC MODB MODA Mode Port A Port B 0 0 0 special single chip G.P. I/O G.P. I/O special expanded 0 0 1 narrow Addr/Data Addr 0 1 0 special peripheral Addr/Data Addr/Data 0 1 1 special expanded wide Addr/Data Addr/Data 1 0 0 normal single chip G.P. I/O G.P. I/O normal expanded 1 0 1 narrow Addr/Data Addr 1 1 0 reserved -- -- 1 1 1 normal expanded wide Addr/Data Addr/Data G.P. = general purpose HCS12 Ports for Expanded Modes Handout 7: Peripheral Hardware Page 4 Memory Basics •RAM: Random Access Memory – historically defined as memory array with individual bit access – refers to memory with both Read and Write capabilities •ROM: Read Only Memory – no capabilities for “online” memory Write operations – Write typically requires high voltages or erasing by UV light • Volatility of Memory – volatile memory loses data over time or when power is removed • RAM is volatile – non-volatile memory stores date even when power is removed • ROM is no n-vltilvolatile • Static vs. -

Big Data Benchmarking Workshop Publications

Benchmarking Datacenter and Big Data Systems Wanling Gao, Zhen Jia, Lei Wang, Yuqing Zhu, Chunjie Luo, Yingjie Shi, Yongqiang He, Shiming Gong, Xiaona Li, Shujie Zhang, Bizhu Qiu, Lixin Zhang, Jianfeng Zhan INSTITUTE OFTECHNOLOGY COMPUTING http://prof.ict.ac.cn/ICTBench 1 Acknowledgements This work is supported by the Chinese 973 project (Grant No.2011CB302502), the Hi- Tech Research and Development (863) Program of China (Grant No.2011AA01A203, No.2013AA01A213), the NSFC project (Grant No.60933003, No.61202075) , the BNSFproject (Grant No.4133081), and Huawei funding. 2/ Big Data Benchmarking Workshop Publications BigDataBench: a Big Data Benchmark Suite from Web Search Engines. Wanling Gao, et al. The Third Workshop on Architectures and Systems for Big Data (ASBD 2013) in conjunction with ISCA 2013. Characterizing Data Analysis Workloads in Data Centers. Zhen Jia, et al. 2013 IEEE International Symposium on Workload Characterization (IISWC-2013) Characterizing OS behavior of Scale-out Data Center Workloads. Chen Zheng et al. Seventh Annual Workshop on the Interaction amongst Virtualization, Operating Systems and Computer Architecture (WIVOSCA 2013). In Conjunction with ISCA 2013.[ Characterization of Real Workloads of Web Search Engines. Huafeng Xi et al. 2011 IEEE International Symposium on Workload Characterization (IISWC-2011). The Implications of Diverse Applications and Scalable Data Sets in Benchmarking Big Data Systems. Zhen Jia et al. Second workshop of big data benchmarking (WBDB 2012 India) & Lecture Note in Computer -

An Experimental Evaluation of Datacenter Workloads on Low-Power Embedded Micro Servers

An Experimental Evaluation of Datacenter Workloads On Low-Power Embedded Micro Servers Yiran Zhao, Shen Li, Shaohan Hu, Hongwei Wang Shuochao Yao, Huajie Shao, Tarek Abdelzaher Department of Computer Science University of Illinois at Urbana-Champaign fzhao97, shenli3, shu17, hwang172, syao9, hshao5, [email protected] ABSTRACT To reduce datacenter energy cost, power proportional- This paper presents a comprehensive evaluation of an ultra- ity [47] is one major solution studied and pursued by both low power cluster, built upon the Intel Edison based micro academia and industry. Ideally, it allows datacenter power servers. The improved performance and high energy effi- draw to proportionally follow the fluctuating amount of work- ciency of micro servers have driven both academia and in- load, thus saving energy during non-peak hours. However, dustry to explore the possibility of replacing conventional current high-end servers are not energy-proportional and brawny servers with a larger swarm of embedded micro ser- have narrow power spectrum between idling and full uti- vers. Existing attempts mostly focus on mobile-class mi- lization [43], which is far from ideal. Therefore, researchers cro servers, whose capacities are similar to mobile phones. try to improve energy-proportionality using solutions such We, on the other hand, target on sensor-class micro servers, as dynamic provisioning and CPU power scaling. The for- which are originally intended for uses in wearable technolo- mer relies on techniques such as Wake-On-LAN [36] and gies, sensor networks, and Internet-of-Things. Although VM migration [24] to power on/off servers remotely and dy- sensor-class micro servers have much less capacity, they are namically. -

Adaptive Control of Apache Web Server

Adaptive Control of Apache Web Server Erik Reed Abe Ishihara Ole J. Mengshoel Carnegie Mellon University Carnegie Mellon University Carnegie Mellon University Moffett Field, CA 94035 Moffett Field, CA 94035 Moffett Field, CA 94035 [email protected] [email protected] [email protected] Abstract least load. Typical implementations of load balancing deal with round robin balancing for domain name service Traffic to a Web site can vary dramatically. At the same (DNS) [7]. Much of existing frameworks and previous time it is highly desirable that a Web site is reactive. To research deal with inter-server connections and balanc- provide crisp interaction on thin clients, 150 milliseconds ing, with little or no focus on dynamic parameter adjust- has been suggested as an upper bound on response time. ment of individual servers. Unfortunately, the popular Apache Web server is lim- Focusing on an individual Web server rather than a ited in its capabilities to be reactive under varying traf- cluster of machines, we investigate in this paper an alter- fic. To address this problem, we design in this paper an native approach to ensuring quick and predictable user adaptive controller for the Apache Web server. A modi- response, namely feedback control and specifically Min- fied recursive least squares algorithm is used to identify imum Degree Pole Placement control [5]. This can be in system dynamics and a minimum degree pole placement an environment where inter-server load balancing is al- controller is implemented to adjust the maximum num- ready in place, or when a single server is handling Web ber of concurrent connections. -

Energy Efficiency of Server Virtualization

Energy Efficiency of Server Virtualization Jukka Kommeri Tapio Niemi Olli Helin Helsinki Institute of Physics, Helsinki Institute of Physics, Helsinki Institute of Physics, Technology program, CERN, Technology program, CERN, Technology program, CERN, CH-1211 Geneva 23, Switzerland CH-1211Geneva 23, Switzerland CH-1211 Geneva 23, Switzerland [email protected] [email protected] [email protected] Abstract—The need for computing power keeps on growing. combine several services into one physical server. In this The rising energy expenses of data centers have made server way, these technologies make it possible to take better consolidation and virtualization important research areas. advantage of hardware resources. Virtualization and its performance have received a lot of attention and several studies can be found on performance. In this study, we focus on energy efficiency of different So far researches have not studied the overall performance virtualization technologies. Our aim is to help the system and energy efficiency of server consolidation. In this paper we administrator to decide how services should be consolidated study the effect of server consolidation on energy efficiency with to minimize energy consumption without violating quality an emphasis on quality of service. We have studied this with of service agreements. several synthetic benchmarks and with realistic server load by performing a large set of measurements. We found out that We studied energy consumption of virtualized servers with energy-efficiency depends on the load of the virtualized service two open source virtualization solutions; KVM and Xen. and the number of virtualized servers. Idle virtual servers do They were tested both under load and idle. -

Remote Profiling of Resource Constraints of Web Servers Using

Remote Profiling of Resource Constraints of Web Servers Using Mini-Flash Crowds Pratap Ramamurthy Vyas Sekar Aditya Akella Balachander Krishnamurthy UW-Madison CMU UW-Madison AT&T–Labs Research Anees Shaikh IBM Research Abstract often limited, this can be difficult. Hence, large providers Unexpected surges in Web request traffic can exercise who can afford it typically resort to over-provisioning, or server-side resources (e.g., access bandwidth, process- employ techniques such as distributed content delivery or ing, storage etc.) in undesirable ways. Administra- dynamic server provisioning, to minimize the impact of tors today do not have requisite tools to understand the unexpected surges in request traffic. Smaller application impact of such “flash crowds” on their servers. Most providers may trade-off robustness to large variations in Web servers either rely on over-provisioning and admis- workload for a less expensive infrastructure that is provi- sion control, or use potentially expensive solutions like sioned for the expected common case. CDNs, to ensure high availability in the face of flash This approach still leaves operators without a sense crowds. A more fine-grained understanding of the per- of how their application infrastructure will handle large formance of individual server resources under emulated increases in traffic, due to planned events such as annual but realistic and controlled flash crowd-like conditions sales or Web casts, or unexpected flash crowds. While can aid administrators to make more efficient resource these events may not occur frequently, the inability of the management decisions. In this paper, we present mini- infrastructure to maintain reasonably good service, or at flash crowds (MFC) – a light-weight profiling service least degrade gracefully, can lead to significant loss of that reveals resource bottlenecks in a Web server infras- revenue and dissatisfied users. -

Optimal Power Allocation in Server Farms

Optimal Power Allocation in Server Farms Anshul Gandhi∗ Mor Harchol-Balter∗ Rajarshi Das† Charles Lefurgy†† March 2009 CMU-CS-09-113 School of Computer Science Carnegie Mellon University Pittsburgh, PA 15213 ∗School of Computer Science, Carnegie Mellon University, Pittsburgh, PA, USA †IBM T.J. Watson Research Center, Hawthorne, NY, USA ††IBM Research, Austin, TX, USA Research supported by NSF SMA/PDOS Grant CCR-0615262 and a 2009 IBM Faculty Award. The views and conclusions contained in this document are those of the authors and should not be interpreted as representing the official policies, either expressed or implied, of NSF or IBM. Keywords: Power Management, Server Farm, Response Time, Power-to-Frequency, Data Center Abstract Server farms today consume more than 1.5% of the total electricity in the U.S. at a cost of nearly $4.5 billion. Given the rising cost of energy, many industries are now looking for solutions on how to best make use of their available power. An important question which arises in this context is how to distribute available power among servers in a server farm so as to get maximum perfor- mance. By giving more power to a server, one can get higher server frequency (speed). Hence it is commonly believed that for a given power budget, performance can be maximized by oper- ating servers at their highest power levels. However, it is also conceivable that one might prefer to run servers at their lowest power levels, which allows more servers for a given power budget. To fully understand the effect of power allocation on performance in a server farm with a fixed power budget, we introduce a queueing theoretic model, which also allows us to predict the opti- mal power allocation in a variety of scenarios. -

User Guide Commplete 4000 Single Board Computer (IPC-623C) User Guide S000277A Revision a All Rights Reserved

MultiTech Model IPC-623C Single Board Computer for CommPlete 4000 Server User Guide CommPlete 4000 Single Board Computer (IPC-623C) User Guide S000277A Revision A All rights reserved. This publication may not be reproduced, in whole or in part, without prior expressed written permission from Multi-Tech Systems, Inc. All rights reserved. Copyright © 2002 by Multi-Tech Systems, Inc. Multi-Tech Systems, Inc. makes no representation or warranties with respect to the contents hereof and specifically disclaims any implied warranties of merchantability or fitness for any particular purpose. Furthermore, Multi-Tech Systems, Inc. reserves the right to revise this publication and to make changes from time to time in the content hereof without obligation of Multi-Tech Systems, Inc., to notify any person or organization of such revisions or changes. Record of Revisions Revision Description A Manual released (08/12/02). Patents This product is covered by one or more of the following U.S. Patent Numbers: 5.301.274, 5.309.562, 5.355.365, 5.355.653, 5.452.289, 5.453.986. Other patents Pending. Trademarks The Multi-Tech logo is a registered trademark of Multi-Tech Systems, Inc. NetWare is a registered trademark of Novell, Inc. Pentium is a registered trademark of Intel Corporation. SCO is a registered trademark of Santa Cruz Operation, Inc. UNIX is a registered trademark of X/Open Company, Ltd. Windows 95 and Windows NT are registered trademarks of Microsoft. Multi-Tech Systems, Inc. 2205 Woodale Drive Mounds View, Minnesota 55112 (763) 785-3500 or (800) 328-9717 Fax (763) 785-9874 Tech Support (800) 972-2439 Internet Address: http://www.multitech.com Table of Contents Contents Chapter 1 - Introduction ............................................................... -

Benchmarking Models and Tools for Distributed Web-Server Systems

Benchmarking Models and Tools for Distributed Web-Server Systems Mauro Andreolini1, Valeria Cardellini1, and Michele Colajanni2 1 Dept. of Computer, Systems and Production University of Roma “Tor Vergata” Roma I-00133, Italy andreolini,cardellini @ing.uniroma2.it, { } 2 Dept. of Information Engineering University of Modena Modena I-41100, Italy [email protected] Abstract. This tutorial reviews benchmarking tools and techniques that can be used to evaluate the performance and scalability of highly accessed Web-server systems. The focus is on design and testing of lo- cally and geographically distributed architectures where the performance evaluation is obtained through workload generators and analyzers in a laboratory environment. The tutorial identifies the qualities and issues of existing tools with respect to the main features that characterize a benchmarking tool (workload representation, load generation, data col- lection, output analysis and report) and their applicability to the analysis of distributed Web-server systems. 1 Introduction The explosive growth in size and usage of the Web is causing enormous strain on users, network service, and content providers.Sophisticated software components have been implemented for the provision of critical services through the Web. Consequently, many research efforts have been directed toward improving the performance of Web-based services through caching and replication solutions.A large variety of novel content delivery architectures, such as distributed Web- server systems, cooperative proxy -

NCA’04) 0-7695-2242-4/04 $ 20.00 IEEE Interesting Proposals

WALTy: A User Behavior Tailored Tool for Evaluating Web Application Performance G. Ruffo, R. Schifanella, and M. Sereno R. Politi Dipartimento di Informatica CSP Sc.a.r.l. c/o Villa Gualino Universita` degli Studi di Torino Viale Settimio Severo, 65 - 10133 Torino (ITALY) Corso Svizzera, 185 - 10149 Torino (ITALY) Abstract ticular, stressing tools make what-if analysis practical in real systems, because workload intensity can be scaled to In this paper we present WALTy (Web Application Load- analyst hypothesis, i.e., a workload emulating the activity based Testing tool), a set of tools that allows the perfor- of N users with pre-defined behaviors can be replicated, mance analysis of web applications by means of a scalable in order to monitor a set of performance parameters dur- what-if analysis on the test bed. The proposed approach is ing test. Such workload is based on sequences of object- based on a workload characterization generated from infor- requests and/or analytical characterization, but sometimes mation extracted from log files. The workload is generated they are poorly scalable by the analyst; in fact, in many by using of Customer Behavior Model Graphs (CBMG), stressing framework, we can just replicate a (set of) man- that are derived by extracting information from the web ap- ually or randomly generated sessions, losing in objectivity plication log files. In this manner the synthetic workload and representativeness. used to evaluate the web application under test is repre- The main scope of this paper is to present a methodol- sentative of the real traffic that the web application has to ogy based on the generation of a representative traffic.