Project 4: Writing a Bootloader from Scratch

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Project Log 2 2 LPC2148 USB Bootloader

Project Log 2 Project Title: USB MicroSD Card Reader EEE G512 Embedded System Design October 2018 Submitted by: Submitted to: Joy Parikh j 2016A3PS0136P Dr. Devesh Samaiya Rutwik Narendra Jain j 2015A3PS0726P 2 LPC2148 USB Bootloader The LPC2148 USB bootloader performs three steps: 1. The bootloader checks to see if a USB cable has been plugged in. If the LPC2148 detects the presence of a USB cable then it initiates a USB Mass Storage system. This will cause the target board to appear on any computer platform as a removable flash drive. The user can then seamlessly transfer files to the flash drive. In the background, the LPC2148 moves the user's files onto the SD card using the FAT16 file system. 2. The next thing the bootloader does is look for a firmware file (a file named FW.SFE). This file contains the desired operating firmware (in a binary file format) for the LPC2148 mi- croprocessor. If the bootloader finds this file on the FAT16 system then it programs the contents of this file to the flash memory of the LPC2148. In this way, the bootloader acts as a \programmer" for the LPC2148; and we can upgrade the firmware on the LPC2148 simply by loading a new file onto the micro SD card. 3. After performing the first two checks, the bootloader calls the main firmware. The main code should not even know that the bootloader was used and will run normally. 2.1 Details The USB device class used is MSCD (Mass Storage Class Device). The MSCD presents easy integration with PC's operating systems. -

Hacker's Handbook for Ringzer0 Training, by Steve Lord

Hacker’s Handbook For Ringzer0 Training, by Steve Lord This work is licensed under a Creative Commons Attribution-NonCommercial-ShareAlike 4.0 International License. Copyright ©2021 Raw Hex Ltd. All Rights Reserved. Retro Zer0 is a trademark of Ring Zer0 Training. Raw Hex is a trademark of Raw Hex Ltd. All other trademarks are the property of their respective owners. Raw Hex Ltd reserve the right to make changes or improvements to equipment, software and documentation herein described at any time and without notice. Notice: Please be advised that your Retro Zer0 has no warranty, and that tampering with the internal hardware and software of your Ring Zer0 is widely encouraged as long as you do so with appropriate regard to safety. Contents 1 Preface 5 1.1 Safety ........................... 6 1.2 Understanding This Document ............ 6 2 Before You Start 7 2.1 Check You Have Everything .............. 7 2.2 Back Up The SD Card ................. 8 2.3 Connecting Up Your Retro Zer0 ............ 8 2.4 Powering Up ....................... 10 2.5 Resetting Your Retro Zer0 . 10 2.6 Powering Down ..................... 10 3 First Steps 11 3 4 CONTENTS 3.1 Testing The Keyboard . 11 3.2 Using CP/M ....................... 12 3.3 Would You Like To Play A Game? . 14 3.4 MultiCPM Extras ..................... 17 3.5 Useful Tools ....................... 19 3.6 What’s On The Card? . 20 3.7 Putting It All Together . 23 3.8 Where To Read More . 25 4 Being Productive With Retro Zer0 27 4.1 WordStar .........................27 4.2 Supercalc .........................30 4.3 DBase ...........................32 4.4 Microsoft BASIC .....................32 4.5 Turbo Pascal .......................34 4.6 Forth 83 .........................36 4.7 ZDE ............................38 4.8 Z80 Assembler .....................39 4.9 Hi-Tech C .........................43 4.10 XLisp ...........................46 CONTENTS 5 4.11 Installing New Software . -

Operating System Boot from Fully Encrypted Device

MASARYK UNIVERSITY FACULTY OF INFORMATICS Operating system boot from fully encrypted device BACHELOR'S THESIS Daniel Chromik Brno, Fall 2016 Replace this page with a copy of the official signed thesis assignment and the copy of the Statement of an Author. Declaration Hereby I declare that this paper is my original authorial work, which I have worked out by my own. All sources, references and literature used or excerpted during elaboration of this work are properly cited and listed in complete reference to the due source. Daniel Chromik Advisor: ing. Milan Brož i Acknowledgement I would like to thank my advisor, Ing. Milan Brož, for his guidance and his patience of a saint. Another round of thanks I would like to send towards my family and friends for their support. ii Abstract The goal of this work is description of existing solutions for boot• ing Linux and Windows from fully encrypted devices with Secure Boot. Before that, though, early boot process and bootloaders are de• scribed. A simple Linux distribution is then set up to boot from a fully encrypted device. And lastly, existing Windows encryption solutions are described. iii Keywords boot process, Linux, Windows, disk encryption, GRUB 2, LUKS iv Contents 1 Introduction 1 1.1 Thesis goals 1 1.2 Thesis structure 2 2 Boot Process Description 3 2.1 Early Boot Process 3 2.2 Firmware interfaces 4 2.2.1 BIOS - Basic Input/Output System 4 2.2.2 UEFI - Unified Extended Firmware Interface . 5 2.3 Partitioning tables 5 2.3.1 MBR - Master Boot Record 5 2.3.2 GPT - GUID Partition Table 7 2.4 -

Partition Wizard About Minitool Partition Wizard Minitool Partition Wizard Is an Easy-To-Use Partitioning Software with High Security and Efficiency

MiniTool Partition Wizard About MiniTool Partition Wizard MiniTool Partition Wizard is an easy-to-use partitioning software with high security and efficiency. Due of its simple user interface, you can create, delete, format, move, and resize partitions with ease. What’s more, your data will always be protected when using MiniTool Partition Wizard to move and resize partitions. Main Functions of MiniTool Partition Wizard: Resize/ Move partitions Merge Partitions Create partitions Delete partitions Change Partition Label Delete all partitions Format partitions Change Cluster Size Convert file system Convert FAT to NTFS Convert NTFS to FAT Explore Partition Check Partitions Recovery Partition Wipe disk Wipe partition Copy partition Copy disks Initialize to MBR disk Initialize to GPT disk Align All Partitions Align Partition Convert MBR Disk to GPT Disk Convert GPT Disk to MBR Disk Dynamic Disk Create volume Delete Volume Format Volume Move/Resize Volume Wipe Volume Explore Volume Check File System Change Volume Label Change Volume Letter Change Volume Cluster Size Volume Properties MiniTool Partition Wizard Staring MiniTool Partition Wizard You can start MiniTool Partition Wizard from the Start menu in Windows Click Start menu > All Programs > MiniTool Partition Wizard xxx Edition > MiniTool Partition Wizard xxx Edition Xxx is your present edition of MiniTool Partition Wizard, Such as Home, Professional, Server, and Enterprise MiniTool Partition Wizard Hardware Requirements Minimum Hardware requirements: 500 MHz x86 or compatible CPU. 256mb RAM memory. Mouse and Keyboard. Recommended Hardware requirements: 1 GHz x86 or compatible CPU. 512mb RAM memory. Mouse and Keyboard. MiniTool Partition Wizard System Requirements Note: you should have access to administration while using Partition Wizard. -

Chapter 3. Booting Operating Systems

Chapter 3. Booting Operating Systems Abstract: Chapter 3 provides a complete coverage on operating systems booting. It explains the booting principle and the booting sequence of various kinds of bootable devices. These include booting from floppy disk, hard disk, CDROM and USB drives. Instead of writing a customized booter to boot up only MTX, it shows how to develop booter programs to boot up real operating systems, such as Linux, from a variety of bootable devices. In particular, it shows how to boot up generic Linux bzImage kernels with initial ramdisk support. It is shown that the hard disk and CDROM booters developed in this book are comparable to GRUB and isolinux in performance. In addition, it demonstrates the booter programs by sample systems. 3.1. Booting Booting, which is short for bootstrap, refers to the process of loading an operating system image into computer memory and starting up the operating system. As such, it is the first step to run an operating system. Despite its importance and widespread interests among computer users, the subject of booting is rarely discussed in operating system books. Information on booting are usually scattered and, in most cases, incomplete. A systematic treatment of the booting process has been lacking. The purpose of this chapter is to try to fill this void. In this chapter, we shall discuss the booting principle and show how to write booter programs to boot up real operating systems. As one might expect, the booting process is highly machine dependent. To be more specific, we shall only consider the booting process of Intel x86 based PCs. -

Computer Hardware

Chapter Computer Hardware ENCE EXAM TOPICS COVERED IN 1 THIS CHAPTER: ✓ Computer hardware components ✓ The boot process ✓ Partitions ✓ File systems COPYRIGHTED MATERIAL Computer forensics examiners deal most often with the media on which evidentiary data is stored. This includes, but is not lim- ited to, hard drives, CDs, DVDs, fl ash memory devices, smart phones, tablets, and even legacy fl oppies and tapes. Although these devices might be the bane of the examiner’s existence, media devices don’t exist in a void, and knowledge of a computer’s various components and functions is a must for the competent examiner. As an examiner, you may be called upon to explain how a computer functions to a jury. Doing so requires you know a computer’s function from a technical standpoint and that you can translate those technical concepts into real-world, easy-to-understand terms. As an examiner, you may also be subjected to a voir dire examination by opposing coun- sel to challenge your competence to testify. Acronyms are hardly in short supply in the fi eld of computing—some well-known and meaningful, others more obscure. Imagine being asked during such an examination to explain several of the common acronyms used with computers, such as RAM, CMOS, SCSI, BIOS, and POST. If you were to draw a blank on some obscure or even common acronym, picture its impact on your credibility. Some acronyms are difficult to remember because their meaning is often obscure or meaningless. A good example is TWAIN, which stands for T ech- nology W ithout a n I nteresting N ame. -

UG103.6: Bootloader Fundamentals

UG103.6: Bootloader Fundamentals This document introduces bootloading for Silicon Labs network- ing devices. It describes the concepts of standalone and applica- KEY POINTS tion bootloaders and discusses their relative strengths and weak- • Introduces the Gecko Bootloader. nesses. In addition, it looks at design and implementation details • Summarizes the key features the for each method. Finally, it describes the bootloader file format. bootloaders support and the design decisions associated with selecting a Silicon Labs’ Fundamentals series covers topics that project managers, application de- bootloader. signers, and developers should understand before beginning to work on an embedded • Describes bootloader file formats. networking solution using Silicon Labs chips, networking stacks such as EmberZNet PRO or Silicon Labs Bluetooth®, and associated development tools. The documents can be used as a starting place for anyone needing an introduction to developing wire- less networking applications, or who is new to the Silicon Labs development environ- ment. silabs.com | Building a more connected world. Rev. 1.7 UG103.6: Bootloader Fundamentals Introduction 1. Introduction The bootloader is a program stored in reserved flash memory that can initialize a device, update firmware images, and possibly perform some integrity checks. Firmware image update occurs on demand, either by serial communication or over the air. Production-level pro- gramming is typically done during the product manufacturing process yet it is desirable to be able to reprogram the system after produc- tion is complete. More importantly, it is valuable to be able to update the device's firmware with new features and bug fixes after deploy- ment. The firmware image update capability makes that possible. -

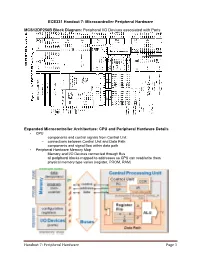

Memory Map: 68HC12 CPU and MC9S12DP256B Evaluation Board

ECE331 Handout 7: Microcontroller Peripheral Hardware MCS12DP256B Block Diagram: Peripheral I/O Devices associated with Ports Expanded Microcontroller Architecture: CPU and Peripheral Hardware Details • CPU – components and control signals from Control Unit – connections between Control Unit and Data Path – components and signal flow within data path • Peripheral Hardware Memory Map – Memory and I/O Devices connected through Bus – all peripheral blocks mapped to addresses so CPU can read/write them – physical memory type varies (register, PROM, RAM) Handout 7: Peripheral Hardware Page 1 Memory Map: 68HCS12 CPU and MC9S12DP256B Evaluation Board Configuration Register Set Physical Memory Handout 7: Peripheral Hardware Page 2 Handout 7: Peripheral Hardware Page 3 HCS12 Modes of Operation MODC MODB MODA Mode Port A Port B 0 0 0 special single chip G.P. I/O G.P. I/O special expanded 0 0 1 narrow Addr/Data Addr 0 1 0 special peripheral Addr/Data Addr/Data 0 1 1 special expanded wide Addr/Data Addr/Data 1 0 0 normal single chip G.P. I/O G.P. I/O normal expanded 1 0 1 narrow Addr/Data Addr 1 1 0 reserved -- -- 1 1 1 normal expanded wide Addr/Data Addr/Data G.P. = general purpose HCS12 Ports for Expanded Modes Handout 7: Peripheral Hardware Page 4 Memory Basics •RAM: Random Access Memory – historically defined as memory array with individual bit access – refers to memory with both Read and Write capabilities •ROM: Read Only Memory – no capabilities for “online” memory Write operations – Write typically requires high voltages or erasing by UV light • Volatility of Memory – volatile memory loses data over time or when power is removed • RAM is volatile – non-volatile memory stores date even when power is removed • ROM is no n-vltilvolatile • Static vs. -

USART Protocol Used in the STM32 Bootloader

AN3155 Application note USART protocol used in the STM32 bootloader Introduction This application note describes the USART protocol used in the STM32 microcontroller bootloader, providing details on each supported command. This document applies to STM32 products embedding any bootloader version, as specified in application note AN2606 STM32 system memory boot mode, available on www.st.com. These products are listed in Table 1, and are referred to as STM32 throughout the document. For more information about the USART hardware resources and requirements for your device bootloader, refer to the already mentioned AN2606. Table 1. Applicable products Type Product series STM32F0 Series STM32F1 Series STM32F2 Series STM32F3 Series STM32F4 Series STM32F7 Series STM32G0 Series Microcontrollers STM32G4 Series STM32H7 Series STM32L0 Series STM32L1 Series STM32L4 Series STM32L5 Series STM32WB Series STM32WL Series June 2021 AN3155 Rev 14 1/48 www.st.com 1 Contents AN3155 Contents 1 USART bootloader code sequence . 5 2 Choosing the USARTx baud rate . 6 2.1 Minimum baud rate . 6 2.2 Maximum baud rate . 6 3 Bootloader command set . 7 3.1 Get command . 8 3.2 Get Version & Read Protection Status command . 10 3.3 Get ID command . 12 3.4 Read Memory command . 13 3.5 Go command . 16 3.6 Write Memory command . 18 3.7 Erase Memory command . 21 3.8 Extended Erase Memory command . 24 3.9 Write Protect command . 27 3.10 Write Unprotect command . 30 3.11 Readout Protect command . 31 3.12 Readout Unprotect command . 33 3.13 Get Checksum command . 35 3.14 Special command . 39 3.15 Extended Special command . -

USB Mass Storage Device (MSD) Bootloader

Freescale Semiconductor Document Number: AN4379 Application Note Rev. 0, October 2011 Freescale USB Mass Storage Device Bootloader by: Derek Snell Freescale Contents 1 Introduction 1 Introduction................................................................1 Freescale offers a broad selection of microcontrollers that 2 Functional description...............................................2 feature universal serial bus (USB) access. A product with a 3 Using the bootloader.................................................9 USB port allows very easy field updates of the firmware. This application note describes a mass storage device (MSD) USB 4 Porting USB MSD device bootloader to bootloader that has been written to work with several other platforms.........................................................13 Freescale USB families. A device with this bootloader is 5 Developing new applications..................................15 connected to a host computer, and the bootloader enumerates as a new drive. The new firmware is copied onto this drive, 6 Conclusion...............................................................20 and the device reprograms itself. Freescale does offer other bootloaders. For example, application note AN3561, "USB Bootloader for the MC9S08JM60," describes a USB bootloader that was written for the Flexis JM family. The MSD bootloader described in this application note is offered as another option, and has these advantages: • It does not require a driver to be installed on the host. • It does not require an application to run on the host. • Any user can use it with a little training. The only action required is to copy a file onto a drive. • It can be used with many different host operating systems since it requires no host software or driver This bootloader was specifically written for several families of Freescale microcontrollers that share similar USB peripherals. These families include, but are not limited to, the following: • Flexis JM family MCF51JM © 2011 Freescale Semiconductor, Inc. -

Lecture 5: Feb 4Th, 2020 5.1 OS Boot Process

CMPSCI 577 Operating Systems Design and Implementation Spring 2020 Lecture 5: Feb 4th, 2020 Lecturer: Prashant Shenoy Scribe: Serena Chan 5.1 OS Boot Process While seemingly mundane and not directly relevant to the modifications we will be making in this course, understanding the OS boot process is important for modifying the kernel. There are six steps that take the machine to a running state from when it is first turned on. 5.1.1 Step 1: BIOS (Basic Input/Output System) The BIOS is a small piece of code that lives in the firmware and is the first software that runs upon boot. When the computer is turned on, the BIOS runs the Power-on Self Test, where the RAM is initialized and hardware such as disks and peripherals are identified and checked. Once the disk is found, the BIOSwill start the boot process from the disk (‘bootstrapping’). The BIOS is often stored on EEPROM/ROM (read-only memory); because of its hardware-specific nature, it is not designed to be easily user modifiable. In addition, since the BIOS is the lowest level of softwarein the PC, it also acts as an interface for the OS to perform I/O and communicate with hardware. 5.1.2 Step 2: MBR (Master Boot Record) The MDR is the first 512 bytes of memory and consists of three components. In particular, thefirst440 bytes contain the bootstrap code that is used to continue the boot process, or the 1st stage boot loader; this is executed by the BIOS. The functionality of the code is to simply search through the partition table and find the root partition, where is where the OS resides. -

Wikipedia: Design of the FAT File System

Design of the FAT file system A FAT file system is a specific type of computer file system architecture and FAT a family of industry-standard file systems utilizing it. Developer(s) Microsoft, SCP, IBM, [3] The FAT file system is a legacy file system which is simple and robust. It Compaq, Digital offers good performance even in very light-weight implementations, but Research, Novell, cannot deliver the same performance, reliability and scalability as some Caldera modern file systems. It is, however, supported for compatibility reasons by Full name File Allocation Table: nearly all currently developed operating systems for personal computers and FAT12 (12- many home computers, mobile devices and embedded systems, and thus is a bit version), well suited format for data exchange between computers and devices of almost FAT16 (16- any type and age from 1981 through the present. bit versions), Originally designed in 1977 for use on floppy disks, FAT was soon adapted and FAT32 (32-bit version used almost universally on hard disks throughout the DOS and Windows 9x with 28 bits used), eras for two decades. Today, FAT file systems are still commonly found on exFAT (64- floppy disks, USB sticks, flash and other solid-state memory cards and bit versions) modules, and many portable and embedded devices. DCF implements FAT as Introduced 1977 (Standalone the standard file system for digital cameras since 1998.[4] FAT is also utilized Disk BASIC-80) for the EFI system partition (partition type 0xEF) in the boot stage of EFI- FAT12: August 1980 compliant computers. (SCP QDOS) FAT16: August 1984 For floppy disks, FAT has been standardized as ECMA-107[5] and (IBM PC DOS 3.0) ISO/IEC 9293:1994[6] (superseding ISO 9293:1987[7]).