Epitaxial Lift-Off Process for Gallium Arsenide Substrate Reuse and flexible Electronics

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

A Guide to Export Controls

Foreign Affairs, Trade and Affaires étrangères, Commerce et Development Canada Développment Canada A Guide To CANADA’S EXPORT CONTROLS December 2012 Introduction The issuance of export permits is administered by the Export Controls Division (TIE) of Foreign Affairs, Trade and Development Canada (DFATD). TIE provides assistance to exporters in determining if export permits are required. It also publishes brochures and Notices to Exporters that are freely available on request and on our website www.exportcontrols.gc.ca. How to contact us: Export Controls Division (TIE) Foreign Affairs, Trade and Development Canada 111 Sussex Drive Ottawa, Ontario K1A 0G2 Telephone: (613) 996-2387 Facsimile: (613) 996-9933 Email: [email protected] For information on how to apply for an export permit and additional information on export controls please refer to our website. To enquire on the status of an export permit application: Recognized EXCOL users can check the status of an export permit application on-line. Non-recognized users can call (613) 996-2387 or email [email protected] and quote your export permit application identification (ref ID) number. Export Controls Division website: www.exportcontrols.gc.ca This Guide, at time of publication, encompasses the list of items enumerated on the Export Control List (ECL) that are controlled for export in accordance with Canadian foreign policy, including Canada’s participation in multilateral export control regimes and bilateral agreements. Unless otherwise specified, the export controls contained in this Guide apply to all destinations except the United States. Canada’s Export Control List can be found at the Department of Justice website at http://canada.justice.gc.ca/. -

TSMC DAY at MIT 7 MTL DAY at FOXCONN 8 MTL DAY at TEXAS INSTRUMENTS MTL Teams with the DSP MEDICAL ELECTRONIC SYSTEMS Leadership University Program

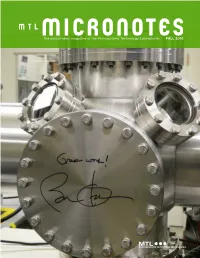

The annual news magazine of the Microsystems Technology Laboratories FALL 2010 microsystems technology laboratories CONTENTS COLLABORATION AT ITS BEST 1 NOTES FROM THE DIRECTOR page 24 NEWS & EVENTS 2 MTL’S NEW FACULTY Introducing Li-Shiuan Peh & Dana Weinstein. 3 FOXCONN JOINS MIG 4 APPLIED MATERIALS Interactions with MTL in & out of the Fab. 5 BORN IN THE WRONG PLACE Andrea Cuomo of STMicroelectronics shares his company’s unique history. 6 TSMC DAY AT MIT 7 MTL DAY AT FOXCONN 8 MTL DAY AT TEXAS INSTRUMENTS MTL teams with the DSP MEDICAL ELECTRONIC SYSTEMS Leadership University Program. page 30 9 SAMSUNG DAY AT MTL; DR. CHANG-GYU HWANG 10 MIT & MASDAR INSTITUTE MIT & Masdar Institute develop microsystems education & research in the Middle East. 12 MARC2010 13 ENERGY RESEARCHERS FIND OBAMA AN EAGER STUDENT President showed keen interest, quick understanding and warm appreciation, say his hosts. 14 IN THE NEWS 40 GRADUATION WOMEN IN ENGINEERING FEATURE STORIES page 34 24 COLLABORATION AT ITS BEST Everyone wins when MTL and industry join forces. 30 MEDICAL ELECTRONIC SYSTEMS Can Boston become the “Silicon Valley of Medical Electronic Systems?” MTL researchers are working hard to make it happen. WOMEN IN ENGINEERING MIT’s Women’s Technology Program. ON THE COVER 34 Detail of President Barack Obama’s RESEARCH signature on a vacuum pump located in 16 MECHANICAL DEVICES STAMPED ON PLASTIC the Bulovic lab. Microelectromechanical devices gave us the Wii and the digital movie projector. MIT researchers have found a new way to make them. Photo courtesy, Bulovic lab. 18 STRAINING FORWARD Nanowires made of ‘strained silicon’— silicon whose atoms have been pried slightly apart — show how to keep increases in computer power coming. -

RLE Currents | December 1988 (8.9Mb PDF)

Volume 2, Number 1 " December 1988 The Research Laboratory of Electronics at the Massachusetts Institute of Technology MATERIALS RESEARCH: Meeting the Challenge of Microelectronics Technology Since the discovery of the transis- tor at Bell Laboratories in 1947, scien- tists have been challenged by the need to produce materials for highly minia- turized and increasingly fast micro- electronic components. Driven by the technology of the information age, sci- entists have examined the unique properties of semiconductors, funda- mentally exploited new combinations of these novel materials, and devel- oped innovative design techniques to miniaturize electronic components. At the heart of this research is the ever- shrinking and exceedingly complex in- tegrated circuit microchip. In addition, the development of microscaled tran- sistors and other electronic compo- nents has resulted in systems with larg- er and faster capabilities, particularly for information processing and high- speed communication. I Every year since 1960, the number of circuit components on the most ad- Professor Henry I. Smith e.p loins the development of an alignment ststemJbr x-ray vanced microchip has nearly doubled. nanolithography that should be capable of 100-angstrom precision. Under his direction. Today, over 4 million transistors can be RLE's Submicron Structures Laboratory has pioneered new technologies in submicron onto one packed neatly computer structuresfabrication and explored deep -submicron MOSPETs and the exciting new memory or DRAM random (dynamic field of quantum-effect electronics (see related article on page 7.). Working with Prqfes- access memory) chip. The dramatic sor Dimitri Antoniadis and graduate student Ghavam Shahidi, dx. have discovered that miniaturization of electronic compo- the deleterious hot- electron effects seen in silicon MOSFETs with channel lengths below nents over the last forty years has raised 0.25 microns actually decrease at linewidths below 0.15 microns. -

IBM Research Report SOI Series MOSFET for Embedded High

RC24545 (W0805-007) May 1, 2008 Electrical Engineering IBM Research Report SOI Series MOSFET for Embedded High Voltage Applications and Soft-Error Immunity Jin Cai, Tak Ning, Philip Oldiges*, Anthony Chou*, Arvind Kumar*, Werner Rausch*, Wilfried Haensch, Ghavam Shahidi IBM Research Division Thomas J. Watson Research Center P.O. Box 218 Yorktown Heights, NY 10598 *IBM Semiconductor Research & Development Center Hopewell Junction, NY 12533 Research Division Almaden - Austin - Beijing - Cambridge - Haifa - India - T. J. Watson - Tokyo - Zurich LIMITED DISTRIBUTION NOTICE: This report has been submitted for publication outside of IBM and will probably be copyrighted if accepted for publication. It has been issued as a Research Report for early dissemination of its contents. In view of the transfer of copyright to the outside publisher, its distribution outside of IBM prior to publication should be limited to peer communications and specific requests. After outside publication, requests should be filled only by reprints or legally obtained copies of the article (e.g. , payment of royalties). Copies may be requested from IBM T. J. Watson Research Center , P. O. Box 218, Yorktown Heights, NY 10598 USA (email: [email protected]). Some reports are available on the internet at http://domino.watson.ibm.com/library/CyberDig.nsf/home . SOI Series MOSFET for Embedded High Voltage Applications and Soft-Error Immunity Jin Cai, Tak Ning, Philip Oldiges*, Anthony Chou*, Arvind Kumar*, Werner Rausch*, Wilfried Haensch and Ghavam Shahidi IBM Research Division, T. J. Watson Research Center, Yorktown Heights, NY 10598 * IBM Semiconductor Research & Development Center, Hopewell Junction, NY 12533 Phone: 914-945-2310; Fax: 914-945-2141; E-mail: [email protected]. -

Electrical Characterization of Sub-30Nm Gatelength SOI Mosfets Terence Kane, Michael P

Proceedings from the 30th International Symposium for Testing and Failure Analysis, November 14-18, 2004 Worcester, Massachusetts Electrical Characterization of sub-30nm Gatelength SOI MOSFETs Terence Kane, Michael P. Tenney IBM Microelectronics, Hopewell Junction, New York Abstract manufacturing but also for discrete device electrical characterization. Demonstrations of sub 20nm gate length MOSFET devices According to the 2003 International Technology Roadmap for involving various FEOL (front end of line) schemes such as high performance logic [5] development of UT-SOI MOSFET Silicon On DEpletion Layer (SODEL) FET’s, asymmetric- devices is fairly advanced at the 65 nm nodes. This is shown gate FinFET devices, planar Ultra-thin body SOI (UTSOI) in TABLE I. [5] FET’s, and, more recently, independently oriented surface channels for (110) pMOS and (100) nMOS described as Table 1: 2003 ITRS Roadmap for High Performance Logic[5] Simplified Hybrid Orientation Technology (SHOT).[1-4, 7- 18] have been reported. SHOT FEOL integration for FinFETs can be combined on the same wafer as planar PDSOI and UTSOI MOSFETs [18]. According to International Technology Roadmap for Semiconductors (ITRS) guidelines [5] 20nm silicon layers with +/-5%, 6V uniformity will be needed in 2004 timeframe[8] to guarantee threshold voltage ( Vt ) control [6]. Bonded Silicon on Insulator (SOI) processes that achieve +/- 10 A film thickness have been shown [6] for these Ultra-Thin SOI (UT-SOI) devices at the 65nm node and beyond. UT- SOI devices combined with SHOT (110) pMOS and (100) nMOS oriented surface channels offer optimizeed channel carrier mobility as well meeting issues of threshold voltage levels[4-18]. -

Modelling and Optimising Gaas/Al (X) Ga (1-X) As Multiple Quantum Well

University of London Imperial College of Science, Technology and Medicine Department of Physics Modelling and Optimising GaAs/AlxGa1 xAs − Multiple Quantum Well Solar Cells James P. Connolly arXiv:1006.1053v1 [cond-mat.mes-hall] 5 Jun 2010 Submitted in part fulfilment of the requirements for the degree of Doctor of Philosophy in Science of the University of London and the Diploma of Imperial College, January 1997 2 Abstract The quantum well solar cell (QWSC) is a p - i - n solar cell with quantum wells in the intrinsic region. Previous work has shown that QWSCs have a greater open circuit voltage (Voc) than would be provided by a cell with the quantum well effective bandgap. This suggests that the fundamental efficiency limits of QWSCs are greater than those of single bandgap solar cells. The following work investigates QWSCs in the GaAs/AlxGa1−xAs materials system. The design and optimisation of a QWSC in this system requires studies of the voltage and current dependencies on the aluminium fraction. QWSCs with different aluminium fractions have been studied and show an increasing Voc with increasing barrier aluminium composition. The QE however decreases with increasing aluminium composition. We de- velop a model of the QE to test novel QWSC designs with a view to minimising this problem. This work concentrates on two design changes. The first deals with com- positionally graded structures in which the bandgap varies with position. This bandgap variation introduces an quasi electric field which can be used to increase minority carrier collection in the low efficiency p and n layers. This technique also increases the light flux reaching the highly efficient depletion regions. -

Determination of Band Structure of Gallium-Arsenide and Aluminium-Arsenide Using Density Functional Theory

Computational Chemistry, 2016, 4, 73-82 Published Online July 2016 in SciRes. http://www.scirp.org/journal/cc http://dx.doi.org/10.4236/cc.2016.43007 Determination of Band Structure of Gallium-Arsenide and Aluminium-Arsenide Using Density Functional Theory J. A. Owolabi1, M. Y. Onimisi1, S. G. Abdu2, G. O. Olowomofe1 1Department of Physics, Nigerian Defence Academy, Kaduna, Nigeria 2Department of Physics, Kaduna State University, Kaduna, Nigeria Received 18 April 2016; accepted 2 July 2016; published 5 July 2016 Copyright © 2016 by authors and Scientific Research Publishing Inc. This work is licensed under the Creative Commons Attribution International License (CC BY). http://creativecommons.org/licenses/by/4.0/ Abstract This research paper is on Density Functional Theory (DFT) within Local Density Approximation. The calculation was performed using Fritz Haber Institute Ab-initio Molecular Simulations (FHI- AIMS) code based on numerical atomic-centered orbital basis sets. The electronic band struc- ture, total density of state (DOS) and band gap energy were calculated for Gallium-Arsenide and Aluminium-Arsenide in diamond structures. The result of minimum total energy and computa- tional time obtained from the experimental lattice constant 5.63 A for both Gallium Arsenide and Aluminium Arsenide is −114,915.7903 eV and 64.989 s, respectively. The electronic band structure analysis shows that Aluminium-Arsenide is an indirect band gap semiconductor while Gallium-Arsenide is a direct band gap semiconductor. The energy gap results obtained for GaAs is 0.37 eV and AlAs is 1.42 eV. The band gap in GaAs observed is very small when compared to AlAs. -

Chemical Names and CAS Numbers Final

Chemical Abstract Chemical Formula Chemical Name Service (CAS) Number C3H8O 1‐propanol C4H7BrO2 2‐bromobutyric acid 80‐58‐0 GeH3COOH 2‐germaacetic acid C4H10 2‐methylpropane 75‐28‐5 C3H8O 2‐propanol 67‐63‐0 C6H10O3 4‐acetylbutyric acid 448671 C4H7BrO2 4‐bromobutyric acid 2623‐87‐2 CH3CHO acetaldehyde CH3CONH2 acetamide C8H9NO2 acetaminophen 103‐90‐2 − C2H3O2 acetate ion − CH3COO acetate ion C2H4O2 acetic acid 64‐19‐7 CH3COOH acetic acid (CH3)2CO acetone CH3COCl acetyl chloride C2H2 acetylene 74‐86‐2 HCCH acetylene C9H8O4 acetylsalicylic acid 50‐78‐2 H2C(CH)CN acrylonitrile C3H7NO2 Ala C3H7NO2 alanine 56‐41‐7 NaAlSi3O3 albite AlSb aluminium antimonide 25152‐52‐7 AlAs aluminium arsenide 22831‐42‐1 AlBO2 aluminium borate 61279‐70‐7 AlBO aluminium boron oxide 12041‐48‐4 AlBr3 aluminium bromide 7727‐15‐3 AlBr3•6H2O aluminium bromide hexahydrate 2149397 AlCl4Cs aluminium caesium tetrachloride 17992‐03‐9 AlCl3 aluminium chloride (anhydrous) 7446‐70‐0 AlCl3•6H2O aluminium chloride hexahydrate 7784‐13‐6 AlClO aluminium chloride oxide 13596‐11‐7 AlB2 aluminium diboride 12041‐50‐8 AlF2 aluminium difluoride 13569‐23‐8 AlF2O aluminium difluoride oxide 38344‐66‐0 AlB12 aluminium dodecaboride 12041‐54‐2 Al2F6 aluminium fluoride 17949‐86‐9 AlF3 aluminium fluoride 7784‐18‐1 Al(CHO2)3 aluminium formate 7360‐53‐4 1 of 75 Chemical Abstract Chemical Formula Chemical Name Service (CAS) Number Al(OH)3 aluminium hydroxide 21645‐51‐2 Al2I6 aluminium iodide 18898‐35‐6 AlI3 aluminium iodide 7784‐23‐8 AlBr aluminium monobromide 22359‐97‐3 AlCl aluminium monochloride -

1.0 Submicron Structures Technology and Research

Submicron Structures Technology and Research 1.0 Submicron Structures Technology and Research Academic and Research Staff Prof. H.I. Smith, Dr. M.L. Schattenburg, J.M. Carter Visiting Scientists H. Kawata,1 I. Plotnik,2 I. Tanaka3 Graduate Students S. Ajuria, E.H. Anderson, H.A. Atwater, P. Bagwell, W. Chu, L. Clevenger, J. Floro, S.M. Garrison, J. Im, K. Ismail, E. Jiran, H.J. Kim, Y-C. Ku, U. Meirav, P. Meyer, A. Moel, J.E. Palmer, S.L. Park, H.M. Quek, J. Scott-Thomas, G. Shahidi, M. Toth, A.T. Yen 1.1 Submicron Structures Laboratory The Submicron Structures Laboratory at MIT develops techniques for fabricating surface structures with linewidths in the range from nanometers to micrometers, and uses these structures in a variety of research projects. These projects of the laboratory, which are described briefly below, fall into four major categories: development of submicron and nanometer fabrication technology; deep-submicron electronics and quantum-effect electronics; crystalline films on amorphous substrates; and periodic structures for x-ray optics and spectroscopy. 1.2 Microfabrication at Linewidths of 100nm and Below Joint Services Electronics Program (Contract DAALO3-86-K-0002) National Science Foundation (Grant ECS 87-09806) Erik H. Anderson, James M. Carter, William Chu, Hui M. Quek, Irving Plotnik, Mark L. Schattenburg, Anthony T. Yen, Henry I. Smith A variety of techniques for fabricating structures with characteristic dimensions of 0.1 ym (100 nm) and below are investigated. These include: x-ray nanolithography, holographic lithography, achromatic holographic lithography, electron-beam lithography, reactive-ion etching, electroplating and liftoff. -

Semiconductor and Magnetic Material 3

Semiconductor and 11 Magnetic Material 2 Electronic Devices Circuits and Applications 1.1 INTRODUCTION Semiconductors are materials having electrical conductivities between those of good conductors and insulators. Semiconductors resistivity varies from 10–5 to 10+4 m. Similarly resistivity range values 10–8 to 10+6 m for conductors and from 107 to 108 m for insulators. Germanium (Ge) and Silicon (Si) are the most commonly used semiconductors and belong to Group-IV of the periodic table. They have resistivity of about 0.6 and 1.5 × 103 m respectively. Also there are certain compound semiconductors such as gallium arsenide (GaAs), indium phosphide (InP), cadmium sulphide (CdS), etc. They are formed by the combination of the elements of groups III and V. Small band gap is another important characteristic of semiconductors. Also the semiconductors have negative temperature coefficient of resistance because the number of carriers in a semiconductor will increase significantly with temperature, resulting in reduction of the resistance of the semiconductor. 1.2 SEMICONDUCTOR MATERIALS (GROUP-IV) Semiconductors are materials having electrical conductivities between those of good conductors and insulators. The elemental semiconductor such as germanium (Ge) and silicon (Si) belong to Group-IV of the periodic table and have resistivity of about 0.6 and 1.5 × 103 cm respectively. The energy band gaps of these elements of Group-IV at 0 K are given as below: C (diamond) → 5.51 eV Ge → 0.75 eV Si → 1.16 eV Sn (grey) → 0.08 eV Pd → ≈ eV We may say from above list that at room temperature (i.e., 0 K) diamond behaves as an insulator but Ge and Si are treated as semiconductors. -

(12) United States Patent (10) Patent No.: US 6, 180,486 B1 Leobandung Et Al

USOO6180486B1 (12) United States Patent (10) Patent No.: US 6, 180,486 B1 Leobandung et al. (45) Date of Patent: *Jan. 30, 2001 (54) PROCESS OF FABRICATING PLANAR AND 5,518,949 5/1996 Chen ...................................... 437/62 DENSELY PATTERNED 5,539,240 7/1996 Cronin et al. ........................ 257/520 SILICON-ON-INSULATOR STRUCTURE 5,567,634 * 10/1996 Hebert et al. ........................ 430/270 5,598,019 1/1997 Komori et al. ...................... 257/397 5,665,619 9/1997 Kwan et al. ......................... 438/270 (75) Inventors: E.A.S.Fingers 5,811,315 * 9/1998 Yindeepol et al. .................. 438/405 Pleasantville; Dominic J. Schepis, OTHER PUBLICATIONS Wappingers Falls; Ghavam Shahidi, Elmsford, all of NY (US) Stanley Wolf Silicon Processing for the VSLI ERA vol. 2 Lattice Press pp. 52, 69, 1990.* (73) Assignee: International Business Machines “Defect-Free Silicon on Insulator by Oxidized Porous Sili Corporation, Armonk, NY (US) con” by L.A. Nesbit. IBM Technical Disclosure Bulletin. vol. 27, No. 8, Jan. 1985.p.4632. (*) Notice: This patent issued on a continued pros- “Wet Processing: Cleaining, Etching, and Liftoff by S. Wolf ecution application filed under 37 CFR Ph.D., R. N. Tauber Ph.D., Silicon Processing for the VLSI 1.53(d), and is subject to the twenty year Era. vol. 1, 1986, pp. 516-517. patent term provisions of 35 U.S.C. 154(a)(2). * cited by examiner Under 35 U.S.C. 154(b), the term of this Primary Examiner—Charles Bowers patent shall be extended for 0 days. ASSistant Examiner David S Blum (74) Attorney, Agent, or Firm-Ratner & Prestia; Joseph P. -

Strategic Goods (Control) Act (Chapter 300) Strategic Goods (Control) Order 2013

1 S 10/2013 1 First published in the Government Gazette, Electronic Edition, on 11th January 2013 at 4.00 pm. No. S 00010 STRATEGIC GOODS (CONTROL) ACT (CHAPTER 300) STRATEGIC GOODS (CONTROL) ORDER 2013 ARRANGEMENT OF PARAGRAPHS Paragraph 1. Citation and commencement 2. Strategic goods and strategic goods technology 3. Revocation The Schedule In exercise of the powers conferred by section 4A(1) of the Strategic Goods (Control) Act, the Minister for Trade and Industry hereby makes the following Order: Citation and commencement 1. This Order may be cited as the Strategic Goods (Control) Order 2013 and shall come into operation on 1st February 2013. Strategic goods and strategic goods technology 2. The goods and technology specified in the Schedule shall be strategic goods and strategic goods technology, respectively, for the purposes of the Act. Revocation 3. The Strategic Goods (Control) Order 2010 (G.N. No. S 152/2010) is revoked. S 10/2013 2 2 THE SCHEDULE Paragraph 2 PART I MILITARY GOODS THE EXPORT, TRANSHIPMENT OR BRINGING IN TRANSIT OF WHICH, AND TECHNOLOGY THE EXPORT OR TRANSMISSION OF WHICH, REQUIRE A PERMIT Division 1 — Preliminary Provisions Subdivision 1 — General Notes 1. Non-controlled goods (including plant) containing one or more controlled components set out in Division 2 shall be considered as being controlled goods within Division 2 if the controlled components are the principal element of the non-controlled goods and can feasibly be removed or used for other purposes. 2. In determining whether goods are to be considered the principal element of other goods for the purposes of paragraph 1, factors such as the quantity, value and technological know-how involved and other special circumstances which might establish the goods as the principal element of those other goods must be weighed.