Device Scaling of High Performance MOSFET with Metal Gate High-K At

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

TSMC DAY at MIT 7 MTL DAY at FOXCONN 8 MTL DAY at TEXAS INSTRUMENTS MTL Teams with the DSP MEDICAL ELECTRONIC SYSTEMS Leadership University Program

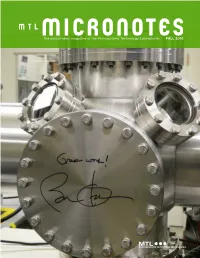

The annual news magazine of the Microsystems Technology Laboratories FALL 2010 microsystems technology laboratories CONTENTS COLLABORATION AT ITS BEST 1 NOTES FROM THE DIRECTOR page 24 NEWS & EVENTS 2 MTL’S NEW FACULTY Introducing Li-Shiuan Peh & Dana Weinstein. 3 FOXCONN JOINS MIG 4 APPLIED MATERIALS Interactions with MTL in & out of the Fab. 5 BORN IN THE WRONG PLACE Andrea Cuomo of STMicroelectronics shares his company’s unique history. 6 TSMC DAY AT MIT 7 MTL DAY AT FOXCONN 8 MTL DAY AT TEXAS INSTRUMENTS MTL teams with the DSP MEDICAL ELECTRONIC SYSTEMS Leadership University Program. page 30 9 SAMSUNG DAY AT MTL; DR. CHANG-GYU HWANG 10 MIT & MASDAR INSTITUTE MIT & Masdar Institute develop microsystems education & research in the Middle East. 12 MARC2010 13 ENERGY RESEARCHERS FIND OBAMA AN EAGER STUDENT President showed keen interest, quick understanding and warm appreciation, say his hosts. 14 IN THE NEWS 40 GRADUATION WOMEN IN ENGINEERING FEATURE STORIES page 34 24 COLLABORATION AT ITS BEST Everyone wins when MTL and industry join forces. 30 MEDICAL ELECTRONIC SYSTEMS Can Boston become the “Silicon Valley of Medical Electronic Systems?” MTL researchers are working hard to make it happen. WOMEN IN ENGINEERING MIT’s Women’s Technology Program. ON THE COVER 34 Detail of President Barack Obama’s RESEARCH signature on a vacuum pump located in 16 MECHANICAL DEVICES STAMPED ON PLASTIC the Bulovic lab. Microelectromechanical devices gave us the Wii and the digital movie projector. MIT researchers have found a new way to make them. Photo courtesy, Bulovic lab. 18 STRAINING FORWARD Nanowires made of ‘strained silicon’— silicon whose atoms have been pried slightly apart — show how to keep increases in computer power coming. -

RLE Currents | December 1988 (8.9Mb PDF)

Volume 2, Number 1 " December 1988 The Research Laboratory of Electronics at the Massachusetts Institute of Technology MATERIALS RESEARCH: Meeting the Challenge of Microelectronics Technology Since the discovery of the transis- tor at Bell Laboratories in 1947, scien- tists have been challenged by the need to produce materials for highly minia- turized and increasingly fast micro- electronic components. Driven by the technology of the information age, sci- entists have examined the unique properties of semiconductors, funda- mentally exploited new combinations of these novel materials, and devel- oped innovative design techniques to miniaturize electronic components. At the heart of this research is the ever- shrinking and exceedingly complex in- tegrated circuit microchip. In addition, the development of microscaled tran- sistors and other electronic compo- nents has resulted in systems with larg- er and faster capabilities, particularly for information processing and high- speed communication. I Every year since 1960, the number of circuit components on the most ad- Professor Henry I. Smith e.p loins the development of an alignment ststemJbr x-ray vanced microchip has nearly doubled. nanolithography that should be capable of 100-angstrom precision. Under his direction. Today, over 4 million transistors can be RLE's Submicron Structures Laboratory has pioneered new technologies in submicron onto one packed neatly computer structuresfabrication and explored deep -submicron MOSPETs and the exciting new memory or DRAM random (dynamic field of quantum-effect electronics (see related article on page 7.). Working with Prqfes- access memory) chip. The dramatic sor Dimitri Antoniadis and graduate student Ghavam Shahidi, dx. have discovered that miniaturization of electronic compo- the deleterious hot- electron effects seen in silicon MOSFETs with channel lengths below nents over the last forty years has raised 0.25 microns actually decrease at linewidths below 0.15 microns. -

IBM Research Report SOI Series MOSFET for Embedded High

RC24545 (W0805-007) May 1, 2008 Electrical Engineering IBM Research Report SOI Series MOSFET for Embedded High Voltage Applications and Soft-Error Immunity Jin Cai, Tak Ning, Philip Oldiges*, Anthony Chou*, Arvind Kumar*, Werner Rausch*, Wilfried Haensch, Ghavam Shahidi IBM Research Division Thomas J. Watson Research Center P.O. Box 218 Yorktown Heights, NY 10598 *IBM Semiconductor Research & Development Center Hopewell Junction, NY 12533 Research Division Almaden - Austin - Beijing - Cambridge - Haifa - India - T. J. Watson - Tokyo - Zurich LIMITED DISTRIBUTION NOTICE: This report has been submitted for publication outside of IBM and will probably be copyrighted if accepted for publication. It has been issued as a Research Report for early dissemination of its contents. In view of the transfer of copyright to the outside publisher, its distribution outside of IBM prior to publication should be limited to peer communications and specific requests. After outside publication, requests should be filled only by reprints or legally obtained copies of the article (e.g. , payment of royalties). Copies may be requested from IBM T. J. Watson Research Center , P. O. Box 218, Yorktown Heights, NY 10598 USA (email: [email protected]). Some reports are available on the internet at http://domino.watson.ibm.com/library/CyberDig.nsf/home . SOI Series MOSFET for Embedded High Voltage Applications and Soft-Error Immunity Jin Cai, Tak Ning, Philip Oldiges*, Anthony Chou*, Arvind Kumar*, Werner Rausch*, Wilfried Haensch and Ghavam Shahidi IBM Research Division, T. J. Watson Research Center, Yorktown Heights, NY 10598 * IBM Semiconductor Research & Development Center, Hopewell Junction, NY 12533 Phone: 914-945-2310; Fax: 914-945-2141; E-mail: [email protected]. -

Electrical Characterization of Sub-30Nm Gatelength SOI Mosfets Terence Kane, Michael P

Proceedings from the 30th International Symposium for Testing and Failure Analysis, November 14-18, 2004 Worcester, Massachusetts Electrical Characterization of sub-30nm Gatelength SOI MOSFETs Terence Kane, Michael P. Tenney IBM Microelectronics, Hopewell Junction, New York Abstract manufacturing but also for discrete device electrical characterization. Demonstrations of sub 20nm gate length MOSFET devices According to the 2003 International Technology Roadmap for involving various FEOL (front end of line) schemes such as high performance logic [5] development of UT-SOI MOSFET Silicon On DEpletion Layer (SODEL) FET’s, asymmetric- devices is fairly advanced at the 65 nm nodes. This is shown gate FinFET devices, planar Ultra-thin body SOI (UTSOI) in TABLE I. [5] FET’s, and, more recently, independently oriented surface channels for (110) pMOS and (100) nMOS described as Table 1: 2003 ITRS Roadmap for High Performance Logic[5] Simplified Hybrid Orientation Technology (SHOT).[1-4, 7- 18] have been reported. SHOT FEOL integration for FinFETs can be combined on the same wafer as planar PDSOI and UTSOI MOSFETs [18]. According to International Technology Roadmap for Semiconductors (ITRS) guidelines [5] 20nm silicon layers with +/-5%, 6V uniformity will be needed in 2004 timeframe[8] to guarantee threshold voltage ( Vt ) control [6]. Bonded Silicon on Insulator (SOI) processes that achieve +/- 10 A film thickness have been shown [6] for these Ultra-Thin SOI (UT-SOI) devices at the 65nm node and beyond. UT- SOI devices combined with SHOT (110) pMOS and (100) nMOS oriented surface channels offer optimizeed channel carrier mobility as well meeting issues of threshold voltage levels[4-18]. -

1.0 Submicron Structures Technology and Research

Submicron Structures Technology and Research 1.0 Submicron Structures Technology and Research Academic and Research Staff Prof. H.I. Smith, Dr. M.L. Schattenburg, J.M. Carter Visiting Scientists H. Kawata,1 I. Plotnik,2 I. Tanaka3 Graduate Students S. Ajuria, E.H. Anderson, H.A. Atwater, P. Bagwell, W. Chu, L. Clevenger, J. Floro, S.M. Garrison, J. Im, K. Ismail, E. Jiran, H.J. Kim, Y-C. Ku, U. Meirav, P. Meyer, A. Moel, J.E. Palmer, S.L. Park, H.M. Quek, J. Scott-Thomas, G. Shahidi, M. Toth, A.T. Yen 1.1 Submicron Structures Laboratory The Submicron Structures Laboratory at MIT develops techniques for fabricating surface structures with linewidths in the range from nanometers to micrometers, and uses these structures in a variety of research projects. These projects of the laboratory, which are described briefly below, fall into four major categories: development of submicron and nanometer fabrication technology; deep-submicron electronics and quantum-effect electronics; crystalline films on amorphous substrates; and periodic structures for x-ray optics and spectroscopy. 1.2 Microfabrication at Linewidths of 100nm and Below Joint Services Electronics Program (Contract DAALO3-86-K-0002) National Science Foundation (Grant ECS 87-09806) Erik H. Anderson, James M. Carter, William Chu, Hui M. Quek, Irving Plotnik, Mark L. Schattenburg, Anthony T. Yen, Henry I. Smith A variety of techniques for fabricating structures with characteristic dimensions of 0.1 ym (100 nm) and below are investigated. These include: x-ray nanolithography, holographic lithography, achromatic holographic lithography, electron-beam lithography, reactive-ion etching, electroplating and liftoff. -

(12) United States Patent (10) Patent No.: US 6, 180,486 B1 Leobandung Et Al

USOO6180486B1 (12) United States Patent (10) Patent No.: US 6, 180,486 B1 Leobandung et al. (45) Date of Patent: *Jan. 30, 2001 (54) PROCESS OF FABRICATING PLANAR AND 5,518,949 5/1996 Chen ...................................... 437/62 DENSELY PATTERNED 5,539,240 7/1996 Cronin et al. ........................ 257/520 SILICON-ON-INSULATOR STRUCTURE 5,567,634 * 10/1996 Hebert et al. ........................ 430/270 5,598,019 1/1997 Komori et al. ...................... 257/397 5,665,619 9/1997 Kwan et al. ......................... 438/270 (75) Inventors: E.A.S.Fingers 5,811,315 * 9/1998 Yindeepol et al. .................. 438/405 Pleasantville; Dominic J. Schepis, OTHER PUBLICATIONS Wappingers Falls; Ghavam Shahidi, Elmsford, all of NY (US) Stanley Wolf Silicon Processing for the VSLI ERA vol. 2 Lattice Press pp. 52, 69, 1990.* (73) Assignee: International Business Machines “Defect-Free Silicon on Insulator by Oxidized Porous Sili Corporation, Armonk, NY (US) con” by L.A. Nesbit. IBM Technical Disclosure Bulletin. vol. 27, No. 8, Jan. 1985.p.4632. (*) Notice: This patent issued on a continued pros- “Wet Processing: Cleaining, Etching, and Liftoff by S. Wolf ecution application filed under 37 CFR Ph.D., R. N. Tauber Ph.D., Silicon Processing for the VLSI 1.53(d), and is subject to the twenty year Era. vol. 1, 1986, pp. 516-517. patent term provisions of 35 U.S.C. 154(a)(2). * cited by examiner Under 35 U.S.C. 154(b), the term of this Primary Examiner—Charles Bowers patent shall be extended for 0 days. ASSistant Examiner David S Blum (74) Attorney, Agent, or Firm-Ratner & Prestia; Joseph P. -

Highlights from the Chicago Meeting

Highlights from Chicago ttendees of the 211th ECS meeting was the presentation of the session. Thus the audience was treated meeting were treated to an Student Poster Session Awards at to a “two-for-one” in Chicago in Aarray of celebrities during the the Annual Society Luncheon and terms of featured talks. week. In addition to the two stellar Business Meeting on Tuesday. Twenty- speakers at the Plenary Session on four booths in the Technical Exhibit Plenary Session Monday morning, attendees also provided attendees with a wealth of The ECS Lecture was given by caught glimpses of U.S. Presidential information on services, hardware, JAMES TOUR of Rice University and candidates Barack Obama and Hilary and software related to the needs of his talk was entitled, “Nanocars and Clinton; and celebrities Oprah those in the fields ECS serves. This Hybrid Silicon/Molecule Devices.” Winfrey and the Mayor of Chicago. meeting also heralded a change in Prof. Tour is currently the Chao In addition to the fun, the over-,500 format: on Monday morning there Professor of Chemistry, Professor attendees presented ,355 papers in was a newly-combined Plenary of Computer Science, and Professor 38 sessions. An innovation of the Session and Honors and Awards of Mechanical Engineering and Nanovehicles were the subject of the ECS Lecture at the Plenary Session in Chicago this past spring. JAMES M. TOUR (second from left) delivered a fascinating talk on molecular machines. Joining him before the talk were ECS Vice-President D. NOEL BUCKLEY (far left), ECS President MARK ALLEndORF (third from left), and ECS Executive Director ROQUE CALVO (far right). -

Decadal Plan Full Report

Decadal Plan for Semiconductors FULL REPORT Published January 2021 Table of Contents Introduction . 7 Acronym Defi nitions . 8 Chapter 1 New Trajectories for Analog Electronics. .12 Chapter 2 New Trajectories for Memory and Storage . .42 Chapter 3 New Trajectories for Communication . .76 Chapter 4 New Trajectories for Hardware Enabled ICT Security . 102 Chapter 5 New Compute Trajectories for Energy-Effi cient Computing. 122 1 Decadal Plan Executive Committee James Ang, PNNL Kevin Kemp, NXP Dave Robertson, Analog Devices Dmytro Apalkov, Samsung Taff y Kingscott, IBM Gurtej Sandhu, Micron Fari Assaderaghi, Sunrise Memory Stephen Kosonocky, AMD Motoyuki Sato, TEL Ralph Cavin, Independent Consultant Matthew Klusas, Amazon Ghavam Shahidi, IBM Ramesh Chauhan, Qualcomm Steve Kramer, Micron Steve Son, SK hynix An Chen, IBM Donny Kwak, Samsung Mark Somervell, TEL Richard Chow, Intel Lawrence Loh, MediaTek Gilroy Vandentop, Intel Robert Clark, TEL Rafi c Makki, Mubadala Jeff rey Vetter, ORNL Maryam Cope, SIA Matthew Marinella, SNL Jeff rey Welser, IBM Debra Delise, Analog Devices Seong-Ho Park, SK hynix Jim Wieser, Texas Instruments Carlos Diaz, TSMC David Pellerin, Amazon Tomomari Yamamoto, TEL Bob Doering, Texas Instruments Daniel Rasic, SRC Ian Young, Intel Sean Eilert, Micron Ben Rathsak, TEL Todd Younkin, SRC Ken Hansen, Independent Consultant Wally Rhines, Cornami David Yeh, Texas Instruments Baher Haroun, Texas Instruments Heike Riel, IBM Victor Zhirnov, SRC Yeon-Cheol Heo, Samsung Kirill Rivkin, Western Digital Zoran Zvonar, Analog Devices Gilbert Herrera, SNL Juan Rey, Mentor (Siemens) The Decadal Plan Workshops that helped drive this report were supported by the U.S. Department of Energy, Advanced Scientifi c Computing Research (ASCR) and Basic Energy Sciences (BES) Research Programs, and the National Nuclear Security Agency, Advanced Simulation and Computing (ASC) Program. -

UNIVERSITY of CALIFORNIA Los Angeles Design, Evaluation and Co

UNIVERSITY OF CALIFORNIA Los Angeles Design, Evaluation and Co-optimization of Emerging Devices and Circuits A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Electrical Engineering by Shaodi Wang 2017 c Copyright by Shaodi Wang 2017 ABSTRACT OF THE DISSERTATION Design, Evaluation and Co-optimization of Emerging Devices and Circuits by Shaodi Wang Doctor of Philosophy in Electrical Engineering University of California, Los Angeles, 2017 Professor Puneet Gupta, Chair The continued push for traditional Silicon technology scaling faces the main chal- lenge of non-scaling power density. Exploring alternative power-efficient technologies is essential for sustaining technology development. Many emerging technologies have been proposed as potential replacement for Silicon technology. However, these emerging tech- nologies need rigorous evaluation in the contexts of circuits and systems to identify their value prior to commercial investment. We have developed evaluation frameworks cover- ing emerging Boolean logic devices, memory devices, memory systems, and integration technologies. The evaluation metrics are in terms of delay, power, and reliability. Ac- cording to the evaluation results, the development of emerging Boolean logic devices is still far from being able to replace Silicon technology, but magnetic random access mem- ory (MRAM) is a promising memory technology showing benefits in performance and energy-efficiency. As a specific example, we co-optimize MRAM with application circuits and systems. Optimized MRAM write and read design can significantly improve the system perfor- mance. We have proposed magnetic tunnel junction (MTJ) based process and tem- perature variation monitor, which enables variation-aware MRAM write and read op- timization. -

Performance Analysis of 8-Bit ALU for Power in 32 Nm Scale

International Journal of Engineering Research & Technology (IJERT) ISSN: 2278-0181 Vol. 1 Issue 8, October - 2012 Performance Analysis Of 8-Bit ALU For Power In 32 Nm Scale Pooja Vaishnav ME(VLSI design) SSCET,Bhilai Mr. Vishal Moyal SSITM,Bhilai ABSTRACT leakages which threatened the continuance of The 32 nm process (also called 32 nanometer Moore’s Law. node) is the next step after the 45 nanometer process in CMOS semiconductor device fabrication. Like the The introduction of high-k dielectric gate 45 nm generation, the 32 nm node will take transistors on the 32nm generation broke through advantage of the performance tricks of the prior some of these scaling barriers. At the 32 nm node, technology generation, including immersion high-K dielectric gate will be the mainstream gate lithography. The biggest change at 32 nm will be the stack in high volume manufacturing. In this space, introduction of high-k dielectrics and metal gates into gate length and contact all must be scaled. production. The development of next 32 nm generation needs innovations on not only device structures, but also fabrication techniques and material selections. This reduces the Power Dissipation and Leakage Current in the designing of any circuitry. The major sources of leakage current are the gate direct tunneling current, the sub-IJERT threshold leakage and the reverse biased band-to- band-tunneling junction leakage. To reduce total chip power, these leakage components must be suppressed. Here, for giving the advantages of 32nm scale technology 8-bit ALU was simulated on the different number of integration scale. The advantages of 32nm technology will be given over the other scaling technology. -

Ieee Cledo Brunetti Award Recipients

IEEE CLEDO BRUNETTI AWARD RECIPIENTS 2022 – SIMON DELEONIBUS “For contributions to and leadership in Chief Scientist (Retired), CEA, nanoscale CMOS device and process LETI, Grenoble, France technologies.” 2021 – JESUS DEL ALAMO “For leadership in and contributions to Donner Professor and Professor of InGaAs- and GaN-based field-effect Electrical Engineering, transistor technology.” Massachusetts Institute of Technology, Cambridge, Massachusetts, USA 2020 – JAMES H. STATHIS “For contributions to the understanding of Principal Research gate dielectric reliability and its application Staff Member, IBM Research, to transistor scaling.” Yorktown Heights, New York, USA AND ERNEST YUE WU Senior Technical Staff Member, IBM Research, Albany, New York, USA 2019 – DANIEL C. EDELSTEIN “For contributions to manufacturable, IBM Fellow, IBM T.J. Watson reliable, and scalable Cu interconnect and Research Center, Yorktown low-k dielectric technology for CMOS.” Heights, New York, USA AND ALFRED GRILL IBM Fellow, IBM T.J. Watson Research Center, Yorktown Heights, New York, USA AND CHAO-KUN HU Research Staff Member, IBM T.J. Watson Research Center, Yorktown Heights, New York, USA 2018 - SIEGFRIED SELBERHERR “For pioneering contributions to Technology Professor, Vienna University of Computer Aided Design.” Technology, Institute for Microelectronics, Vienna, Austria 1 of 6 IEEE CLEDO BRUNETTI AWARD RECIPIENTS 2017 - GUIDO GROESENEKEN “For contributions to the characterization Professor, Catholic University of and understanding of the reliability physics Leuven, -

Highlights from CSTIC 2013

SOCIETY NEWS technologies. Dr. Wachsman recently published visit, but all left with a newfound appreciation of that will inform our positions and actions an article entitled, “Role of Solid Oxide Fuel the accessibility and willingness of the legislators throughout the rest of our long careers in science Cells in a Balanced Energy Strategy” in Energy and their staff to meet with constituents and to and engineering. I’m glad that we were able & Environmental Science, and gave a number of hear their concerns. Though brief, the meetings to have this experience early on in our careers energy policy oriented talks in DC region. were a great opportunity to make contacts with so that we have many decades to improve our Roque Calvo, Executive Director of ECS; legislators and their staff, and the UMD chapter relationship with our congressmen and women. Betsy Houston of Federation of Materials members were able to offer assistance and I look forward to spreading this message to Sciences; Dean Darryl Pines of UMD’s Clark information to congressional staff as well as my peers at UMD, in ECS, and in the other School of Engineering, and; Bob Boege, grow their own network in the policy world. professional spheres I go on to inhabit in the organizer of SET-CVD, were instrumental in Colin Gore, President of the UMD chapter, future. guiding the students, however, the enthusiasm put it nicely when he said, “I know that though For more information on participating and commitment of the students to science we don’t yet have the clout to make any big on Science, Engineering, Technology prevailed.