Circuit Design with VHDL Volnei A

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

A Vhsic Hardware Description Language Compiler for Logic Cell Arrays

A VHSIC HARDWARE DESCRIPTION LANGUAGE COMPILER FOR LOGIC CELL ARRAYS by Bing Liu A thesis presented to the university of Mânitoba in partial fulfillment of úe requirements of the degree of Maste¡ of Science in Elecrical and Computel Engineering Winnipeg, Manitoba, Canada @ Bing Liu, January 1990 Bibliothèque nat¡onale rE fr"3""i"i;tjo'",' du Canada Canadian Theses Serv¡ce Service des thèses canadiennes Otta'¿/ã. Can¿da Kl A ON¡ The author has granted an inevocable non' L'auteur a accordé une licence iffévocable et exclusive licence allowing the National Library non exclusive permettant à h Bibliothèque of Canada to reproduce, loan, distribute or sell nationale du Canada.de reproduire, prêter, copies of his/her thesis by any means and in distribuer ou vendre des copies de sa thèse any form or format, making this thesis avaihble de quelque manière et sous quelque forme to ¡nterested persons. que ce soit pour mettre des exemplaires de cette thèse à la disposition des personnes intéressées. The author retains ownership of the copyright L auteur conserve la propriété du droit d'auteur in his/her thesis. Neither the thesis nor qui protà?e sa thèse. Ni la thèse ni des extraits substantial extracts from it may be printed or substantiels de celle-ci ne doivent être otherw¡se reproduced without his/her per' imprimés ou autrement reproduits sans son mission. autorisation. ISBN ø-315-7 r7s t -3 Canadä A VHSIC HARDWARE DESCRIPTION I.ANGUAGE COMPILER FOR LOG]C CEI,L ARRAYS BY BING LIU A thesis subnrined lo thc Fact¡lty of Crâduate Studies of the University of M¿nitoba in partial fulfìllment of the requirenrents of the degree of MASTM O¡' SC]MICE o 1990 Permission has becn granted to the L¡BRÁRY OF THE UNIVER' SITY OF MANITOBA to lend o¡ sell copies of tlt¡s thesis. -

Co-Simulation Between Cλash and Traditional Hdls

MASTER THESIS CO-SIMULATION BETWEEN CλASH AND TRADITIONAL HDLS Author: John Verheij Faculty of Electrical Engineering, Mathematics and Computer Science (EEMCS) Computer Architecture for Embedded Systems (CAES) Exam committee: Dr. Ir. C.P.R. Baaij Dr. Ir. J. Kuper Dr. Ir. J.F. Broenink Ir. E. Molenkamp August 19, 2016 Abstract CλaSH is a functional hardware description language (HDL) developed at the CAES group of the University of Twente. CλaSH borrows both the syntax and semantics from the general-purpose functional programming language Haskell, meaning that circuit de- signers can define their circuits with regular Haskell syntax. CλaSH contains a compiler for compiling circuits to traditional hardware description languages, like VHDL, Verilog, and SystemVerilog. Currently, compiling to traditional HDLs is one-way, meaning that CλaSH has no simulation options with the traditional HDLs. Co-simulation could be used to simulate designs which are defined in multiple lan- guages. With co-simulation it should be possible to use CλaSH as a verification language (test-bench) for traditional HDLs. Furthermore, circuits defined in traditional HDLs, can be used and simulated within CλaSH. In this thesis, research is done on the co-simulation of CλaSH and traditional HDLs. Traditional hardware description languages are standardized and include an interface to communicate with foreign languages. This interface can be used to include foreign func- tions, or to make verification and co-simulation possible. Because CλaSH also has possibilities to communicate with foreign languages, through Haskell foreign function interface (FFI), it is possible to set up co-simulation. The Verilog Procedural Interface (VPI), as defined in the IEEE 1364 standard, is used to set-up the communication and to control a Verilog simulator. -

Going Vertical: a New Integration Era in the Semiconductor Industry Table of Contents

Going vertical: A new integration era in the semiconductor industry Table of contents 01 Executive overview Integration in the 02 semiconductor industry Strategic options for 03 semiconductor companies Moving forward: what semiconductor 04 companies must consider today Going vertical: A new integration era in the semiconductor industry 2 Executive overview Like many industries, the semiconductor industry is not immune to waves of diversification and consolidation through inorganic and organic growth. While inflection points with large-scale systemic changes in the value chain are relatively rare, our perspective is that there is a systemic change currently trending in the industry. Since the inception of the industry, semiconductor companies have recognized the value of technology. Accordingly, the market has rewarded semiconductor companies for specializing in distinct parts of the value chain by developing technological advantages by investing in R&D and by scaling technology through horizontal integration. This way of working transformed an industry that was initially vertically integrated (semiconductor design, semiconductor manufacturing, and system integration) into an ecosystem focused on specific areas of design, manufacturing, and/or systems. In the past five years, business value in some segments has moved from underlying technology to specific use cases to better monetize end-customer data and experience. • 5G, automotive, AI, cloud, system integration and hardware-software integration System integrators and software and cloud platform companies are no longer just important customers for the semiconductor industry—they are directly expanding into multiple upstream areas. • Taking advantage of silicon and system design • Control more of the technology stack • Optimize system performance • Improve the customer experience This vertical integration trend is distinctly different from the vertical integration which occurred at the inception of the semiconductor and integrated device manufacturing industry more than 50 years ago. -

Download the Compiled Program File Onto the Chip

International Journal of Computer Science & Information Technology (IJCSIT) Vol 4, No 2, April 2012 MPP SOCGEN: A FRAMEWORK FOR AUTOMATIC GENERATION OF MPP SOC ARCHITECTURE Emna Kallel, Yassine Aoudni, Mouna Baklouti and Mohamed Abid Electrical department, Computer Embedded System Laboratory, ENIS School, Sfax, Tunisia ABSTRACT Automatic code generation is a standard method in software engineering since it improves the code consistency and reduces the overall development time. In this context, this paper presents a design flow for automatic VHDL code generation of mppSoC (massively parallel processing System-on-Chip) configuration. Indeed, depending on the application requirements, a framework of Netbeans Platform Software Tool named MppSoCGEN was developed in order to accelerate the design process of complex mppSoC. Starting from an architecture parameters design, VHDL code will be automatically generated using parsing method. Configuration rules are proposed to have a correct and valid VHDL syntax configuration. Finally, an automatic generation of Processor Elements and network topologies models of mppSoC architecture will be done for Stratix II device family. Our framework improves its flexibility on Netbeans 5.5 version and centrino duo Core 2GHz with 22 Kbytes and 3 seconds average runtime. Experimental results for reduction algorithm validate our MppSoCGEN design flow and demonstrate the efficiency of generated architectures. KEYWORD MppSoC, Automatic code generation; mppSoC configuration;parsing ; MppSoCGEN; 1. INTRODUCTION Parallel machines are most often used in many modern applications that need regular parallel algorithms and high computing resources, such as image processing and signal processing. Massively parallel architectures, in particular Single Instruction Multiple Data (SIMD) systems, have shown to be powerful executers for data-intensive applications [1]. -

Computer Organization and Architecture Designing for Performance Ninth Edition

COMPUTER ORGANIZATION AND ARCHITECTURE DESIGNING FOR PERFORMANCE NINTH EDITION William Stallings Boston Columbus Indianapolis New York San Francisco Upper Saddle River Amsterdam Cape Town Dubai London Madrid Milan Munich Paris Montréal Toronto Delhi Mexico City São Paulo Sydney Hong Kong Seoul Singapore Taipei Tokyo Editorial Director: Marcia Horton Designer: Bruce Kenselaar Executive Editor: Tracy Dunkelberger Manager, Visual Research: Karen Sanatar Associate Editor: Carole Snyder Manager, Rights and Permissions: Mike Joyce Director of Marketing: Patrice Jones Text Permission Coordinator: Jen Roach Marketing Manager: Yez Alayan Cover Art: Charles Bowman/Robert Harding Marketing Coordinator: Kathryn Ferranti Lead Media Project Manager: Daniel Sandin Marketing Assistant: Emma Snider Full-Service Project Management: Shiny Rajesh/ Director of Production: Vince O’Brien Integra Software Services Pvt. Ltd. Managing Editor: Jeff Holcomb Composition: Integra Software Services Pvt. Ltd. Production Project Manager: Kayla Smith-Tarbox Printer/Binder: Edward Brothers Production Editor: Pat Brown Cover Printer: Lehigh-Phoenix Color/Hagerstown Manufacturing Buyer: Pat Brown Text Font: Times Ten-Roman Creative Director: Jayne Conte Credits: Figure 2.14: reprinted with permission from The Computer Language Company, Inc. Figure 17.10: Buyya, Rajkumar, High-Performance Cluster Computing: Architectures and Systems, Vol I, 1st edition, ©1999. Reprinted and Electronically reproduced by permission of Pearson Education, Inc. Upper Saddle River, New Jersey, Figure 17.11: Reprinted with permission from Ethernet Alliance. Credits and acknowledgments borrowed from other sources and reproduced, with permission, in this textbook appear on the appropriate page within text. Copyright © 2013, 2010, 2006 by Pearson Education, Inc., publishing as Prentice Hall. All rights reserved. Manufactured in the United States of America. -

North American Company Profiles 8X8

North American Company Profiles 8x8 8X8 8x8, Inc. 2445 Mission College Boulevard Santa Clara, California 95054 Telephone: (408) 727-1885 Fax: (408) 980-0432 Web Site: www.8x8.com Email: [email protected] Fabless IC Supplier Regional Headquarters/Representative Locations Europe: 8x8, Inc. • Bucks, England U.K. Telephone: (44) (1628) 402800 • Fax: (44) (1628) 402829 Financial History ($M), Fiscal Year Ends March 31 1992 1993 1994 1995 1996 1997 1998 Sales 36 31 34 20 29 19 50 Net Income 5 (1) (0.3) (6) (3) (14) 4 R&D Expenditures 7 7 7 8 8 11 12 Capital Expenditures — — — — 1 1 1 Employees 114 100 105 110 81 100 100 Ownership: Publicly held. NASDAQ: EGHT. Company Overview and Strategy 8x8, Inc. is a worldwide leader in the development, manufacture and deployment of an advanced Visual Information Architecture (VIA) encompassing A/V compression/decompression silicon, software, subsystems, and consumer appliances for video telephony, videoconferencing, and video multimedia applications. 8x8, Inc. was founded in 1987. The “8x8” refers to the company’s core technology, which is based upon Discrete Cosine Transform (DCT) image compression and decompression. In DCT, 8-pixel by 8-pixel blocks of image data form the fundamental processing unit. 2-1 8x8 North American Company Profiles Management Paul Voois Chairman and Chief Executive Officer Keith Barraclough President and Chief Operating Officer Bryan Martin Vice President, Engineering and Chief Technical Officer Sandra Abbott Vice President, Finance and Chief Financial Officer Chris McNiffe Vice President, Marketing and Sales Chris Peters Vice President, Sales Michael Noonen Vice President, Business Development Samuel Wang Vice President, Process Technology David Harper Vice President, European Operations Brett Byers Vice President, General Counsel and Investor Relations Products and Processes 8x8 has developed a Video Information Architecture (VIA) incorporating programmable integrated circuits (ICs) and compression/decompression algorithms (codecs) for audio/video communications. -

A Vhdl-Based Digital Slot Machine Implementation Using A

A VHDL-BASED DIGITAL SLOT MACHINE IMPLEMENTATION USING A COMPLEX PROGRAMMABLE LOGIC DEVICE by Lucas C. Pascute Submitted in Partial Fulfillment ofthe Requirements for the Degree of Master ofScience ofEngineering in the Electrical Engineering Program YOUNGSTOWN STATE UNIVERSITY December, 2002 A VHDL-BASED DIGITAL SLOT MACHINE IMPLEMENTATION USING A COMPLEX PROGRAMMABLE LOGIC DEVICE Lucas C. Pascute I hereby release this thesis to the public. I understand that this thesis will be made available from the OhioLINK ETD Center and the Maag Library Circulation Desk for public access. I also authorize the University or other individuals to make copies ofthis thesis as needed for scholarly research. Signature: ;/ (' , p ~-~_.._--- c:;.--_. ~ ~b IZ-3-Cl7., Lucas C. Pascute, Student Date Approvals: r. Faramarz Mossayebi, Thesis Advisor 12-:}--02- Date S~?c~ /"L/ 0:5 /u C Dr. Salvatore Pansino, Committee Member Date Dr. Peter J. K: vinsky, Dean ofGradua 111 ABSTRACT The intent ofthis project is to provide an educational resource from which future students can learn the basics ofprogrammable logic and the design process involved. More specifically, the area ofinterest involves very large scale integration (VLSI) design and the advantages associated with it such as reduced chip count and development time. The methodology used within is to first implement a design; using small and medium scale integration (SSI/MSI) packages in order to have a baseline for comparison. The design is then translated for use with the very high speed integrated circuit hardware description language (VHDL) and implemented onto a complex programmable logic device (CPLD). A discussion ofthis implementation process as well as VHDL lessons is provided to serve as a tutorial for the interested reader. -

Using Modelsim to Simulate Logic Circuits in Verilog Designs

Using ModelSim to Simulate Logic Circuits in Verilog Designs For Quartus Prime 16.0 1 Introduction This tutorial is a basic introduction to ModelSim, a Mentor Graphics simulation tool for logic circuits. We show how to perform functional and timing simulations of logic circuits implemented by using Quartus Prime CAD software. The reader is expected to have the basic knowledge of the Verilog hardware description language, and the Altera Quartus® Prime CAD software. Contents: • Introduction to simulation • What is ModelSim? • Functional simulation using ModelSim • Timing simulation using ModelSim Altera Corporation - University Program 1 May 2016 USING MODELSIM TO SIMULATE LOGIC CIRCUITS IN VERILOG DESIGNS For Quartus Prime 16.0 2 Background Designers of digital systems are inevitably faced with the task of testing their designs. Each design can be composed of many modules, each of which has to be tested in isolation and then integrated into a design when it operates correctly. To verify that a design operates correctly we use simulation, which is a process of testing the design by applying inputs to a circuit and observing its behavior. The output of a simulation is a set of waveforms that show how a circuit behaves based on a given sequence of inputs. The general flow of a simulation is shown in Figure1. Figure 1. The simulation flow. There are two main types of simulation: functional and timing simulation. The functional simulation tests the logical operation of a circuit without accounting for delays in the circuit. Signals are propagated through the circuit using logic and wiring delays of zero. This simulation is fast and useful for checking the fundamental correctness of the 2 Altera Corporation - University Program May 2016 USING MODELSIM TO SIMULATE LOGIC CIRCUITS IN VERILOG DESIGNS For Quartus Prime 16.0 designed circuit. -

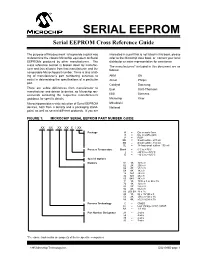

Serial EEPROM Cross Reference Guide

SERIAL EEPROM Serial EEPROM Cross Reference Guide The purpose of this document is to provide a quick way interested in a part that is not listed in this book, please to determine the closest Microchip equivalent to Serial refer to the Microchip data book, or contact your local EEPROMs produced by other manufacturers. The distributor or sales representative for assistance. cross reference section is broken down by manufac- The manufacturers* included in this document are as turer and lists all parts from that manufacturer, and the follows: comparable Microchip part number. There is also a list- ing of manufacturer’s part numbering schemes to AKM Oki assist in determining the specifications of a particular Atmel Philips part. Catalyst Samsung There are subtle differences from manufacturer to Exel SGS-Thomson manufacturer and device to device, so Microchip rec- ommends consulting the respective manufacturer’s ISSI Siemens gadabout for specific details. Microchip Xicor Microchip provides a wide selection of Serial EEPROM Mitsubishi devices, both from a density and a packaging stand- National point, as well as several different protocols. If you are FIGURE 1: MICROCHIP SERIAL EEPROM PART NUMBER GUIDE XX XX XX XX X / XX Package W = Die in wafer form S = Die in waffle pack P = PDIP SM = Small outline .207 mil SN = Small outline .150 mil SL = 14-lead small outline .150 mil Process Temperature Blank = 0°C to +70°C I = -40°C to +125°C E = -40°C to +125°C Special Options Memory 01 1K 128 x 8 02 2K 256 x 8 04 4K 512 x 8 08 8K 1K x 8 16 16K 2K x 8 32 32K 4K x 8 65 64K 8K x 8 11 1K 128K x 8 or 64 x 16 72 1K 128 x 8 82 2K 256 x 8 92 4K 512 x 8 06 256 Bit 16 x 16 46 1K 64 x 16/128 x 8 56 2K 256 x 8/128 x 16 66 4K 512 x 8/256 x 16 Process Technology C – CMOS LC – Low Voltage (2.5V) CMOS AA – 1.8 Volt Part Number Designator 24 – 2-wire 59 – 4-wire 85 – 2-wire 93 – 3-wire *The above trademarks are property of their respective companies. -

Anr018 Gnss I2c Communication

ANR018 GNSS I2C COMMUNICATION VERSION 1.2 JUNE 2, 2021 Revision history Manual Notes Date version 1.0 • Initial version June 2020 1.1 • Figure 7 and 8 updated July 2020 1.2 • Updated Chapter 3 June 2021 ANR018 GNSS I2C Communication version 1.2 © June 2021 www.we-online.com/wireless-connectivity 1 Abbreviations and abstract Abbreviation Description ASCII American Standard Code for Information Interchange CTS Clear to send I2C Inter-IC bus GND Ground GNSS Global Navigation Satellite System HIGH Digital (logic) high level IC Integrated Circuit IDC Insulation Displacement Contact LOW Digital (logic) low level µC Microcontroller NMEA National Marine Electronics Association OSP One Socket Protocol PC Personal Computer RTS Request to send SCL Serial Clock SDA Serial Data USB Universal Serial Bus ANR018 GNSS I2C Communication version 1.2 © June 2021 www.we-online.com/wireless-connectivity 2 Contents 1 Introduction5 2 I2C Digital interface6 2.1 General characteristics..............................6 2.2 SDA and SCL logic levels............................6 2.3 Communication phase..............................6 2.3.1 Idle state.................................6 2.3.2 START(S) and STOP(P) condition...................7 2.3.3 Data validity...............................7 2.3.4 Data format...............................8 2.3.5 Acknowledge and No-Acknowledge..................8 2.3.6 Addressing the GNSS module.....................8 2.3.7 GNSS communication protocol....................9 2.4 I2C timing parameters..............................9 3 Hardware Setup 10 3.1 Hardware Setup - 1.8V.............................. 10 3.2 Evaluation Board Modification - 1.8V...................... 11 3.3 Hardware Setup - Erinome-I........................... 13 3.4 Evaluation Board Modification - Erinome-I................... 14 4 Application Example 16 4.1 Total Phase Aardvark host adapter...................... -

48-Bit, High Current, Logic Level Digital I/O Board for PCI

User's Guide http://www.omega.com e-mail: [email protected] CIO-DIO48 CIO-DIO48H CIO-DIO96 CIO-DIO192 INTRODUCTION ................................... 1 Cable from DIO board QUICK START ..................................... 2 plugs into connector TM labeled IN Cable to second ERB or INSTALL THE INSTACAL SOFTWARE .................... 2 TM SSR board plugs into RUN INSTACAL ..................................... 2 connector labeled OUT OPERATION ....................................... 4 INSTALLATION ...................................... 4 BASE ADDRESS ...................................... 4 WAIT STATE JUMPER .................................. 6 INSTALLING THE CIO-DIO IN THE COMPUTER ............... 6 CABLING TO THE DIO CONNECTOR ....................... 7 SIGNAL CONNECTION - CIO-DIO48 ........................ 7 UNCONNECTED INPUTS FLOAT .......................... 8 CONNECTOR DIAGRAM ................................ 8 Cable from DIO board Cable to second ERB or ARCHITECTURE ................................... 9 plugs into connector SSR board plugs into labeled IN connector labeled OUT 82C55 CONTROL & DATA REGISTERS ...................... 9 82C55 DIGITAL I/O REGISTERS .......................... 11 SPECIFICATIONS ................................. 14 POWER CONSUMPTION ............................... 14 DIGITAL I/O ........................................ 15 ELECTRONICS AND INTERFACING ................. 16 PULL UP & PULL DOWN RESISTORS ...................... 16 UNCONNECTED INPUTS FLOAT ......................... 18 CIO-ERB-24 and SSR-RACK24 provide -

Introduction to Simulation of VHDL Designs Using Modelsim Graphical Waveform Editor

Introduction to Simulation of VHDL Designs Using ModelSim Graphical Waveform Editor For Quartus II 13.1 1 Introduction This tutorial provides an introduction to simulation of logic circuits using the Graphical Waveform Editor in the ModelSim Simulator. It shows how the simulator can be used to perform functional simulation of a circuit specified in VHDL hardware description language. It is intended for a student in an introductory course on logic circuits, who has just started learning this material and needs to acquire quickly a rudimentary understanding of simulation. Contents: • Design Project • Creating Waveforms for Simulation • Simulation • Making Changes and Resimulating • Concluding Remarks Altera Corporation - University Program 1 October 2013 INTRODUCTION TO SIMULATION OF VHDL DESIGNS USING MODELSIM GRAPHICAL WAVEFORM EDITOR For Quartus II 13.1 2 Background ModelSim is a powerful simulator that can be used to simulate the behavior and performance of logic circuits. This tutorial gives a rudimentary introduction to functional simulation of circuits, using the graphical waveform editing capability of ModelSim. It discusses only a small subset of ModelSim features. The simulator allows the user to apply inputs to the designed circuit, usually referred to as test vectors, and to observe the outputs generated in response. The user can use the Waveform Editor to represent the input signals as waveforms. In this tutorial, the reader will learn about: • Test vectors needed to test the designed circuit • Using the ModelSim Graphical Waveform Editor to draw test vectors • Functional simulation, which is used to verify the functional correctness of a synthesized circuit This tutorial is aimed at the reader who wishes to simulate circuits defined by using the VHDL hardware description language.