A College Championship, Our NBA Finals Expectations, and Dreaded Feature Creep by Tom Fitzpatrick, Editor and Verification Technologist

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Cleveland Cavaliers (56-22) at Indiana Pacers (41-36)

WED., APRIL 6, 2016 BANKERS LIFE FIELDHOUSE – INDIANAPOLIS, IN TV: ESPN/FSO RADIO: 100.7 WMMS/LA MEGA 87.7 FM 7:00 PM EST CLEVELAND CAVALIERS (56-22) AT INDIANA PACERS (41-36) 2015-16 CLEVELAND CAVALIERS GAME NOTES OVERALL GAME # 79 ROAD GAME # 40 PROBABLE STARTERS 2015-16 SCHEDULE POS NO. PLAYER HT. WT. G GS PPG RPG APG FG% MPG 10/27 @ CHI Lost, 95-97 10/28 @ MEM WON, 106-76 F 23 LEBRON JAMES 6-8 250 15-16: 74 74 *25.0 7.5 >6.8 .514 35.6 10/30 vs. MIA WON, 102-92 11/2 @ PHI WON, 107-100 11/4 vs. NYK WON, 96-86 F 0 KEVIN LOVE 6-10 251 15-16: 74 74 16.0 ^9.9 2.4 .422 31.6 11/6 vs. PHI WON, 108-102 11/8 vs. IND WON, 101-97 11/10 vs. UTA WON, 118-114 C 20 TIMOFEY MOZGOV 7-1 275 15-16: 73 47 6.2 4.4 0.4 .565 17.3 11/13 @ NYK WON, 90-84 11/14 @ MIL Lost, 105-108** 11/17 @ DET Lost, 99-104 G 5 J.R. SMITH 6-6 225 15-16: 74 74 12.4 2.8 1.7 .414 30.7 11/19 vs. MIL WON, 115-100 11/21 vs. ATL WON, 109-97 G 2 KYRIE IRVING 6-3 193 15-16: 50 50 19.4 2.9 4.6 .446 31.2 11/23 vs. ORL WON, 117-103 11/25 @ TOR Lost, 99-103 11/27 @ CHA WON, 95-90 * Ranks 6th in NBA > Ranks 8th in NBA ^ Ranks 12th in NBA 11/28 vs. -

Administration of Barack Obama, 2016 Remarks Honoring the 2016

Administration of Barack Obama, 2016 Remarks Honoring the 2016 National Basketball Association Champion Cleveland Cavaliers November 10, 2016 The President. Hello, everybody! Welcome to the White House, and give it up for the World Champion Cleveland Cavaliers! That's right, I said "World Champion" and "Cleveland" in the same sentence. [Laughter] That's what we're talking about when we talk about hope and change. [Laughter] We've got a lot of big Cavs fans here in the house, including Ohio's Governor, John Kasich, and his daughters Emma and Reese. We've got some outstanding Members of Congress that are here. And obviously we want to recognize Cavs owner Dan Gilbert, who put so much of himself into trying to make sure this thing worked. One of the great general managers of the game, David Griffin. And the pride and joy of Mexico, Missouri—[laughter]— Coach Tyronn Lue. I also, before I go any further, want to give a special thanks to J.R. Smith's shirt for showing up. [Laughter] I wasn't sure if it was going to make an appearance today. I'm glad you came. You're a very nice shirt. [Laughter] Now, last season, the Cavs were the favorites in the East all along, but the road was anything but stable. And I'm not even talking about what happened on the court. There were rumors about who was getting along with who, and why somebody wasn't in a picture, and LeBron is tweeting—[laughter]—and this was all big news. But somehow Coach Lue comes in and everything starts getting a little smoother, and they hit their stride in the playoffs. -

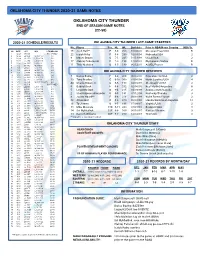

Thunder 2020-21 Game Notes

OKLAHOMA CITY THUNDER 2020-21 GAME NOTES OKLAHOMA CITY THUNDER END OF SEASON GAME NOTES (22-50) 2020-21 SCHEDULE/RESULTS OKLAHOMA CITY THUNDER LAST GAME STARTERS No. Player Pos. Ht. Wt. Birthdate Prior to NBA/Home Country NBA Yr. NO DATE OPP W/L **TV/RECORD 15 Josh Hall** F 6-8 200 10/08/00 Moravian Prep/USA R 1 12/23 @ HOU POSTPONED 22 Isaiah Roby F 6-8 230 02/03/98 Nebraska/USA 2 2 12/26 @ CHA W, 109-107 1-0 9 Moses Brown C 7-1 245 10/13/99 UCLA/USA 2 3 12/28 vs. UTA L, 109-110 1-1 4 12/29 vs. ORL L, 107-118 1-2 17 Aleksej Pokuševski F 7-0 195 12/26/01 Olympiacos/Serbia R 5 12/31 vs. NOP L, 80-113 1-3 6 1/2 @ ORL W, 108-99 2-3 11 Théo Maledon G 6-5 180 06/12/01 ASVEL/France R 7 1/4 @ MIA L, 90-118 2-4 8 1/6 @ NOP W, 111-110 3-4 OKLAHOMA CITY THUNDER RESERVES 9 1/8 @ NYK W, 101-89 4-4 10 1/10 @ BKN W, 129-116 5-4 11 1/12 vs. SAS L, 102-112 5-5 7 Darius Bazley F 6-8 208 06/12/00 Princeton HS/USA 2 12 1/13 vs. LAL L, 99-128 5-6 13 Tony Bradley C 6-10 260 01/08/98 North Carolina/USA 4 13 1/15 vs. CHI W, 127-125 (OT) 6-6 44 Charlie Brown Jr. -

Episode 6: Drazen Petrovic and Basketball’S Cold War

Death at the Wing Episode 6: Drazen Petrovic and Basketball’s Cold War ⧫ ⧫ ⧫ Back in 1988, the USA Men’s Basketball team did something they almost never did... ARCHIVAL ANNOUNCER: The United States found themselves in a position in the last seven minutes of this game of having to score on almost every possession and they could not. After winning 9 of the last 10 Olympics they competed in, they lost. ARCHIVAL ANNOUNCER: But there’s no time, really, for even a miracle now. And the Soviets are already celebrating. The USA suddenly found itself wearing bronze. It did not go over well. And so, as the dust settled, they decided to do what America does best: get better through hard work, inch by inch, grinding it out… I’m kidding. No, we did the real American thing. ARCHIVAL ANNOUNCER: What may well be the best basketball team ever assembled… ...which is throwing lots of money at something to make even more money. And so, for the next Olympics, they formed a super squad of sorts. No more amateurs. It was time to bend the rules a little bit and bring in the pros. And, of course, bring in Reebok to sponsor it. ARCHIVAL ANNOUNCER: And now, the United States of America. This was the Dream Team. Magic Johnson, Larry Bird, Michael Jordan. This wasn’t about winning gold. This was about buying the whole fucking gold mine. Shock and awe. 1 But in Barcelona in 1992, one player in all of the Olympics didn’t get the memo... or fax. -

![Where Are We At, March 29Th? [Crosstalk 00:00:13]](https://docslib.b-cdn.net/cover/5355/where-are-we-at-march-29th-crosstalk-00-00-13-2125355.webp)

Where Are We At, March 29Th? [Crosstalk 00:00:13]

The Bill Walton Show Why Bernie Sanders Should Understand Human Agency and Free Market Bill Walton: Where are we at, March 29th? [crosstalk 00:00:13] Speaker 2: March 29. Sarah Walton: Isn't it incredible? Speaker 2: Aren't we ready for summer? Bill Walton: Yes. Anne Bradley: Indeed. Sarah Walton: Most years you can put geraniums out April 1st. It doesn't seem like this year. Bill Walton: That's crazy. All right. The Bill Walton Show, March 29th. Speaker 2: Bill, look at the camera and some energy and when you're ready. Bill Walton: Today we're here to talk about a big topic, the moral case for free markets and the path to human flourishing. Joining me, to help us understand that topic is Dr. Anne Rathbone-Bradley, who is a professor of economics at the Institute of World Politics, that is an adjunct professor at George Mason University. She's also taught at Georgetown and Charles University in the Prague. Vice President now of Economic Initiatives at the Institute for Faith Work in Economics where she developed a systematic theology of economic freedom. Anne is also a specialist on the political economy of terrorism with a specific emphasis on industrial organization of Al Qaeda. Her most recent book is, "Counting the Cost, Christians' Perspectives on Capitalism." Anne, welcome. Anne Bradley: Bill, thanks for having me, pleasure to be here. Bill Walton: Great to have you here. Also joining me here is my lovely bride Sarah Walton who has an outstanding background as an artist and a designer. -

Cleveland's Epicenter of Entertainment

CLEVELAND’S EPICENTER OF ENTERTAINMENT PHOTOS: TREPAL PHOTOGRAPHY/CLEVELAND CAVALIERS PHOTOS: TREPAL OCTOBER 28-NOVEMBER 3, 2019 SPECIAL ADVERTISING SECTION I SPORTS BUSINESS JOURNAL 1A ROCKET MORTGAGE FIELDHOUSE: CLEVELAND’S EPICENTER OF ENTERTAINMENT ROCKET MORTGAGE FIELDHOUSE PHOTOS: TREPAL PHOTOGRAPHY/CLEVELAND CAVALIERS PHOTOS: TREPAL Creating a New, more connectivity to the brand the see Cavaliers or Monsters games, we company is using on a customer-fac- can cover the spectrum of interest.” State-of-the-Art Arena ing basis,” said Nic Barlage, president “We believe the Rocket Mortgage In July, Rocket Mortgage FieldHouse through a Total Renovation of business operations for the Cavs FieldHouse transformation is received its highest ranking from Walking into Rocket Mortgage and Rocket Mortgage FieldHouse. “It the most holistic renovation Pollstar, the concert industry’s leading was a unique convergence of oppor- trade publication, when it was ranked FieldHouse, guests are greeted by the of a major professional arena Power Portal, a dazzling display of tunities between the venue’s transfor- 27th of 200 top worldwide venues for video and sound that surrounds and mation and Quicken Loans’ rebrand- ever executed and will set the entertainment ticket sales (not includ- immerses them in one of the venue’s ing happening at the same time.” standard going forward.” ing sporting events). Additionally, the new signature experiences. The FieldHouse, which is owned by FieldHouse was ranked 11th in the U.S. This is just one highlight of the Cuyahoga County and the city of LEN KOMOROSKI for major concerts in 2019. recently completed two-year trans- Cleveland, has been a catalyst CEO I Cavs and Rocket “This ranking shows we have one of Mortgage FieldHouse formation to Rocket Mortgage behind nearly $2 billion in develop- the highest performing per capita FieldHouse, which was so all-encom- ment in Cleveland’s Gateway District. -

Granity Studios & ESPN+ Presents Kobe Detail Notes by Jeff Steines

Granity Studios & ESPN+ presents Kobe Detail Notes by Jeff Steines KOBE DETAIL EPISODE NO.: TITLE: 1. WESTERN CONFERENCE FINALS (2009) GAME #6 WITH KOBE BRYANT 2. WIZARDS VS RAPTORS PLAYOFFS (2018) GAME #1 WITH DEMAR DEROZAN 3. JAZZ VS ROCKETS PLAYOFFS (2018) GAME #1 WITH DONOVAN MITCHELL 4. WARRIORS VS PELICANS PLAYOFFS (2018) GAME #3 WITH JRUE HOLIDAY 5. EASTERN CONFERENCE FINALS (2018) PREVIEW WITH LEBRON JAMES 6. CLEVELAND VS BOSTON ECF (2018) GAME #2 WITH JAYSON TATUM 7. WESTERN CONFERENCE FINALS (2018) GAME # 3 WITH STEPHEN CURRY 8. EASTERN CONFERENCE FINALS (2018) GAME # 5 WITH JAYLEN BROWN 9. DURANT AND LEBRON NBA FINALS (2018) PREVIEW 10. CLEVELAND VS GOLDEN STATE NBA FINALS (2018) GAME #1 WITH KEVIN LOVE 11. CLEVELAND VS GOLDEN STATE NBA FINALS (2018) WITH KEVIN DURRANT 12. DRAFT CLASS (2018): REQUIRED VIEWING WITH SCOTTIE PIPPEN 13. NBA SUMMER LEAGUE WITH TRAE YOUNG 14. WNBA WITH JEWELL LOYD 15. BREANNA STEWART/ELENA DELLE DONNE (WNBA) 16. BREAKING DOWN JAMES HARDEN 17. BREAKING DOWN ARIKE OGUNBOWALE 18. BREAKING DOWN KALANI BROWN 19. BREAKING DOWN NAPHESSA COLLIER 20. BREAKING DOWN SABRINA IONESCU KOBE DETAIL EPISODE NO.: TITLE: 21. BREAKING DOWN KAWHI LEONARD 22. BREAKING DOWN KYRIE IRVING 23. BREAKING DOWN GIANNIS ANTETOKOUNMPO 24. BREAKING DOWN DAMIAN LILLARD 25. BREAKING DOWN DRAYMOND GREEN 26. DIANA TAURASI BREAKING DOWN KLAY THOMPSON 27. BREAKING DOWN STEPH CURRY 28. BREAKING DOWN KYLE LOWRY 29. BREAKING DOWN PASCAL SIAKAM 30. BREAKING DOWN KIMBA WALKER (FIBA) 31. BREAKING DOWN CHELSEA GRAY 32. BREAKING DOWN COURTNEY WILLIAMS 33. BREAKING DOWN BEN SIMMONS 34. BREAKING DOWN JOEL EMBIID 1. -

Monday, January 22, 2007 Quicken Loans

CLEVELAND CAVALIERS (8-1) VS. TORONTO RAPTORS (7-2) TUES., NOV. 15, 2016 QUICKEN LOANS ARENA – CLEVELAND, OH 7:00 PM EST TV: FSO/NBA TV RADIO: WTAM/LA MEGA 87.7 FM 2016-17 CLEVELAND CAVALIERS GAME NOTES OVERALL GAME # 10 HOME GAME # 7 LAST GAME’S STARTERS 2016-17 SCHEDULE All games can be heard on WTAM/La Mega 87.7 FM POS NO. PLAYER HT. WT. G GS PPG RPG APG FG% MPG 10/25 vs. NYK WON, 117-88 10/28 @ TOR WON, 94-91 10/29 vs. ORL WON, 105-99 F 23 LEBRON JAMES 6-8 250 16-17: 9 9 22.9 8.9 >9.1 .472 36.9 11/1 vs. HOU WON, 128-120 11/3 vs. BOS WON, 128-122 11/5 @ PHI WON, 102-101 F 0 KEVIN LOVE 6-10 251 16-17: 9 9 20.6 10.0 1.4 .429 32.5 11/8 vs. ATL Lost, 106-110 11/11 @ WAS WON, 105-94 C 13 TRISTAN THOMPSON 6-10 238 16-17: 9 9 5.0 9.6 0.8 .613 27.9 11/13 vs. CHA WON, 100-93 11/15 vs. TOR 7:00 p.m. NBATV/FSO 11/16 @ IND 7:00 p.m. FSO G 3 MIKE DUNLEAVY 6-9 220 16-17: 9 1 4.1 1.8 0.9 .316 16.2 11/18 vs. DET 7:30 p.m. FSO 11/23 vs. POR 7:00 p.m. FSO 11/25 vs. DAL 7:30 p.m. -

BART ROTHENBERGER TAFT HIGH 7-12 SCHOOL Asst

Brad Garrett 143 From: Rothenberger, Bart <[email protected]> Sent: Monday, February 27, 2017 10:12 AM To: Bennett, Bob; Brad Garrett Subject: West Valley Proposal Bob and Brad- I apologize I have been in an Admin meeting. The reason for us providing testimony is that you haven't heard much from the lower level classifications. We feel that this issue of 5A or 6A is really between those schools currently in those levels. We are primarily asking that you leave all schools alone from the 4A level down. If those 83 schools want to go to 5A or 6A then let them. The other issue is where do we cut off the numbers? We prior testimony and prior history from the the past 8 years we feel their is definitely an easy separation between 4A, 3A, 2A and 1A. Mr. Mulkey presented some findings that we felt were very pertinent on what leve you should be affiliated with. Those findings looked at lower level programs offered at a particular school. With that being said we feel the following ADM would be a good representation for the next four year block. 4A: 725 -371 (40 schools) 3A: 370 - 200 (38 Schools) 2A: 199-89 (44 Schools) 1A: 89- (85 schools) If we could do a survey of those 207 schools with these numbers I think you would be surprised. Take the remaining 81 schools with ADM over 726 and decide if you should go 5A or 6A. I do not see how a school with 800 can compete with school of 2500. -

FRED BOWEN Published by PEACHTREE PUBLISHERS 1700 Chattahoochee Avenue Atlanta, Georgia 30318-2112

FRED BOWEN Published by PEACHTREE PUBLISHERS 1700 Chattahoochee Avenue Atlanta, Georgia 30318-2112 www.peachtree-online.com Text © 1999 by Fred Bowen All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means—electronic, mechanical, photocopy, recording, or any other—except for brief quotations in printed reviews, without the prior permission of the publisher. Photo of Michael Jordan reprinted with permission of Dan Sears, Wilmington Morning Star. Photo of Bill Russell reprinted with permission of The National Basketball Hall of Fame. University of North Carolina Tar Heels trademark and copyright used with permission from the University of North Carolina–Chapel Hill. Cover design by Thomas Gonzalez and Maureen Withee Book design by Melanie McMahon Ives and Loraine M. Joyner Printed in the United States of America 10 9 8 7 6 5 4 3 2 1 First Revised Edition Bowen, Fred. The final cut / written by Fred Bowen. p. cm. Summary: After tryouts for the school basketball team, eighth graders Zeke, Eli, Ryan, and Miles find their friendship tested when two of them make the team and two of them do not. Includes facts about Michael Jordan and BIll Russell. ISBN 13 978-1-56145-510-2 / ISBN 10 1-56145-510-5 [1. Basketball--Fiction. 2. Friendship--Fiction. 3. Determination (Personality trait)--Fiction.] I. Title. PZ7.B6724Fi 2009 [Fic]--dc22 2009017025 For Peggy, Liam, and Kerry. My team. One yan Phillips looked around the small huddle of boys standing on the Rwindswept field. It was late afternoon on a crisp autumn day. -

04/12/19 Farm Directionанаvan Trump

Tim Francisco <[email protected]> GOOD MORNING: 04/12/19 Farm Direction Van Trump Report 1 message The Van Trump Report <reply@vantrumpreportemail.com> Fri, Apr 12, 2019 at 7:07 AM ReplyTo: Jordan <replyfec216757c670c7f314_HTML362509461000034501@vantrumpreportemail.com> To: [email protected] “A man who gives you less than what he has to give is telling you what he thinks of you, and telling you what he thinks of himself." Pete Carill 1633, Galileo is Convicted of FRIDAY, APRIL 12, 2019 Heresy On this day in 1633, Printable Copy or Audio Version chief inquisitor Father Vincenzo Maculano da Firenzuola, Morning Summary: Stocks are higher this morning on improved economic data out of appointed by Pope Urban VIII, China. Traders on both sides however continue to ask, where are we in the U.S. begins the inquisition of physicist and financial cycle? And perhaps more importantly what's going to happen to interest rates astronomer Galileo Galilei. Galileo was moving forward? Even though the Fed says they have turned more dovish and some ordered to turn himself in to the Holy inside the market see a rate cut coming, many, including myself, worry that the Fed Office to begin trial for holding the belief could quickly turn more hawkish and actually hike rates if the economy starts to heat that the Earth revolves around the Sun, up. It's not that rising rates are horrible for the stock market, there's been plenty of which was deemed heretical by the times rates have risen and so has the stock market. -

Cavaliers Assistant Coaches Cavaliers General

All-Time Coaches Record All-Time Coaches & General Managers Coach Years Record Pct. Coach Years Record Pct. Bill Fitch 1970-79 304-434 .412 John Lucas 2001-03 37-87 .298 Stan Albeck 1979-80 37-45 .451 Keith Smart 2002-03 9-31 .225 Bill Musselman 1980-82 27-67 .287 Paul Silas 2003-05 69-77 .473 Chuck Daly 1981-82 9-32 .220 Brendan Malone 2005 8-10 .444 Don Delaney 1981-82 7-21 .250 Mike Brown 2005-10, Bob Kloppenburg 1981-82 0-1 .000 2013-14 305-187 .620 Tom Nissalke 1982-84 51-113 .311 Byron Scott 2010-2013 64-166 .386 George Karl 1984-86 61-88 .409 David Blatt 2014-2016 83-40 .675 Gene Littles 1985-86 4-11 .267 Tyronn Lue 2016-2018 128-83 .607 Lenny Wilkens 1986-93 316-258 .551 Larry Drew 2018-2019 19-57 .250 Mike Fratello 1993-99 248-212 .539 John Beilein 2019-2020 14-40 .259 Randy Wittman 1999-2001 62-102 .378 J .B . Bickerstaff 2020-present 5-6 .455 Cavaliers Assistant Coaches Jim Lessig . 1970-71 Richie Adubato . 1993-94 Mark Osowski . 2003-04 Bernie Bickerstaff . 2013-2014 Jimmy Rodgers . 1971-79 Jim Boylan . 1993-97 Stephen Silas . 2003-05 Igor Kokoskov . 2013-2014 Morris McHone . 1979-80, Ron Rothstein . 1993-99 Brendan Malone . 2004-05 Bret Brielmaier . 2013-2016 1984-86 Sidney Lowe . 1994-99 Wes Wilcox . 2005 Jim Boylan . 2013-2018 Larry Creger . 1980-81 Marc Iavaroni . 1997-99 Kenny Natt . 2004-07 Tyronn Lue . 2014-2016 Gerald Oliver .