S D G B the MOSFET

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Advanced MOSFET Structures and Processes for Sub-7 Nm CMOS Technologies

Advanced MOSFET Structures and Processes for Sub-7 nm CMOS Technologies By Peng Zheng A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences in the Graduate Division of the University of California, Berkeley Committee in charge: Professor Tsu-Jae King Liu, Chair Professor Laura Waller Professor Costas J. Spanos Professor Junqiao Wu Spring 2016 © Copyright 2016 Peng Zheng All rights reserved Abstract Advanced MOSFET Structures and Processes for Sub-7 nm CMOS Technologies by Peng Zheng Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences University of California, Berkeley Professor Tsu-Jae King Liu, Chair The remarkable proliferation of information and communication technology (ICT) – which has had dramatic economic and social impact in our society – has been enabled by the steady advancement of integrated circuit (IC) technology following Moore’s Law, which states that the number of components (transistors) on an IC “chip” doubles every two years. Increasing the number of transistors on a chip provides for lower manufacturing cost per component and improved system performance. The virtuous cycle of IC technology advancement (higher transistor density lower cost / better performance semiconductor market growth technology advancement higher transistor density etc.) has been sustained for 50 years. Semiconductor industry experts predict that the pace of increasing transistor density will slow down dramatically in the sub-20 nm (minimum half-pitch) regime. Innovations in transistor design and fabrication processes are needed to address this issue. The FinFET structure has been widely adopted at the 14/16 nm generation of CMOS technology. -

MOS Caps II; Mosfets I

6.012 - Microelectronic Devices and Circuits Lecture 10 - MOS Caps II; MOSFETs I - Outline G cS vGS + SiO2 – • Review - MOS Capacitor (= vGB) The "Delta-Depletion Approximation" n+ (n-MOS example) p-Si Flat-band voltage: VFB ≡ vGB such that φ(0) = φp-Si: VFB = φp-Si – φm Threshold voltage: VT ≡ vGB such B 1/2 * that φ(0) = – φp-Si: VT = VFB – 2φp-Si + [2εSi qNA|2φp-Si| ] /Cox * * Inversion layer sheet charge density: qN = – Cox [vGC – VT] • Charge stores - qG(vGB) from below VFB to above VT Gate Charge: qG(vGB) from below VFB to above VT Gate Capacitance: Cgb(VGB) Sub-threshold charge: qN(vGB) below VT • 3-Terminal MOS Capacitors - Bias between B and C Impact is on VT(vBC): |2φp-Si| → (|2φp-Si| - vBC) • MOS Field Effect Transistors - Basics of model Gradual Channel Model: electrostatics problem normal to channel drift problem in the plane of the channel Clif Fonstad, 10/15/09 Lecture 10 - Slide 1 G CS vGS + SiO2 – (= vGB) The n-MOS capacitor n+ Right: Basic device p-Si with vBC = 0 B Below: One-dimensional structure for depletion approximation analysis* vGB + – SiO 2 p-Si G B x -tox 0 * Note: We can't forget the n+ region is there; we Clif Fonstad, 10/15/09 will need electrons, and they will come from there. Lecture 10 - Slide 2 MOS Capacitors: Where do the electrons in the inversion layer come from? Diffusion from the p-type substrate? If we relied on diffusion of minority carrier electrons from the p-type substrate it would take a long time to build up the inversion layer charge. -

Photovoltaic Couplers for MOSFET Drive for Relays

Photocoupler Application Notes Basic Electrical Characteristics and Application Circuit Design of Photovoltaic Couplers for MOSFET Drive for Relays Outline: Photovoltaic-output photocouplers(photovoltaic couplers), which incorporate a photodiode array as an output device, are commonly used in combination with a discrete MOSFET(s) to form a semiconductor relay. This application note discusses the electrical characteristics and application circuits of photovoltaic-output photocouplers. ©2019 1 Rev. 1.0 2019-04-25 Toshiba Electronic Devices & Storage Corporation Photocoupler Application Notes Table of Contents 1. What is a photovoltaic-output photocoupler? ............................................................ 3 1.1 Structure of a photovoltaic-output photocoupler .................................................... 3 1.2 Principle of operation of a photovoltaic-output photocoupler .................................... 3 1.3 Basic usage of photovoltaic-output photocouplers .................................................. 4 1.4 Advantages of PV+MOSFET combinations ............................................................. 5 1.5 Types of photovoltaic-output photocouplers .......................................................... 7 2. Major electrical characteristics and behavior of photovoltaic-output photocouplers ........ 8 2.1 VOC-IF characteristics .......................................................................................... 9 2.2 VOC-Ta characteristic ........................................................................................ -

Fundamentals of MOSFET and IGBT Gate Driver Circuits

Application Report SLUA618A–March 2017–Revised October 2018 Fundamentals of MOSFET and IGBT Gate Driver Circuits Laszlo Balogh ABSTRACT The main purpose of this application report is to demonstrate a systematic approach to design high performance gate drive circuits for high speed switching applications. It is an informative collection of topics offering a “one-stop-shopping” to solve the most common design challenges. Therefore, it should be of interest to power electronics engineers at all levels of experience. The most popular circuit solutions and their performance are analyzed, including the effect of parasitic components, transient and extreme operating conditions. The discussion builds from simple to more complex problems starting with an overview of MOSFET technology and switching operation. Design procedure for ground referenced and high side gate drive circuits, AC coupled and transformer isolated solutions are described in great details. A special section deals with the gate drive requirements of the MOSFETs in synchronous rectifier applications. For more information, see the Overview for MOSFET and IGBT Gate Drivers product page. Several, step-by-step numerical design examples complement the application report. This document is also available in Chinese: MOSFET 和 IGBT 栅极驱动器电路的基本原理 Contents 1 Introduction ................................................................................................................... 2 2 MOSFET Technology ...................................................................................................... -

Power MOSFET Basics by Vrej Barkhordarian, International Rectifier, El Segundo, Ca

Power MOSFET Basics By Vrej Barkhordarian, International Rectifier, El Segundo, Ca. Breakdown Voltage......................................... 5 On-resistance.................................................. 6 Transconductance............................................ 6 Threshold Voltage........................................... 7 Diode Forward Voltage.................................. 7 Power Dissipation........................................... 7 Dynamic Characteristics................................ 8 Gate Charge.................................................... 10 dV/dt Capability............................................... 11 www.irf.com Power MOSFET Basics Vrej Barkhordarian, International Rectifier, El Segundo, Ca. Discrete power MOSFETs Source Field Gate Gate Drain employ semiconductor Contact Oxide Oxide Metallization Contact processing techniques that are similar to those of today's VLSI circuits, although the device geometry, voltage and current n* Drain levels are significantly different n* Source t from the design used in VLSI ox devices. The metal oxide semiconductor field effect p-Substrate transistor (MOSFET) is based on the original field-effect Channel l transistor introduced in the 70s. Figure 1 shows the device schematic, transfer (a) characteristics and device symbol for a MOSFET. The ID invention of the power MOSFET was partly driven by the limitations of bipolar power junction transistors (BJTs) which, until recently, was the device of choice in power electronics applications. 0 0 V V Although it is not possible to T GS define absolutely the operating (b) boundaries of a power device, we will loosely refer to the I power device as any device D that can switch at least 1A. D The bipolar power transistor is a current controlled device. A SB (Channel or Substrate) large base drive current as G high as one-fifth of the collector current is required to S keep the device in the ON (c) state. Figure 1. Power MOSFET (a) Schematic, (b) Transfer Characteristics, (c) Also, higher reverse base drive Device Symbol. -

Extending the Road Beyond CMOS

By James A. Hutchby, George I. Bourianoff, Victor V. Zhirnov, and Joe E. Brewer he quickening pace of MOSFET technology scaling, as seen in the new 2001 International Technology Roadmap for Semiconductors [1], is ac- celerating the introduction of many new technologies to extend CMOS Tinto nanoscale MOSFET structures heretofore not thought possible. A cautious optimism is emerging that these new technologies may extend MOSFETs to the 22-nm node (9-nm physical gate length) by 2016 if not by the end of this decade. These new devices likely will feature several new materials cleverly incorporated into new nonbulk MOSFET structures. They will be ultra fast and dense with a voracious appetite for power. Intrinsic device speeds may be more than 1 THz and integration densities will exceed 1 billion transistors per cm2. Excessive power consumption, however, will demand judicious use of these high-performance devices only in those critical paths requiring their su- perior performance. Two or perhaps three other lower performance, more power-efficient MOSFETs will likely be used to perform less performance-criti- cal functions on the chip to manage the total power consumption. Beyond CMOS, several completely new approaches to information-process- ing and data-storage technologies and architectures are emerging to address the timeframe beyond the current roadmap. Rather than vying to “replace” CMOS, one or more of these embryonic paradigms, when combined with a CMOS plat- form, could extend microelectronics to new applications domains currently not accessible to CMOS. A successful new information-processing paradigm most likely will require a new platform technology embodying a fabric of intercon- nected primitive logic cells, perhaps in three dimensions. -

Basics of CMOS Logic Ics Application Note

Basics of CMOS Logic ICs Application Note Basics of CMOS Logic ICs Outline: This document describes applications, functions, operations, and structure of CMOS logic ICs. Each functions (inverter, buffer, flip-flop, etc.) are explained using system diagrams, truth tables, timing charts, internal circuits, image diagrams, etc. ©2020- 2021 1 2021-01-31 Toshiba Electronic Devices & Storage Corporation Basics of CMOS Logic ICs Application Note Table of Contents Outline: ................................................................................................................................................. 1 Table of Contents ................................................................................................................................. 2 1. Standard logic IC ............................................................................................................................. 3 1.1. Devices that use standard logic ICs ................................................................................................. 3 1.2. Where are standard logic ICs used? ................................................................................................ 3 1.3. What is a standard logic IC? .............................................................................................................. 4 1.4. Classification of standard logic ICs ................................................................................................... 5 1.5. List of basic circuits of CMOS logic ICs (combinational logic circuits) -

Basic Design of MOSFET, Four-Phase, Digital Integrated Circuits

Scholars' Mine Masters Theses Student Theses and Dissertations 1969 Basic design of MOSFET, four-phase, digital integrated circuits Earl Morris Worstell Follow this and additional works at: https://scholarsmine.mst.edu/masters_theses Part of the Electrical and Computer Engineering Commons Department: Recommended Citation Worstell, Earl Morris, "Basic design of MOSFET, four-phase, digital integrated circuits" (1969). Masters Theses. 5304. https://scholarsmine.mst.edu/masters_theses/5304 This thesis is brought to you by Scholars' Mine, a service of the Missouri S&T Library and Learning Resources. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact [email protected]. BASIC DESIGN OF MOSFET, FOUR-PHASE, DIGITAL INTEGRATED CIRCUITS By t_fL/ () Earl Morris Worstell , Jr./ J q¥- 2., A Thesis submitted to the faculty of THE UNIVERSITY OF MISSOURI - ROLLA in partial fulfillment of the requirements for the Degree of MASTER OF SCIENCE IN ELECTRICAL ENGINEERING Ro 11 a , M i sous ri 1969 Approved By i BASIC DESIGN OF MOSFET, FOUR-PHASE, DIGITAL INTEGRATED CIRCUITS by Earl M. Worstell, Jr. Abstract MOSFET is defined as metal oxide semiconductor field-effect transis tor. The integrated circuit design relates strictly to logic and switch ing circuits rather than linear circuits. The design of MOS circuits is primarily one of charge and discharge of stray capacitance through MOSFETS used as switches and active loads. To better take advantage of the possibilities of MOS technology, four phase (4¢) circuitry is developed. It offers higher speeds and lower power while permitting higher circuit density than does static or two phase (2cj>) logic. -

A Graphene/Polycrystalline Silicon Photodiode and Its Integration in a Photodiode–Oxide–Semiconductor Field Effect Transistor

micromachines Article A Graphene/Polycrystalline Silicon Photodiode and Its Integration in a Photodiode–Oxide–Semiconductor Field Effect Transistor Yu-Yang Tsai, Chun-Yu Kuo, Bo-Chang Li, Po-Wen Chiu and Klaus Y. J. Hsu * Institute of Electronics Engineering, National Tsing Hua University, Hsinchu 30013, Taiwan; [email protected] (Y.-Y.T.); [email protected] (C.-Y.K.); [email protected] (B.-C.L.); [email protected] (P.-W.C.) * Correspondence: [email protected]; Tel.: +886-3-574-2594 Received: 25 May 2020; Accepted: 15 June 2020; Published: 17 June 2020 Abstract: In recent years, the characteristics of the graphene/crystalline silicon junction have been frequently discussed in the literature, but study of the graphene/polycrystalline silicon junction and its potential applications is hardly found. The present work reports the observation of the electrical and optoelectronic characteristics of a graphene/polycrystalline silicon junction and explores one possible usage of the junction. The current–voltage curve of the junction was measured to show the typical exponential behavior that can be seen in a forward biased diode, and the photovoltage of the junction showed a logarithmic dependence on light intensity. A new phototransistor named the “photodiode–oxide–semiconductor field effect transistor (PDOSFET)” was further proposed and verified in this work. In the PDOSFET, a graphene/polycrystalline silicon photodiode was directly merged on top of the gate oxide of a conventional metal–oxide–semiconductor field effect transistor (MOSFET). The magnitude of the channel current of this phototransistor showed a logarithmic dependence on the illumination level. It is shown in this work that the PDOSFET facilitates a better pixel design in a complementary metal–oxide–semiconductor (CMOS) image sensor, especially beneficial for high dynamic range (HDR) image detection. -

AN-500: Depletion-Mode Power Mosfets and Applications

INTEGRATED CIRCUITS DIVISION Application Note AN-500 Depletion-Mode Power MOSFETs and Applications AN-500-R03 www.ixysic.com 1 INTEGRATED CIRCUITS DIVISION AN-500 1 Introduction Applications like constant current sources, solid state relays, and high voltage DC lines in power systems require N-channel depletion-mode power MOSFETs that operate as normally-on switches when the gate-to-source voltage is zero (VGS=0V). This paper will describe IXYS IC Division’s latest N-channel, depletion-mode, power MOSFETs and their application advantages to help designers to select these devices in many industrial applications. Figure 1 N-Channel Depletion-Mode MOSFET D ID + G V + DS IG V - GS I - S S A circuit symbol for an N-channel depletion-mode power MOSFET is given in Figure 1. The terminals are labeled as G (gate), S (source) and D (drain). IXYS IC Division depletion-mode power MOSFETs are built with a structure called vertical double-diffused MOSFET, or DMOSFET, and have better performance characteristics when compared to other depletion-mode power MOSFETs on the market such as high VDSX, high current, and high forward biased safe operating area (FBSOA). Figure 2 shows a typical drain current characteristic, ID, versus the drain-to-source voltage, VDS, which is called the output characteristic. It’s a similar plot to that of an N-channel enhancement mode power MOSFET except that it has current lines at VGS equal to -2V, -1.5V, -1V, and 0V. Figure 2 CPC3710 - MOSFET Output Characteristics Output Characteristics (TA=25ºC) 300 270 VGS=0.0V 240 210 V =-1.0V 180 GS 150 (mA) D I 120 V =-1.5V 90 GS 60 V =-2.0V 30 GS 0 0123456 VDS (V) The on-state drain current, IDSS, a parameter defined in the datasheet, is the current that flows between the drain and the source at a particular drain-to-source voltage (VDS), when the gate-to-source voltage (VGS) is zero (or short-circuited). -

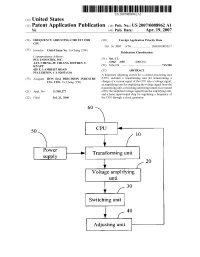

Y F 20 Voltage Amplifying Unti K 3 O Switching Unit

US 20070088962Al (19) United States (12) Patent Application Publication (10) Pub. No.: US 2007/0088962 A1 Yu (43) Pub. Date: Apr. 19, 2007 (54) FREQUENCY ADJUSTING CIRCUIT FOR (30) Foreign Application Priority Data CPU Oct. 14, 2005 (CN) ............................ .. 2005101003597 (75) Inventor: Chia-Chuan Yu, Tu-Cheng (TW) Publication Classi?cation Correspondence Address: PCE INDUSTRY, INC. (51) Int. Cl. ATT. CHENG-JU CHIANG JEFFREY T. G06F 1/00 (2006.01) KNAPP (52) U.S. c1. ............................................................ ..713/300 458 E. LAMBERT ROAD (57) ABSTRACT FULLERTON, CA 92835 (US) A frequency adjusting circuit for a central processing unit (73) Assignee: HON HAI PRECISION INDUSTRY (CPU) includes a transforming unit for transforming a CO., LTD., Tu-Cheng (TW) change of a current signal of the CPU into a Voltage signal, an amplifying unit for amplifying the Voltage signal from the transforming unit, a switching unit being turned on or turned (21) Appl, NQ; 11/309,277 oif by the ampli?ed Voltage signal from the amplifying unit, and a basic input/output chip for regulating a frequency of (22) Filed: Jul. 21, 2006 the CPU through a clock generator. 60 50 CPU 4 l 0 Power . supply —> Transformlng unit y f 20 Voltage amplifying unti K 3 O Switching unit 40 K Adjusting unit Patent Application Publication Apr. 19, 2007 Sheet 1 0f 2 US 2007/0088962 A1 5O CPU '4 \ l / 1° Power . supply —> Transfonnlng unit 4 K 20 Voltage amplifying unti l r 30 Switching unit l r 40 Adjusting unit FIG. 1 Patent Application Publication Apr. 19, 2007 Sheet 2 0f 2 US 2007/0088962 A1 _ _ _ _ _M86 _5:22am N.65 US 2007/0088962 A1 Apr. -

Research Needs Document: Logic and Memory Devices March 2015 Semiconductor Research Corp

Research Needs Document: Logic and Memory Devices March 2015 Semiconductor Research Corp. (SRC) P.O. Box 12053 Research Triangle Park, NC 27709-2053 Background This document is prepared to accompany the Call-for-White-Papers for the thrust of Logic and Memory Devices. The research needs in this area are very wide. We present here selected areas of high priorities as identified by our sponsor members. In an integrated circuit, transistors and memories are the most important and common components. For transistors, the natural progression beyond the current manufacturing technologies, SOI planar MOSFETs and FinFETs, will be nanowire MOSFETs, all based on Si channel materials. Other than these Si MOSFET structures, there are potential benefits to be gained by going to other alternate channel materials with high mobilities, such as different versions of III-V compounds, SixGe1-x compound or pure Ge, graphene, carbon nanotube, 2-D crystals, etc. It is believed that even though mobility is a low-field phenomenon, its more favorable scattering process can lead to higher high-field saturation velocity or ballistic velocity, which in term can result in larger current. Common MOSFET devices encounter one common fundamental limitation of MOSFET principle–a subthreshold slope of 60 mV/decade. This places a lower limit on the operational voltage given the required on-current to off-current ratio. There is a group of logic devices that based on different material and device physics and can lead to subthreshold slope steeper than this fundamental limit. A few approaches are being examined. One is based on gate-control tunneling as in tunnel FET (TFET), because tunneling is not limited by the kT/q factor.