Computer-Controlled Teletext Decoder

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Alpha Eta Rho Mu Kappa Tau Chapter Minnesota State University, Mankato By-Laws

ALPHA ETA RHO MU KAPPA TAU CHAPTER MINNESOTA STATE UNIVERSITY, MANKATO BY-LAWS ARTICLE I- Name and Philosophy Section 1. NAME. This Fraternity shall be officially known as Alpha Eta Rho Mu Kappa Tau Chapter. Section 2. PHILOSOPHY. It is the philosophy of Alpha Eta Rho Mu Kappa Tau Chapter to exhibit a professional approach and attitude toward aviation. Alpha Eta Rho Mu Kappa Tau Chapter is not to conduct itself as a social Fraternity in any of the events it sponsors. However, this shall not exclude the Fraternity from promoting fellowship among its membership, nor should it prohibit the Fraternity from accepting invitations or requests from other organizations, professional or social. ARTICLE II- Chapter Officers, Their Powers and Duties Section 1. PRESIDENT. The president shall have been an active member for one year prior to taking office. The president shall uphold and administer the laws and philosophy of the Fraternity. He or she shall preside over all meetings and help organize all activities. The president will be the representative of the Fraternity to other organizations, departments, faculty, and etceteras. It is also the responsibly of the president to delegate individual tasks or roles to the appropriate officer or committees. Section 2. VICE-PRESIDENT. The vice-president shall have been an active member for one year prior to taking office. The vice-president shall assist the president in his or her duties and shall also substitute for the president in his or her absence. The vice-president shall be responsible for educating the pledge class. Section 3. SECRETARY/HISTORIAN. The secretary and historian shall have been an active member for one year piorr to taking office. -

AIX Globalization

AIX Version 7.1 AIX globalization IBM Note Before using this information and the product it supports, read the information in “Notices” on page 233 . This edition applies to AIX Version 7.1 and to all subsequent releases and modifications until otherwise indicated in new editions. © Copyright International Business Machines Corporation 2010, 2018. US Government Users Restricted Rights – Use, duplication or disclosure restricted by GSA ADP Schedule Contract with IBM Corp. Contents About this document............................................................................................vii Highlighting.................................................................................................................................................vii Case-sensitivity in AIX................................................................................................................................vii ISO 9000.....................................................................................................................................................vii AIX globalization...................................................................................................1 What's new...................................................................................................................................................1 Separation of messages from programs..................................................................................................... 1 Conversion between code sets............................................................................................................. -

Constitution of the Mu Eta Chapter of Sigma Alpha Mu Fraternity

1 Constitution of the Mu Eta Chapter of Sigma Alpha Mu Fraternity . Division I: Name and Purpose o Article 1: Name . The name of this social fraternity shall be: Mu Eta Chapter of Sigma Alpha Mu. o Article 2: Purpose . The purpose of these bylaws is to govern the affairs of Mu Eta Chapter in accordance with the rules of the Blue Book, and to provide regulations for the proper functioning of the Mu Eta Chapter. o Article 3: Conflicts . In event of conflict between these by-laws and the Blue Book, the Blue Book shall stand supreme. Division II: Definitions o The following are terms for these bylaws and will be defined as the following: . Candidate - A person that is going through Candidate Education. Chapter Bad Standing – Temporarily not allowed at any Fraternity function until cleared by council. Committee - A number of people, to be determined by council or specific chairman, to assist said chairman in maintaining and organizing such duties as described in Division IV, Article 3, Section C (Organization, Chairmen, Chairmen and Committee Responsibilities). Consequence - A stipulated punishment as determined by council or Judicial Board. Dues - A stipulated amount of money owed each term by every member. Fine - A type of Consequence; A stipulated amount of money or probation as determined by Council or Judicial Board. 2 . Full-time student - A student who is taking no less than the minimum number of term credits as defined by Drexel University to qualify as a full-time student. Good Standing - Not in bad standing, as per Division III, Article 5 (Membership, Bad Standing), and active as per Division III, Article 3 (Membership, Active). -

International Language Environments Guide

International Language Environments Guide Sun Microsystems, Inc. 4150 Network Circle Santa Clara, CA 95054 U.S.A. Part No: 806–6642–10 May, 2002 Copyright 2002 Sun Microsystems, Inc. 4150 Network Circle, Santa Clara, CA 95054 U.S.A. All rights reserved. This product or document is protected by copyright and distributed under licenses restricting its use, copying, distribution, and decompilation. No part of this product or document may be reproduced in any form by any means without prior written authorization of Sun and its licensors, if any. Third-party software, including font technology, is copyrighted and licensed from Sun suppliers. Parts of the product may be derived from Berkeley BSD systems, licensed from the University of California. UNIX is a registered trademark in the U.S. and other countries, exclusively licensed through X/Open Company, Ltd. Sun, Sun Microsystems, the Sun logo, docs.sun.com, AnswerBook, AnswerBook2, Java, XView, ToolTalk, Solstice AdminTools, SunVideo and Solaris are trademarks, registered trademarks, or service marks of Sun Microsystems, Inc. in the U.S. and other countries. All SPARC trademarks are used under license and are trademarks or registered trademarks of SPARC International, Inc. in the U.S. and other countries. Products bearing SPARC trademarks are based upon an architecture developed by Sun Microsystems, Inc. SunOS, Solaris, X11, SPARC, UNIX, PostScript, OpenWindows, AnswerBook, SunExpress, SPARCprinter, JumpStart, Xlib The OPEN LOOK and Sun™ Graphical User Interface was developed by Sun Microsystems, Inc. for its users and licensees. Sun acknowledges the pioneering efforts of Xerox in researching and developing the concept of visual or graphical user interfaces for the computer industry. -

Mu Alpha Theta High School Scholarships 2020-2021

Mu Alpha Theta High School Scholarships 2020-2021 Mu Alpha Theta Scholarships are for exceptional, graduating high school seniors who are members in good standing of an active Mu Alpha Theta chapter. Recipients will have advanced the mission of Mu Alpha Theta by excelling as mathematics students, providing exemplary leadership and loyalty to their Mu Alpha Theta chapters, participating enthusiastically in local projects, and providing service in the area of mathematics. A number of these $4,000 scholarships will be available each year. Scholarships will be sent to the recipient’s college to be used for educational expenses within 18 months of award notification. In order to receive these funds, recipients must be enrolled full-time at an accredited college or university. The Kalin Award is named in honor of Dr. Robert Kalin, a former president of Mu Alpha Theta. A Kalin Award nominee must be a student who is representative of all student members who excel in mathematics and who has provided notable service to Mu Alpha Theta. Nominees must be graduating high school seniors who will begin college in the year the award is made. The current award amount is $4,000, which may be taken as a cash prize or as a scholarship. The winner’s school will receive a $1,000 chapter grant. Top candidates for the award must attend our national convention with their chapter and will be interviewed in person by our Governing Council. Interviewed finalists who do not win the award will each receive a $500 cash prize. There is a separate application for this award. -

Section 18.1, Han

The Unicode® Standard Version 13.0 – Core Specification To learn about the latest version of the Unicode Standard, see http://www.unicode.org/versions/latest/. Many of the designations used by manufacturers and sellers to distinguish their products are claimed as trademarks. Where those designations appear in this book, and the publisher was aware of a trade- mark claim, the designations have been printed with initial capital letters or in all capitals. Unicode and the Unicode Logo are registered trademarks of Unicode, Inc., in the United States and other countries. The authors and publisher have taken care in the preparation of this specification, but make no expressed or implied warranty of any kind and assume no responsibility for errors or omissions. No liability is assumed for incidental or consequential damages in connection with or arising out of the use of the information or programs contained herein. The Unicode Character Database and other files are provided as-is by Unicode, Inc. No claims are made as to fitness for any particular purpose. No warranties of any kind are expressed or implied. The recipient agrees to determine applicability of information provided. © 2020 Unicode, Inc. All rights reserved. This publication is protected by copyright, and permission must be obtained from the publisher prior to any prohibited reproduction. For information regarding permissions, inquire at http://www.unicode.org/reporting.html. For information about the Unicode terms of use, please see http://www.unicode.org/copyright.html. The Unicode Standard / the Unicode Consortium; edited by the Unicode Consortium. — Version 13.0. Includes index. ISBN 978-1-936213-26-9 (http://www.unicode.org/versions/Unicode13.0.0/) 1. -

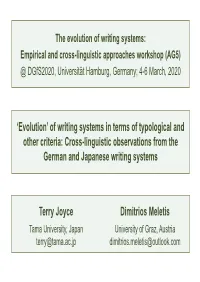

Of Writing Systems in Terms of Typological and Other Criteria: Cross-Linguistic Observations from the German and Japanese Writing Systems

The evolution of writing systems: Empirical and cross-linguistic approaches workshop (AG5) @ DGfS2020, Universität Hamburg, Germany; 4-6 March, 2020 ‘Evolution’ of writing systems in terms of typological and other criteria: Cross-linguistic observations from the German and Japanese writing systems Terry Joyce Dimitrios Meletis Tama University, Japan University of Graz, Austria [email protected] [email protected] Overview Opening remarks Selective sample of writing system (WS) typologies Alternative criteria for evaluating WSs Observations from German (GWS) + Japanese (JWS) Closing remarks Opening remarks 1: Chaos over basic terminology! Erring towards understatement, Gnanadesikan (2017: 15) notes, [t]here is, in general, significant variation in the basic terminology used in the study of writing systems. Indeed, as Meletis (2018: 73) observes regarding the differences between the concepts of WS and orthography, [t]hese terms are often shockingly misused as synonyms, or writing system is not used at all and orthography is employed instead. Similarly, Joyce and Masuda (in press) seek to differentiate between the elusive trinity of terms at heart of WS research; namely, script, WS, and orthography, with particular reference to the JWS. Opening remarks 2: Our working definitions WS1 [Schrifttyp]: Abstract relations (i.e., morphographic, syllabographic, + phonemic), as focus of typologies. WS2 [Schriftsystem]: Common usage for signs + conventions of given language, such as GWS + JWS. Script [Schrift]: Set of material signs for specific language. Orthography [Orthographie]: Mediation between script + WS, but often with prescriptive connotations of correct writing. Graphematic representation: Emerging from grapholinguistic approach, a neutral (ego preferable) alternative to orthography. GWS: Use of extended alphabetic set, as used to represent written German language. -

Alpha Kappa Alpha Sorority, Inc. Psi Mu Omega Chapter Pink and Green Charitable Foundation 2019 Scholarship Application

Alpha Kappa Alpha Sorority, Inc. Psi Mu Omega Chapter Pink and Green Charitable Foundation 2019 Scholarship Application The completed application must be postmarked and mailed by February 01, 2019 (No emails or Hand Delivered Applications will be accepted) to: Alpha Kappa Alpha Sorority, Inc., Psi Mu Omega Chapter Attention: Kim Warren P.O. Box 841723 Pearland, Texas 77584 Alpha Kappa Alpha Sorority, Inc. Psi Mu Omega Chapter and Pink and Green Foundation is awarding a One-Time Scholarship to assist African-American students with educational expenses associated with attendance at a higher education institution. Please check All Scholarship (s) in which you are applying: I am applying for Community Scholarship ______ (Applicant must reside in Brazoria County, Proof of Residence is required) I am applying for Family (Chapter Member) Scholarship ______ (Applicant must have a Parent or Grandparent that is active in the Psi Mu Omega AKA chapter) I am applying for Ginger D. Worthington Leadership Scholarship ______ (Applicant must show Leadership qualities) I am applying for Historically Black Colleges and Universities Scholarship ______ (Applicant must attend a HBCU school, Visit website provided to see if the college that you are attending qualifies, https://www.usnews.com/best-colleges/rankings/hbcu) Scholarship Criteria: Must be of African American origin and a 2019 graduating senior Attend one of the following high schools: Alvin, Angleton, Brazosport, Brazoswood, Dawson, Manvel, Turner, Pearland or Shadowcreek. Must be enrolled in a two or four year college or university Fall of 2019 Must have a high school overall grade point average of 2.5 or above on 4.0 scale Applicant should have demonstrated at least 25 or more hours of community service Applicant must submit a 250-300 (maximum) word response to EACH of the questions located in the Scholarship Application. -

Integrated VIP and Teletext Decoder (IVT1.1)

INTEGRATED CIRCUITS DATA SHEET SAA5244A Integrated VIP and teletext decoder (IVT1.1) Product specification March 1992 File under Integrated Circuits, IC02 Philips Semiconductors Product specification Integrated VIP and teletext decoder SAA5244A (IVT1.1) FEATURES • Complete teletext decoder including page memory in a single 40-pin DIL package • Single +5 V power supply • Digital data slicer and display clock phase-locked loop reduces peripheral components to a minimum • Both video and scan related synchronization modes are DESCRIPTION supported The Integrated VIP and Teletext (IVT1.1) is a teletext • On board single page memory including extension decoder (contained within a single-chip package) for packets for FASTEXT decoding 625-line based World System Teletext • Single page acquisition system transmissions. The teletext decoder hardware is based on • RGB interface to standard colour decoder ICs, push-pull a reduced function version of the device SAA5246 output drive (IVT1.0). • Data capture performance similar to SAA5231 (VIP2) The Video Input Processor (VIP) section of the device uses mixed analog and digital designs for the data slicer • Simple software control via I2C-bus and the display clock phase-locked loop functions. As a • Option for five national languages result the number of external components is greatly • 32 supplementary characters for on-screen displays reduced and no critical or adjustable components are required. A single page static RAM is incorporated in the • Optional storage of packet 24 in the display memory device -

Mu Alpha Theta Officer Requirements and Application

Mu Alpha Theta Officer Requirements and Application The following list details the job requirements for the offices of Mu Alpha Theta. President – The President is IN CHARGE of planning the officer meetings as well as the monthly meetings. The President must be extremely organized and able to follow through on ideas and plans. The President must be dedicated to making Mu Alpha Theta interesting and educational. Much of the responsibility for the success of Mu Alpha Theta lies with the performance of the President. The President must attend all officers’ meetings and all meetings of the members. The President is in charge of the Blood Drive which includes meeting with Hoxworth representative, organizing schedule, letters and permission slips. Vice President – The Vice President is responsible for performing the job of the President in the President’s absence. The Vice President assists the President in planning the meetings for the Mu Alpha Theta members. This officer serves more in an undefined manner and MUST be willing to volunteer for and accept miscellaneous tasks. The Vice President must attend all officers’ meetings and all meetings of the members. The Vice President is IN CHARGE of the Peer Tutoring Program and elections for the following year. The Vice President will be in charge of one of the member meetings. Treasurer – The Treasurer is responsible for collecting and managing the funds for the group. This officer must maintain a high level of integrity. This person is responsible for collecting funds. The Treasurer must attend all officers’ meetings and all meetings of the members. The Treasurer is in charge of Pi-Day Activities which includes arranging location, schedule, activities and “pies”. -

Constitution Eta Mu Sigma National Honor Society 02-27-2018 Article I

Constitution Eta Mu Sigma National Honor Society 02-27-2018 Preamble The Eta Mu Sigma National Honor Society is established to recognize and honor those individuals in the Majors and Minors in the Aviation curriculum who have, through scholarship and outstanding achievement, been a credit to their college. The primary functions of the society are to stimulate and encourage professional development through high academic performance, develop spiritual and intellectual leadership skills among society members, and provide a medium of communication between individuals in the industry and members of the society. The mission of the Society is to promote service in the community. Article I. Name and Affiliations Section 1. The name of the society will be Eta Mu Sigma National Honor Society. It may be referred to plainly as the Society or Eta Mu Sigma. Section 2. The organization represents students in the Aviation Curriculum. Section 3. The Symbol of the Society will have the form depicted in Appendix A. This symbol may be utilized only by members of the Society. It will be utilized only in conjunction with the Society’s purposes and sanctioned events. Section 4. The Seal of the Society will have the form depicted in Appendix B. This Seal may be utilized only by members of the Society. It will be utilized only in conjunction with the Society’s purposes and sanctioned events. Section 5. The colors of the society will be Blue and White. Section 6. Chapters will be named after their respective schools. 1 Constitution & By Laws Eta Mu Sigma National Honor Society 02-27-2018 Article II. -

The Unicode Standard, Version 3.0, Issued by the Unicode Consor- Tium and Published by Addison-Wesley

The Unicode Standard Version 3.0 The Unicode Consortium ADDISON–WESLEY An Imprint of Addison Wesley Longman, Inc. Reading, Massachusetts · Harlow, England · Menlo Park, California Berkeley, California · Don Mills, Ontario · Sydney Bonn · Amsterdam · Tokyo · Mexico City Many of the designations used by manufacturers and sellers to distinguish their products are claimed as trademarks. Where those designations appear in this book, and Addison-Wesley was aware of a trademark claim, the designations have been printed in initial capital letters. However, not all words in initial capital letters are trademark designations. The authors and publisher have taken care in preparation of this book, but make no expressed or implied warranty of any kind and assume no responsibility for errors or omissions. No liability is assumed for incidental or consequential damages in connection with or arising out of the use of the information or programs contained herein. The Unicode Character Database and other files are provided as-is by Unicode®, Inc. No claims are made as to fitness for any particular purpose. No warranties of any kind are expressed or implied. The recipient agrees to determine applicability of information provided. If these files have been purchased on computer-readable media, the sole remedy for any claim will be exchange of defective media within ninety days of receipt. Dai Kan-Wa Jiten used as the source of reference Kanji codes was written by Tetsuji Morohashi and published by Taishukan Shoten. ISBN 0-201-61633-5 Copyright © 1991-2000 by Unicode, Inc. All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, recording or other- wise, without the prior written permission of the publisher or Unicode, Inc.