Fpgas As Components in Heterogeneous HPC Systems: Raising the Abstraction Level of Heterogeneous Programming

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

ECE Illinois WINTER2005.Indd

Electrical and Computer Engineering Alumni News ECE Alumni Association newsletter University of Illinois at Urbana-Champaign Winter 2005-2006 Jack Kilby, 1923–2005 Volume XL Cancer claims Nobel laureate, ECE alumnus By Laura Schmitt and Jamie Hutchinson Inside this issue Microchip inventor and Nobel physics laureate DEPARTMENT HEAD’S Jack Kilby (BSEE ’47) died from cancer on MESSAGE June 22, 2005. He was 81. Kilby received the 2000 Nobel Prize in 2 Physics on December 10, 2001, in an award ceremony in Stockholm, Sweden. Kilby was ROOM-TEMPERATURE LASER recognized for his part in the invention and 4 development of the integrated circuit, which he first demonstrated on September 12, 1958, while at Texas Instruments. At the Nobel awards ceremony, Royal Swedish Academy member Tord Claesen called that date “one of the most important birth dates in the history of technology.” A measure of Kilby’s importance can be seen in the praise that was lavished on him in death. Lengthy obituaries appeared in engi- Jack Kilby neering and science trade publications as well FEATURED ALUMNI CAREERS as in major newspapers worldwide, including where his interest in electricity and electron- the New York Times, Financial Times, and The ics blossomed at an early age. His father ran a 29 Economist. On June 24, ABC News honored power company that served a wide area in rural Kilby by naming him its Person of the Week. Kansas, and he used amateur radio to keep in Reporter Elizabeth Vargas introduced the contact with customers during emergencies. segment by noting that Kilby’s invention During an ice storm, the teenage Kilby saw “had a direct effect on billions of people in the firsthand how electronic technology could world,” despite his relative anonymity among positively impact people’s lives. -

Historical Perspective and Further Reading 162.E1

2.21 Historical Perspective and Further Reading 162.e1 2.21 Historical Perspective and Further Reading Th is section surveys the history of in struction set architectures over time, and we give a short history of programming languages and compilers. ISAs include accumulator architectures, general-purpose register architectures, stack architectures, and a brief history of ARMv7 and the x86. We also review the controversial subjects of high-level-language computer architectures and reduced instruction set computer architectures. Th e history of programming languages includes Fortran, Lisp, Algol, C, Cobol, Pascal, Simula, Smalltalk, C+ + , and Java, and the history of compilers includes the key milestones and the pioneers who achieved them. Accumulator Architectures Hardware was precious in the earliest stored-program computers. Consequently, computer pioneers could not aff ord the number of registers found in today’s architectures. In fact, these architectures had a single register for arithmetic instructions. Since all operations would accumulate in one register, it was called the accumulator , and this style of instruction set is given the same name. For example, accumulator Archaic EDSAC in 1949 had a single accumulator. term for register. On-line Th e three-operand format of RISC-V suggests that a single register is at least two use of it as a synonym for registers shy of our needs. Having the accumulator as both a source operand and “register” is a fairly reliable indication that the user the destination of the operation fi lls part of the shortfall, but it still leaves us one has been around quite a operand short. Th at fi nal operand is found in memory. -

John Mccarthy

JOHN MCCARTHY: the uncommon logician of common sense Excerpt from Out of their Minds: the lives and discoveries of 15 great computer scientists by Dennis Shasha and Cathy Lazere, Copernicus Press August 23, 2004 If you want the computer to have general intelligence, the outer structure has to be common sense knowledge and reasoning. — John McCarthy When a five-year old receives a plastic toy car, she soon pushes it and beeps the horn. She realizes that she shouldn’t roll it on the dining room table or bounce it on the floor or land it on her little brother’s head. When she returns from school, she expects to find her car in more or less the same place she last put it, because she put it outside her baby brother’s reach. The reasoning is so simple that any five-year old child can understand it, yet most computers can’t. Part of the computer’s problem has to do with its lack of knowledge about day-to-day social conventions that the five-year old has learned from her parents, such as don’t scratch the furniture and don’t injure little brothers. Another part of the problem has to do with a computer’s inability to reason as we do daily, a type of reasoning that’s foreign to conventional logic and therefore to the thinking of the average computer programmer. Conventional logic uses a form of reasoning known as deduction. Deduction permits us to conclude from statements such as “All unemployed actors are waiters, ” and “ Sebastian is an unemployed actor,” the new statement that “Sebastian is a waiter.” The main virtue of deduction is that it is “sound” — if the premises hold, then so will the conclusions. -

John Mccarthy – Father of Artificial Intelligence

Asia Pacific Mathematics Newsletter John McCarthy – Father of Artificial Intelligence V Rajaraman Introduction I first met John McCarthy when he visited IIT, Kanpur, in 1968. During his visit he saw that our computer centre, which I was heading, had two batch processing second generation computers — an IBM 7044/1401 and an IBM 1620, both of them were being used for “production jobs”. IBM 1620 was used primarily to teach programming to all students of IIT and IBM 7044/1401 was used by research students and faculty besides a large number of guest users from several neighbouring universities and research laboratories. There was no interactive computer available for computer science and electrical engineering students to do hardware and software research. McCarthy was a great believer in the power of time-sharing computers. John McCarthy In fact one of his first important contributions was a memo he wrote in 1957 urging the Director of the MIT In this article we summarise the contributions of Computer Centre to modify the IBM 704 into a time- John McCarthy to Computer Science. Among his sharing machine [1]. He later persuaded Digital Equip- contributions are: suggesting that the best method ment Corporation (who made the first mini computers of using computers is in an interactive mode, a mode and the PDP series of computers) to design a mini in which computers become partners of users computer with a time-sharing operating system. enabling them to solve problems. This logically led to the idea of time-sharing of large computers by many users and computing becoming a utility — much like a power utility. -

Kansas Inventors and Innovators Fourth Grade

Kansas Inventors and Innovators Fourth Grade Developed for Kansas Historical Society at the Library of Congress, Midwest Region Workshop “It’s Elementary: Teaching with Primary Sources” 2012 Terry Healy Woodrow Wilson School, USD 383, Manhattan Overview This lesson is designed to teach students about inventors and innovators of Kansas. Students will read primary sources about Jack St. Clair Kilby, Clyde Tombaugh, George Washington Carver, and Walter P. Chrysler. Students will use a document analysis sheet to record information before developing a Kansas Innovator card. Standards History: Benchmark 1, Indicator 1 The student researches the contributions made by notable Kansans in history. Benchmark 4, Indicator 4 The student identifies and compares information from primary and secondary sources (e.g., photographs, diaries/journals, newspapers, historical maps). Common Core ELA Reading: Benchmark RI.4.9 The student integrates information from two texts on the same topic in order to write or speak about the subject knowledgably. Benchmark RI.4.10. By the end of year, read and comprehend informational texts, including history/social studies, science, and technical texts, in the grades 4–5 text complexity band proficiently, with scaffolding as needed at the high end of the range. Objectives Content The student will summarize and present information about a Kansas inventor/innovator. 1 Skills The student will analyze and summarize primary and secondary sources to draw conclusions. Essential Questions How do we know about past inventions and innovations? What might inspire or spark the creation of an invention or innovation? How do new inventions or innovations impact our lives? Resource Table Image Description Citation URL Photograph of Jack Photograph of Jack http://kshs.org/kans Kilby (Handout 1) Kilby, Kansapedia, apedia/jack-st-clair- from Texas Kansas Historical kilby/12125 Instruments Society (Topeka, Kansas) Photo originally from Texas Instruments. -

Guide to the Jack Kilby, Manuscript

Guide to the Jack Kilby, Manuscript NMAH.AC.0798 NMAH Staff Archives Center, National Museum of American History P.O. Box 37012 Suite 1100, MRC 601 Washington, D.C. 20013-7012 [email protected] http://americanhistory.si.edu/archives Table of Contents Collection Overview ........................................................................................................ 1 Administrative Information .............................................................................................. 1 Scope and Contents note................................................................................................ 2 Arrangement..................................................................................................................... 2 Biographical/Historical note.............................................................................................. 1 Names and Subjects ...................................................................................................... 2 Container Listing ...................................................................................................... Jack Kilby, Manuscript NMAH.AC.0798 Collection Overview Repository: Archives Center, National Museum of American History Title: Jack Kilby, Manuscript Identifier: NMAH.AC.0798 Date: 1951. Creator: Johnson Controls. (5757 North Green Bay Avenue, Glendale, Illinois 53209) Kilby, Jack Extent: 0.05 Cubic feet (1 folder) Language: English . Administrative Information Immediate Source of Acquisiton Collection donated by Jack Kilby and -

Matse Alumni News/Winter 2005 University of Illinois at Urbana-Champaign 1 Contents 3 Message from the Department Head

UNIVERSITY OF ILLINOIS AT URBANA-CHAMPAIGN Mat SE Department of Materials Science and Illinois Engineering WINTER 2005 ALUMNI NEWS New diffraction techniques improve sensitivity to small structures John Rogers listed in 2005 Scientific American 50 MatSE Alumni News/Winter 2005 University of Illinois at Urbana-Champaign 1 Contents 3 Message from the Department Head 4 Electron nanodiffraction techniques reveal new structures 5 Alumni awards 6 Awards banquet 6 7-8 Student awards 9 New faculty: Jianjun Cheng 10 Nestor Zaluzec honored by College 11-13 FY05 donors recognized 14 In memoriam: Earl Eckel 7 15 Where are our alumni? 16 Department notes 17 John Rogers in the 2005 Scientifi c American 50 18 Obituaries 19 Class notes 19 20 Flashback Published twice annually by the University of Illinois Department of Materials Science and Engineering for its alumni, faculty and friends. All ideas expressed in Materials Science & Engineering Alumni News are those of the authors or editor and do not necessarily refl ect the offi cial position of either the alumni or the Department of Materials Science and Engineering at the University of Illinois. On the Cover Correspondence concerning the MatSE Department Head Alumni News should be sent to: Ian Robertson The development and understanding of nanomaterials for nanotechnology rely critically on high-resolution The Editor structural characterization of individual nanostruc- MatSE Alumni News Associate Heads tures. Structure characterization tools, such as diffrac- 201B MSEB Phil Geil, Angus Rockett tion, need to be developed and adapted to nanoscale re- 1304 West Green Street quirements. The image on the cover shows single-wall Urbana, IL 61801 Assistant to the Head carbon nanotube bundles from NASA Johnson Space Jay Menacher Center. -

The Computational Attitude in Music Theory

The Computational Attitude in Music Theory Eamonn Bell Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Graduate School of Arts and Sciences COLUMBIA UNIVERSITY 2019 © 2019 Eamonn Bell All rights reserved ABSTRACT The Computational Attitude in Music Theory Eamonn Bell Music studies’s turn to computation during the twentieth century has engendered particular habits of thought about music, habits that remain in operation long after the music scholar has stepped away from the computer. The computational attitude is a way of thinking about music that is learned at the computer but can be applied away from it. It may be manifest in actual computer use, or in invocations of computationalism, a theory of mind whose influence on twentieth-century music theory is palpable. It may also be manifest in more informal discussions about music, which make liberal use of computational metaphors. In Chapter 1, I describe this attitude, the stakes for considering the computer as one of its instruments, and the kinds of historical sources and methodologies we might draw on to chart its ascendance. The remainder of this dissertation considers distinct and varied cases from the mid-twentieth century in which computers or computationalist musical ideas were used to pursue new musical objects, to quantify and classify musical scores as data, and to instantiate a generally music-structuralist mode of analysis. I present an account of the decades-long effort to prepare an exhaustive and accurate catalog of the all-interval twelve-tone series (Chapter 2). This problem was first posed in the 1920s but was not solved until 1959, when the composer Hanns Jelinek collaborated with the computer engineer Heinz Zemanek to jointly develop and run a computer program. -

Liste Der Nobelpreisträger

Physiologie Wirtschafts- Jahr Physik Chemie oder Literatur Frieden wissenschaften Medizin Wilhelm Henry Dunant Jacobus H. Emil von Sully 1901 Conrad — van ’t Hoff Behring Prudhomme Röntgen Frédéric Passy Hendrik Antoon Theodor Élie Ducommun 1902 Emil Fischer Ronald Ross — Lorentz Mommsen Pieter Zeeman Albert Gobat Henri Becquerel Svante Niels Ryberg Bjørnstjerne 1903 William Randal Cremer — Pierre Curie Arrhenius Finsen Bjørnson Marie Curie Frédéric John William William Mistral 1904 Iwan Pawlow Institut de Droit international — Strutt Ramsay José Echegaray Adolf von Henryk 1905 Philipp Lenard Robert Koch Bertha von Suttner — Baeyer Sienkiewicz Camillo Golgi Joseph John Giosuè 1906 Henri Moissan Theodore Roosevelt — Thomson Santiago Carducci Ramón y Cajal Albert A. Alphonse Rudyard \Ernesto Teodoro Moneta 1907 Eduard Buchner — Michelson Laveran Kipling Louis Renault Ilja Gabriel Ernest Rudolf Klas Pontus Arnoldson 1908 Metschnikow — Lippmann Rutherford Eucken Paul Ehrlich Fredrik Bajer Theodor Auguste Beernaert Guglielmo Wilhelm Kocher Selma 1909 — Marconi Ostwald Ferdinand Lagerlöf Paul Henri d’Estournelles de Braun Constant Johannes Albrecht Ständiges Internationales 1910 Diderik van Otto Wallach Paul Heyse — Kossel Friedensbüro der Waals Allvar Maurice Tobias Asser 1911 Wilhelm Wien Marie Curie — Gullstrand Maeterlinck Alfred Fried Victor Grignard Gerhart 1912 Gustaf Dalén Alexis Carrel Elihu Root — Paul Sabatier Hauptmann Heike Charles Rabindranath 1913 Kamerlingh Alfred Werner Henri La Fontaine — Robert Richet Tagore Onnes Theodore -

1. with Examples of Different Programming Languages Show How Programming Languages Are Organized Along the Given Rubrics: I

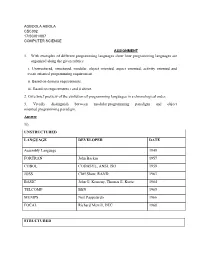

AGBOOLA ABIOLA CSC302 17/SCI01/007 COMPUTER SCIENCE ASSIGNMENT 1. With examples of different programming languages show how programming languages are organized along the given rubrics: i. Unstructured, structured, modular, object oriented, aspect oriented, activity oriented and event oriented programming requirement. ii. Based on domain requirements. iii. Based on requirements i and ii above. 2. Give brief preview of the evolution of programming languages in a chronological order. 3. Vividly distinguish between modular programming paradigm and object oriented programming paradigm. Answer 1i). UNSTRUCTURED LANGUAGE DEVELOPER DATE Assembly Language 1949 FORTRAN John Backus 1957 COBOL CODASYL, ANSI, ISO 1959 JOSS Cliff Shaw, RAND 1963 BASIC John G. Kemeny, Thomas E. Kurtz 1964 TELCOMP BBN 1965 MUMPS Neil Pappalardo 1966 FOCAL Richard Merrill, DEC 1968 STRUCTURED LANGUAGE DEVELOPER DATE ALGOL 58 Friedrich L. Bauer, and co. 1958 ALGOL 60 Backus, Bauer and co. 1960 ABC CWI 1980 Ada United States Department of Defence 1980 Accent R NIS 1980 Action! Optimized Systems Software 1983 Alef Phil Winterbottom 1992 DASL Sun Micro-systems Laboratories 1999-2003 MODULAR LANGUAGE DEVELOPER DATE ALGOL W Niklaus Wirth, Tony Hoare 1966 APL Larry Breed, Dick Lathwell and co. 1966 ALGOL 68 A. Van Wijngaarden and co. 1968 AMOS BASIC FranÇois Lionet anConstantin Stiropoulos 1990 Alice ML Saarland University 2000 Agda Ulf Norell;Catarina coquand(1.0) 2007 Arc Paul Graham, Robert Morris and co. 2008 Bosque Mark Marron 2019 OBJECT-ORIENTED LANGUAGE DEVELOPER DATE C* Thinking Machine 1987 Actor Charles Duff 1988 Aldor Thomas J. Watson Research Center 1990 Amiga E Wouter van Oortmerssen 1993 Action Script Macromedia 1998 BeanShell JCP 1999 AngelScript Andreas Jönsson 2003 Boo Rodrigo B. -

Pioneers of Computing

Pioneers of Computing В 1980 IEEE Computer Society учредило Золотую медаль (бронзовую) «Вычислительный Пионер» Пионерами учредителями стали 32 члена IEEE Computer Society, связанных с работами по информатике и вычислительным наукам. 1 Pioneers of Computing 1.Howard H. Aiken (Havard Mark I) 2.John V. Atanasoff 3.Charles Babbage (Analytical Engine) 4.John Backus 5.Gordon Bell (Digital) 6.Vannevar Bush 7.Edsger W. Dijkstra 8.John Presper Eckert 9.Douglas C. Engelbart 10.Andrei P. Ershov (theroretical programming) 11.Tommy Flowers (Colossus engineer) 12.Robert W. Floyd 13.Kurt Gödel 14.William R. Hewlett 15.Herman Hollerith 16.Grace M. Hopper 17.Tom Kilburn (Manchester) 2 Pioneers of Computing 1. Donald E. Knuth (TeX) 2. Sergei A. Lebedev 3. Augusta Ada Lovelace 4. Aleksey A.Lyapunov 5. Benoit Mandelbrot 6. John W. Mauchly 7. David Packard 8. Blaise Pascal 9. P. Georg and Edvard Scheutz (Difference Engine, Sweden) 10. C. E. Shannon (information theory) 11. George R. Stibitz 12. Alan M. Turing (Colossus and code-breaking) 13. John von Neumann 14. Maurice V. Wilkes (EDSAC) 15. J.H. Wilkinson (numerical analysis) 16. Freddie C. Williams 17. Niklaus Wirth 18. Stephen Wolfram (Mathematica) 19. Konrad Zuse 3 Pioneers of Computing - 2 Howard H. Aiken (Havard Mark I) – США Создатель первой ЭВМ – 1943 г. Gene M. Amdahl (IBM360 computer architecture, including pipelining, instruction look-ahead, and cache memory) – США (1964 г.) Идеология майнфреймов – система массовой обработки данных John W. Backus (Fortran) – первый язык высокого уровня – 1956 г. 4 Pioneers of Computing - 3 Robert S. Barton For his outstanding contributions in basing the design of computing systems on the hierarchical nature of programs and their data. -

Publications Core Magazine, 2007 Read

CA PUBLICATIONo OF THE COMPUTERre HISTORY MUSEUM ⁄⁄ SPRINg–SUMMER 2007 REMARKABLE PEOPLE R E scuE d TREAsuREs A collection saved by SAP Focus on E x TRAORdinARy i MAGEs Computers through the Robert Noyce lens of Mark Richards PUBLISHER & Ed I t o R - I n - c hie f THE BEST WAY Karen M. Tucker E X E c U t I V E E d I t o R TO SEE THE FUTURE Leonard J. Shustek M A n A GI n G E d I t o R OF COMPUTING IS Robert S. Stetson A S S o c IA t E E d I t o R TO BROWSE ITS PAST. Kirsten Tashev t E c H n I c A L E d I t o R Dag Spicer E d I t o R Laurie Putnam c o n t RIBU t o RS Leslie Berlin Chris garcia Paula Jabloner Luanne Johnson Len Shustek Dag Spicer Kirsten Tashev d E S IG n Kerry Conboy P R o d U c t I o n ma n ager Robert S. Stetson W E BSI t E M A n AGER Bob Sanguedolce W E BSI t E d ESIG n The computer. In all of human history, rarely has one invention done Dana Chrisler so much to change the world in such a short time. Ton Luong The Computer History Museum is home to the world’s largest collection computerhistory.org/core of computing artifacts and offers a variety of exhibits, programs, and © 2007 Computer History Museum.