MICRONAS TPU 3035, INTERMETALL TPU 3040 Teletext Processors

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Accessible TV Viewers Expect Broadcasters to Provide More Than Just Pictures and Sound

DOWNLOAD BEYOND THE HEADLINES Accessible TV Viewers expect broadcasters to provide more than just pictures and sound. BY PETER BLATCHFORD losed-caption subtitling The past cue the subtitle fi le with the matching and audio description are Historically, there was an occasional video fi le name on the transmission two increasingly popular requirement to add closed-caption system, and the two fi les would play service additions to mod- subtitles to selected programs, typical- out synchronically . A hardware inser- Cern TV channel output. Providing tion device would insert the subtitle ly high-profi le dramas and documen- access for people with hearing and taries. Consequently, subtitle manage- fi le in real time — typically onto line sight impairments is not the only ment developed as a manual process. A 335 using the World System Teletext driving factor. Programs subtitled videotape recording would be dubbed (WST). To ensure redundancy, there with multiple languages enable TV to produce a VHS copy, and this would would typically be two hot-swappable channels to increase their audience be delivered to the subtitle authoring inserters, possibly with an automated fi gures through wider distribution, department for fi le preparation . failover capability. For occasional which is especially useful in Eastern The completed subtitle fi le, contain- program subtitling, this system oper- ated successfully, although not entirely Channel program schedule without problems . Things have changed UK government legislation has Check existing incrementally raised the level of sub- Extract subtitle subtitle archive requirement titling required from terrestrial chan- nels. The BBC has committed itself to Collect required browse providing subtitles on all of its output Create subtitle job list media or create browse by 2008. -

ABBREVIATIONS EBU Technical Review

ABBREVIATIONS EBU Technical Review AbbreviationsLast updated: January 2012 720i 720 lines, interlaced scan ACATS Advisory Committee on Advanced Television 720p/50 High-definition progressively-scanned TV format Systems (USA) of 1280 x 720 pixels at 50 frames per second ACELP (MPEG-4) A Code-Excited Linear Prediction 1080i/25 High-definition interlaced TV format of ACK ACKnowledgement 1920 x 1080 pixels at 25 frames per second, i.e. ACLR Adjacent Channel Leakage Ratio 50 fields (half frames) every second ACM Adaptive Coding and Modulation 1080p/25 High-definition progressively-scanned TV format ACS Adjacent Channel Selectivity of 1920 x 1080 pixels at 25 frames per second ACT Association of Commercial Television in 1080p/50 High-definition progressively-scanned TV format Europe of 1920 x 1080 pixels at 50 frames per second http://www.acte.be 1080p/60 High-definition progressively-scanned TV format ACTS Advanced Communications Technologies and of 1920 x 1080 pixels at 60 frames per second Services AD Analogue-to-Digital AD Anno Domini (after the birth of Jesus of Nazareth) 21CN BT’s 21st Century Network AD Approved Document 2k COFDM transmission mode with around 2000 AD Audio Description carriers ADC Analogue-to-Digital Converter 3DTV 3-Dimension Television ADIP ADress In Pre-groove 3G 3rd Generation mobile communications ADM (ATM) Add/Drop Multiplexer 4G 4th Generation mobile communications ADPCM Adaptive Differential Pulse Code Modulation 3GPP 3rd Generation Partnership Project ADR Automatic Dialogue Replacement 3GPP2 3rd Generation Partnership -

ATVOD Working Group on Access Services (WGAS)

1 ATVOD Working Group on Access Services (WGAS) Report prepared by Nick Tanton Introduction The perceived ease with which viewers can now get access services with linear TV in the UK 1 makes it hard for users/customers to understand why on-demand services generally lag behind in accessibility. The end-to-end chain (content acquisition, versioning, scheduling, delivery and presentation) for on-demand generally differs substantially from that of linear TV. Some processes are (or could be) the same or similar whilst others are not; some also may apply to one on-demand service provider but not to another. In particular the species (and sometimes generational variants) of end-user equipment are diverse and some may not have been designed a priori with accessibility in mind. For on-demand content there are no insuperable barriers to providing subtitles for Hard-of-Hearing people or Audio Description for Blind and Partially Sighted users. However there are various practical technical and commercial challenges which a regulator or service provider may need to recognise and to address if these access services are to be made available in a realisable and usable form to the end-user. For any particular service provider, the mix and impact of these challenges depends on the delivery platform(s) on which they have a presence, their role within a particular delivery chain and their business model. The content of this report represents a distillation of understanding from within the ATVOD Working Group on Access Services (WGAS) and input from individual companies who have participated in those discussions. -

Saa5x9x Family Economy Teletext and TV Microcontrollers

INTEGRATED CIRCUITS DATA SHEET SAA5x9x family Economy teletext and TV microcontrollers Preliminary specification 1997 Jul 07 File under Integrated Circuits, IC02 Philips Semiconductors Preliminary specification Economy teletext and TV microcontrollers SAA5x9x family CONTENTS 9.7 Language group identification 9.8 525-line operation 1 FEATURES 9.9 On Screen Display characters 1.1 General 9.10 Control characters 1.2 Microcontroller 9.11 Quadruple width display (SAA549x) 1.3 Teletext acquisition 9.12 Page attributes 1.4 Teletext Display 9.13 Display modes 1.5 Additional features of SAA529xA devices 9.14 On Screen Display boxes 1.6 Additional features of SAA549x devices 9.15 Screen colour 9.16 Redefinable Colours (SAA549x) 2 GENERAL DESCRIPTION 9.17 Cursor 3 ORDERING INFORMATION 9.18 Other display features 4 QUICK REFERENCE DATA 9.19 Display timing 5 BLOCK DIAGRAM 9.20 Horizontal timing 9.21 Vertical timing 6 PINNING INFORMATION 9.22 Display position 6.1 Pinning 9.23 Clock generator 6.2 Pin description 10 CHARACTER SETS 7 FUNCTIONAL DESCRIPTION 10.1 Pan-European 7.1 Microcontroller 10.2 Russian 7.2 80C51 Features not supported 10.3 Greek/Turkish 7.3 Additional features 10.4 Arabic/English/French 7.4 Microcontroller interfacing 10.5 Thai 8 TELETEXT DECODER 10.6 Arabic/Hebrew 8.1 Data slicer 11 LIMITING VALUES 8.2 Acquisition timing 12 CHARACTERISTICS 8.3 Teletext acquisition 13 CHARACTERISTICS FOR THE I2C-BUS 8.4 Rolling headers and time INTERFACE 8.5 Error checking 8.6 Memory organisation of SAA5296/7, 14 QUALITY SPECIFICATIONS SAA5296/7A and -

TT1222 4:2:0 Professional Receiver

ST.RE.TT1222.2 Issue 2 ENGLISH (UK) REFERENCE GUIDE TT1222 4:2:0 Professional Receiver Software Version 2.0.0 (and later) TT1222 4:2:0 Professional Receiver Preliminary Pages ENGLISH (UK) ITALIANO READ THIS FIRST! LEGGERE QUESTO AVVISO PER PRIMO! If you do not understand the contents of this manual Se non si capisce il contenuto del presente manuale DO NOT OPERATE THIS EQUIPMENT. NON UTILIZZARE L’APPARECCHIATURA. Also, translation into any EC official language of this manual can be È anche disponibile la versione italiana di questo manuale, ma il costo è made available, at your cost. a carico dell’utente. SVENSKA NEDERLANDS LÄS DETTA FÖRST! LEES DIT EERST! Om Ni inte förstår informationen i denna handbok Als u de inhoud van deze handleiding niet begrijpt ARBETA DÅ INTE MED DENNA UTRUSTNING. STEL DEZE APPARATUUR DAN NIET IN WERKING. En översättning till detta språk av denna handbok kan också anskaffas, U kunt tevens, op eigen kosten, een vertaling van deze handleiding på Er bekostnad. krijgen. PORTUGUÊS SUOMI LEIA O TEXTO ABAIXO ANTES DE MAIS NADA! LUE ENNEN KÄYTTÖÄ! Se não compreende o texto deste manual Jos et ymmärrä käsikirjan sisältöä NÃO UTILIZE O EQUIPAMENTO. ÄLÄ KÄYTÄ LAITETTA. O utilizador poderá também obter uma tradução do manual para o Käsikirja voidaan myös suomentaa asiakkaan kustannuksella. português à própria custa. FRANÇAIS DANSK AVANT TOUT, LISEZ CE QUI SUIT! LÆS DETTE FØRST! Si vous ne comprenez pas les instructions contenues dans ce manuel Udstyret må ikke betjenes NE FAITES PAS FONCTIONNER CET APPAREIL. MEDMINDRE DE TIL FULDE FORSTÅR INDHOLDET AF DENNE HÅNDBOG. -

MAPPING DIGITAL MEDIA: NETHERLANDS Mapping Digital Media: Netherlands

COUNTRY REPORT MAPPING DIGITAL MEDIA: NETHERLANDS Mapping Digital Media: Netherlands A REPORT BY THE OPEN SOCIETY FOUNDATIONS WRITTEN BY Martijn de Waal (lead reporter) Andra Leurdijk, Levien Nordeman, Thomas Poell (reporters) EDITED BY Marius Dragomir and Mark Thompson (Open Society Media Program editors) EDITORIAL COMMISSION Yuen-Ying Chan, Christian S. Nissen, Dusˇan Reljic´, Russell Southwood, Michael Starks, Damian Tambini The Editorial Commission is an advisory body. Its members are not responsible for the information or assessments contained in the Mapping Digital Media texts OPEN SOCIETY MEDIA PROGRAM TEAM Meijinder Kaur, program assistant; Morris Lipson, senior legal advisor; and Gordana Jankovic, director OPEN SOCIETY INFORMATION PROGRAM TEAM Vera Franz, senior program manager; Darius Cuplinskas, director 12 October 2011 Contents Mapping Digital Media ..................................................................................................................... 4 Executive Summary ........................................................................................................................... 6 Context ............................................................................................................................................. 10 Social Indicators ................................................................................................................................ 12 Economic Indicators ........................................................................................................................ -

Abkürzungs-Liste ABKLEX

Abkürzungs-Liste ABKLEX (Informatik, Telekommunikation) W. Alex 1. Juli 2021 Karlsruhe Copyright W. Alex, Karlsruhe, 1994 – 2018. Die Liste darf unentgeltlich benutzt und weitergegeben werden. The list may be used or copied free of any charge. Original Point of Distribution: http://www.abklex.de/abklex/ An authorized Czechian version is published on: http://www.sochorek.cz/archiv/slovniky/abklex.htm Author’s Email address: [email protected] 2 Kapitel 1 Abkürzungen Gehen wir von 30 Zeichen aus, aus denen Abkürzungen gebildet werden, und nehmen wir eine größte Länge von 5 Zeichen an, so lassen sich 25.137.930 verschiedene Abkür- zungen bilden (Kombinationen mit Wiederholung und Berücksichtigung der Reihenfol- ge). Es folgt eine Auswahl von rund 16000 Abkürzungen aus den Bereichen Informatik und Telekommunikation. Die Abkürzungen werden hier durchgehend groß geschrieben, Akzente, Bindestriche und dergleichen wurden weggelassen. Einige Abkürzungen sind geschützte Namen; diese sind nicht gekennzeichnet. Die Liste beschreibt nur den Ge- brauch, sie legt nicht eine Definition fest. 100GE 100 GBit/s Ethernet 16CIF 16 times Common Intermediate Format (Picture Format) 16QAM 16-state Quadrature Amplitude Modulation 1GFC 1 Gigabaud Fiber Channel (2, 4, 8, 10, 20GFC) 1GL 1st Generation Language (Maschinencode) 1TBS One True Brace Style (C) 1TR6 (ISDN-Protokoll D-Kanal, national) 247 24/7: 24 hours per day, 7 days per week 2D 2-dimensional 2FA Zwei-Faktor-Authentifizierung 2GL 2nd Generation Language (Assembler) 2L8 Too Late (Slang) 2MS Strukturierte -

Videotext Technik in Vergangenheit, Gegenwart Und Zukunft

Videotext Technik in Vergangenheit, Gegenwart und Zukunft Sibylle Weber-Böttler & Patrick Cernko 25.11.99 Dieses Referat ist online verfügbar unter http://www.bigfoot.com/˜errror. 1 Inhaltsverzeichnis 1 Einführung 3 2 Technische Merkmale von Fernsehtext 4 2.1 Wie funktioniert Übertragung ? . 4 2.2 Technische Weiterentwicklung in Großbritannien . 5 2.3 Technische Entwicklung in Deutschland . 5 2.4 Die fünf Enhancement-Level . 6 2.5 Struktur des Fernsehtextes . 8 2.5.1 Der Zyklus des Videotextes . 8 2.6 VPS/VPT . 10 2.7 TOP-Text . 11 3 Push-Technologien 13 3.1 Elektronische Programmführer . 13 3.1.1 EPG . 13 3.1.2 NexTView . 14 3.2 Internet im Videotext . 15 3.2.1 TV-Online . 15 3.2.2 Intercast . 16 3.2.3 Zusammenfassung . 17 4 Verfahren mit Rückkanal 18 4.1 TeleWeb . 18 4.2 WebTV . 21 4.3 ATVEF . 22 4.4 Enhanced TV . 22 4.5 Zusammenfassung der Vorteile . 23 5 Teletext im Internet 24 5.1 ARD/ZDF . 24 5.2 Online TV bei TVToday . 24 6 Fazit 28 A Glossar 29 2 1 Einführung Seit Beginn des ARD/ZDF-Feldversuches 1980 in Deutschland hat sich Fernseh- text in Deutschland etabliert. Die 80er und 90er Jahre waren geprägt von einem regelrechten Gründungsboom neuer Fernsehtextdienste. Experten gingen 1997 von 22 Millionen Fernsehtext-Haushalten in Deutsch- land aus [Kul]. Da die Preise für Fernseher mit Fernsehtext-Decodern heute teil- weise schon unter 300 DM liegen, ist davon auszugehen, dass die Zahl der Haus- halte mit Fernsehtext-Geräten weiter steigen wird. Mit Fernsehtext begann eine Entwicklung, die bis heute anhält: Traditionelle Medien werden individueller nutzbar. -

United States Patent (19) 11) Patent Number: 4,908,707 Kinghorn 45) Date of Patent: Mar

United States Patent (19) 11) Patent Number: 4,908,707 Kinghorn 45) Date of Patent: Mar. 13, 1990 54 VIDEO CASSETTE RECORDER PROGRAMMING VA TELETEXT FOREIGN PATENT DOCUMENTS TRANSMISSIONS 0179001 4/1986 European Pat. Off. 0191149 8/1986 European Pat. Off... 75) Inventor: John R. Kinghorn, Ashtead, Great OTHER PUBLICATIONS Britain BBC et al., "Broadcast Teletext Specification", (Sep. 73) Assignee: U.S. Philips Corp., New York, N.Y. 1976). Primary Examiner-John W. Shepperd 21 Appl. No.: 221,156 Assistant Examiner-Michael D. Parker Attorney, Agent, or Firm-Thomas A. Briody 22 Filed: Jul. 19, 1988 57 ABSTRACT 30 Foreign Application Priority Data A system for video recorder programming using exist ing television broadcast teletext transmissions. The pro Jul. 20, 1987 GB) United Kingdom ................. 8717132 grams required are chosen from schedules displayed on Aug. 5, 1987 GB) United Kingdom ................. 8718557 teletext pages, the necessary control information is loaded automatically into a video recorder, and pro I51 Int. Cl“............................................. H04N 7/087 gram labels are transmitted to ensure that the correct 52 U.S.C. .................................... 358/147; 358/142; programs will be recorded even if program timings are 358/191.1; 358/1941; 360/27; 360/33.1 altered. All the control information for achieving the 58) Field of Search ................... 358/84, 86, 142, 146, above are fitted into the coding structure of a teletext 358/147, 194.1, 191.1, 310,311, 335, 337; transmission using extension packets additional to data 360/13, 14.1, 27, 33.1, 40, 48, 53, 55, 61, 69 packets containg display data. The invention also ex tends to a video recorder with its own teletext decoder (56. -

Service Manual Colour Television

S/M No. : TWP895BEF0R2 Service Manual Colour Television CHASSIS WP-895 CP-485F DAEWOO ELECTRONICS CO., LTD http : //svc.dwe.co.kr Jun. 2002 Service manual WP-895/895F. CP485F Contents 1 - Main features ........................................................................................................................................................ 4 1-1 Specifications .................................................................................................................................................. 4 1-2 Channel table .................................................................................................................................................. 8 1-3 ATSS sorting method ....................................................................................................................................... 11 2 - Safety instruction ................................................................................................................................................. 13 3 - Alignment instructions ........................................................................................................................................ 14 3-1 Microcontroller configuration : Service mode ................................................................................................... 14 3-2 Service mode navigation ................................................................................................................................. 14 3-3 Microcontroller configuration : Option ............................................................................................................. -

TONY CONRAD: VIDEO VIDEO –UNDDARÜBER HINAUS CONRAD TONY TABEA LURK PETER LANG Blick Auf Die Künstlervita Die Auf Blick E Musik Der Kunst Basel

TONY CONRAD VIDEO – UND DARÜBER HINAUS Der US-amerikanische Künstler Anthony (Tony) Conrad (*1940) ist seit über 50 Jahren eine feste Größe im Kunstbetrieb. Gefeiert als TABEA LURK Musiker, Filmemacher, Video- und Performance-Künstler gelingt sein Durchbruch 1966 mit dem Experimentalfi lm “The Flicker”. Neben den Filmarbeiten (inkl. “Yellow Movies”) fi nden die soge- nannten “String Performances” (Solovionline) große Anerkennung. Sie erinnern an das Theatre of Eternal Music (1962–1967) und wurden von namhaften Autoren aufgearbeitet. Die vorliegende Monografi e konzentriert sich daher auf die ca. 70 Videoarbeiten des Künstlers, die ab 1977 entstanden und noch nicht wissenschaftlich untersucht wurden. Auf die Erinnerung an Eckpunkte des künstlerischen Werdegangs (Videografi scher Blick auf die Künstlervita) folgt der Übergang vom materialis- tischen Experimentalfi lm zum videografi schen Bilddenken im Um- feld der Appropriation Art (Video als letzte Aufforderung). Die Refl exion der telematischen Kultur der 1980er Jahre hinterfragt das Wechselspiel zwischen (Video-)Kunst und Gesellschaft (Video TONY CONRAD: VIDEO als Fernsehkritik). Das letzte Kapitel (Video im Spannungsfeld der Musik) kehrt zum Beginn der künstlerischen Karriere Tony Conrads zurück. Die Kunstwissenschaftlerin Tabea Lurk hat nach ihrem Volontariat am ZKM | Zentrum für Kunst und Medientechnologie Karlsruhe von 2006– LURK TABEA 2015 primär an der Hochschule der Künste Bern geforscht und gelehrt. Seit 2015 leitet sie die Mediathek der Hochschule für Gestaltung und Kunst Basel. ISBN 978-3-0343-2037-5 WWW.PETERLANG.COM PETER LANG TONY CONRAD VIDEO – UND DARÜBER HINAUS Der US-amerikanische Künstler Anthony (Tony) Conrad (*1940) ist seit über 50 Jahren eine feste Größe im Kunstbetrieb. Gefeiert als TABEA LURK Musiker, Filmemacher, Video- und Performance-Künstler gelingt sein Durchbruch 1966 mit dem Experimentalfi lm “The Flicker”. -

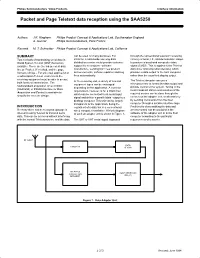

Packet and Page Teletext Data Reception Using the SAA5250

Philips Semiconductors Video Products Interface information Packet and Page Teletext data reception using the SAA5250 Authors: J.R. Kinghorn Philips Product Concept & Applications Lab, Southampton England A. Guenot Philips Semiconductors, Paris France Revised: M. T. Schneider Philips Product Concept & Applications Lab, California SUMMARY can be used for many purposes. For through the conventional television receiving Two methods of transmitting serial data in instance, a nationwide one way data circuitry of tuner, I.F., and demodulator stages World System Teletext (WST) format are distribution service could provide customer to produce a baseband composite video available. These are the independent data support for a computer software signal (CVBS). This is applied to the Teletext line or ‘Packet 31’ method, and the page manufacture, sending both new product data slicer and acquisition decoder, which format technique. For universal application in announcements, software updates and bug provides a data output to the host computer a subscription Teletext environment the fixes automatically. rather than the usual text display output. receiving equipment must be able to accept At the receiving end, a variety of terminal The Teletext decoder can use a both forms of transmission. The equipment types can be envisaged microprocessor to format the data output and Multistandard acquisition circuit CIDAC depending on the application. A common provide control of the system. Tuning in the (SAA5250) or CMOS Interface for Data requirement, however, is for a ‘black box’ local broadcast station and selection of the Acquisition and Control, is available to which can be connected to an aerial input required service can be done through the simplify the receiver design.