Packet and Page Teletext Data Reception Using the SAA5250

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

Accessible TV Viewers Expect Broadcasters to Provide More Than Just Pictures and Sound

DOWNLOAD BEYOND THE HEADLINES Accessible TV Viewers expect broadcasters to provide more than just pictures and sound. BY PETER BLATCHFORD losed-caption subtitling The past cue the subtitle fi le with the matching and audio description are Historically, there was an occasional video fi le name on the transmission two increasingly popular requirement to add closed-caption system, and the two fi les would play service additions to mod- subtitles to selected programs, typical- out synchronically . A hardware inser- Cern TV channel output. Providing tion device would insert the subtitle ly high-profi le dramas and documen- access for people with hearing and taries. Consequently, subtitle manage- fi le in real time — typically onto line sight impairments is not the only ment developed as a manual process. A 335 using the World System Teletext driving factor. Programs subtitled videotape recording would be dubbed (WST). To ensure redundancy, there with multiple languages enable TV to produce a VHS copy, and this would would typically be two hot-swappable channels to increase their audience be delivered to the subtitle authoring inserters, possibly with an automated fi gures through wider distribution, department for fi le preparation . failover capability. For occasional which is especially useful in Eastern The completed subtitle fi le, contain- program subtitling, this system oper- ated successfully, although not entirely Channel program schedule without problems . Things have changed UK government legislation has Check existing incrementally raised the level of sub- Extract subtitle subtitle archive requirement titling required from terrestrial chan- nels. The BBC has committed itself to Collect required browse providing subtitles on all of its output Create subtitle job list media or create browse by 2008. -

KSL-TV--First in the US with Teletext

DOCUMENT RESUME , ED 229 808 CS 504 188 AUTHOR Acker, Stephen R.; Larson, TimothyL. TITLE KSL-TV--First in fir U.S. with Te1etext. , PUB DATE Nov 82 , NOTE 19p.; Paper presented at the AnnualMeeting/ . of the . Speech Communication Association (68th,'Louipille, A KY, November 4=7, t9821t. PUB TYPE Rep9rts - Evaluative/Feasibility (142) Speeches/Conference Papers (150) EDRS PRICE MF01/PC01 Plus Postage. DESCRIPTOkS *Information Services; *Telephone Coimiunications/ Systems; *Television; Video Equipme; ;,*Videotex IDENTIFIERS *Station Kgr.. TV UT; *Two Way Televi ion ABSTRACT Under an experimental license issu din 1978, KSL-TV in Salt Lake City, Utah, provided 126pages of tel text information to its viewers. In choosing thissystem, the stati n had to decide between it and a videotext system. Althoughvideotext systems permit two-way communication, usuallyover telephone UT, teletext broadcast technology is much cheaper.The Cost fo a decoder, a critical factor in the consumer's'accoptance of e ther system, is ,expected to decline for both technologies.In tel text, access cost is zero, while in videotext theinformation provi er has the option of charging users. It'is possiblethat videotext' interactive capability and superior graphics willincrease rt penetration into paying households. Although teletextand videotext provide similar mass market services, videotext has substantiallymore flexibility and speed. Since systems currently beingused in different countries are incompatible, establishing,technical standards inthe areas of data format, transmission,a d display is of key importance. Current trends and the growing home co1iptermarket favor the growth of videotext, but KSL-TV's experiment howed the value of teletextas an interim information system. -

Instructions Wide Lcd Panel Tv Lt-42Dr9bj

LT-42DR9BJ_Analog.book Page 0 Tuesday, February 19, 2008 2:53 PM INSTRUCTIONS WIDE LCD PANEL TV LT-42DR9BJ Trade Mark of the DVB Digital Video Broadcasting Project (1991 to 1996) Number : 5227 GGT0205-001A-U LT-42DR9BJ_Analog.book Page 0 Tuesday, February 19, 2008 2:53 PM LT-42DR9BJ_Analog.book Page 1 Tuesday, February 19, 2008 2:53 PM nf A separate manual “WATCHING Information for Users on Disposal of Old ENGLISH DIGITAL CHANNELS” is provided. Equipment [European Union] This symbol indicates that the electrical and electronic equipment IMPORTANT should not be disposed as general household waste at its end-of- life. Instead, the product should be handed over to the applicable Please refer to the separate manual collection point for the recycling of electrical and electronic WATCHING DIGITAL CHANNELS equipment for proper treatment, recovery and recycling in Contents when watching digital channels. Before reading this manual Read the separate user manual (INSTRUCTIONS), “Warning” (P. 2), and understand how to use th e TV safely. After that follow the Watching digital channels...........................................................2 accordance with your national legislation. PREPARE instructions in “Getting started” (P. 8) to connect the aerial and other Display the programme information ....................................................4 external devices to the TV, and configure the settings for the TV. View subtitles ......................................................................................4 USE Select audio language ........................................................................5 This manual only provides information on View teletext information.....................................................................5 watching digital channels. Other information is Using EPG (Electronic Programme Guide) ................................6 explained in the “INSTRUCTIONS”. Please read both this manual and the “INSTRUCTIONS” By disposing of this product correctly, you will help to conserve manual. -

DO~Ffiloading and ADDRESSING VIA TELETEXT Gary W. Stanton

DO~ffiLOADING AND ADDRESSING VIA TELETEXT Gary w. Stanton Southern Satellite Systems ABSTRACT A teletext signal has been continuously typewriters, or not a large enough transmitted on the vertical interval supply of "t's" at their printer? These of Satcom I, transponder 6 since the questions aside, let's deal with what's NCTA show in 1980. The original purpose really happening. was the video dissemination of cable news services. Recently, the system There are some cable systems in the has been modified to incorporate data u.s. delivering "videotext," which for transmission which emulates a standard the purposes of this paper will be telephone line, but with far higher considered two-way and interactive. data reliability. In addition, the There are some broadcast stations test modified teletext system for data marketing their "teletext" services, transmission incorporates an which in this article will mean strictly addressability function with over five one-way. UPI, Reuters, Dow Jones, and million addresses possible. A priority Quotrader are all delivering their scheme for national, regional, local services, which are "teletext", to and individual addressing is described. cable systems, today and in the case A description of the system, including of Quotrader, to private users. UP! data from reliability tests is presented. and Reuters began satellite testing This will also define several key of the service in July 1980, and service technical requirements for successful to cable TV headends in October 1980. teletext data reception. But one-way teletext services aren't really what all the excitement is about. It's the interactive services that are General Information getting all the attention, and precipitating the hue and cry of the The cable and communications trades future of communications. -

TVP5150AM1 VBI Quick Start

Application Report SLEA102–July 2010 TVP5150AM1 VBI Quick Start ..................................................................................................................................................... ABSTRACT The TVP5150AM1 video decoder has an internal vertical data processor (VDP) that can be used to slice various VBI data services such as V-Chip, Teletext (WST, NABTS), closed captioning (CC), wide screen signaling (WSS), copy generation management system (CGMS), video program system (VPS), electronic program guide (EPG or Gemstar), program delivery control (PDC) and vertical interval time code (VITC). This application report provides an introduction to the VBI data slicing capabilities of the TVP5150AM1 and focuses on configuring the TVP5150AM1 for the more commonly used VBI data services. Contents 1 Introduction .................................................................................................................. 2 2 VDP Configuration RAM ................................................................................................... 4 3 Line Mode Registers ........................................................................................................ 6 4 Sliced Data Retrieval ....................................................................................................... 7 5 Managing Data Retrieval ................................................................................................... 7 6 FIFO Access ................................................................................................................ -

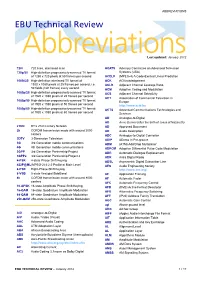

ABBREVIATIONS EBU Technical Review

ABBREVIATIONS EBU Technical Review AbbreviationsLast updated: January 2012 720i 720 lines, interlaced scan ACATS Advisory Committee on Advanced Television 720p/50 High-definition progressively-scanned TV format Systems (USA) of 1280 x 720 pixels at 50 frames per second ACELP (MPEG-4) A Code-Excited Linear Prediction 1080i/25 High-definition interlaced TV format of ACK ACKnowledgement 1920 x 1080 pixels at 25 frames per second, i.e. ACLR Adjacent Channel Leakage Ratio 50 fields (half frames) every second ACM Adaptive Coding and Modulation 1080p/25 High-definition progressively-scanned TV format ACS Adjacent Channel Selectivity of 1920 x 1080 pixels at 25 frames per second ACT Association of Commercial Television in 1080p/50 High-definition progressively-scanned TV format Europe of 1920 x 1080 pixels at 50 frames per second http://www.acte.be 1080p/60 High-definition progressively-scanned TV format ACTS Advanced Communications Technologies and of 1920 x 1080 pixels at 60 frames per second Services AD Analogue-to-Digital AD Anno Domini (after the birth of Jesus of Nazareth) 21CN BT’s 21st Century Network AD Approved Document 2k COFDM transmission mode with around 2000 AD Audio Description carriers ADC Analogue-to-Digital Converter 3DTV 3-Dimension Television ADIP ADress In Pre-groove 3G 3rd Generation mobile communications ADM (ATM) Add/Drop Multiplexer 4G 4th Generation mobile communications ADPCM Adaptive Differential Pulse Code Modulation 3GPP 3rd Generation Partnership Project ADR Automatic Dialogue Replacement 3GPP2 3rd Generation Partnership -

ATVOD Working Group on Access Services (WGAS)

1 ATVOD Working Group on Access Services (WGAS) Report prepared by Nick Tanton Introduction The perceived ease with which viewers can now get access services with linear TV in the UK 1 makes it hard for users/customers to understand why on-demand services generally lag behind in accessibility. The end-to-end chain (content acquisition, versioning, scheduling, delivery and presentation) for on-demand generally differs substantially from that of linear TV. Some processes are (or could be) the same or similar whilst others are not; some also may apply to one on-demand service provider but not to another. In particular the species (and sometimes generational variants) of end-user equipment are diverse and some may not have been designed a priori with accessibility in mind. For on-demand content there are no insuperable barriers to providing subtitles for Hard-of-Hearing people or Audio Description for Blind and Partially Sighted users. However there are various practical technical and commercial challenges which a regulator or service provider may need to recognise and to address if these access services are to be made available in a realisable and usable form to the end-user. For any particular service provider, the mix and impact of these challenges depends on the delivery platform(s) on which they have a presence, their role within a particular delivery chain and their business model. The content of this report represents a distillation of understanding from within the ATVOD Working Group on Access Services (WGAS) and input from individual companies who have participated in those discussions. -

DVB); Specification for Conveying ITU-R System B Teletext in DVB Bitstreams

ETSI EN 300 472 V1.4.1 (2017-04) EUROPEAN STANDARD Digital Video Broadcasting (DVB); Specification for conveying ITU-R System B Teletext in DVB bitstreams 2 ETSI EN 300 472 V1.4.1 (2017-04) Reference REN/JTC-DVB-365 Keywords broadcasting, digital, DVB, MPEG, teletext, TV, video ETSI 650 Route des Lucioles F-06921 Sophia Antipolis Cedex - FRANCE Tel.: +33 4 92 94 42 00 Fax: +33 4 93 65 47 16 Siret N° 348 623 562 00017 - NAF 742 C Association à but non lucratif enregistrée à la Sous-Préfecture de Grasse (06) N° 7803/88 Important notice The present document can be downloaded from: http://www.etsi.org/standards-search The present document may be made available in electronic versions and/or in print. The content of any electronic and/or print versions of the present document shall not be modified without the prior written authorization of ETSI. In case of any existing or perceived difference in contents between such versions and/or in print, the only prevailing document is the print of the Portable Document Format (PDF) version kept on a specific network drive within ETSI Secretariat. Users of the present document should be aware that the document may be subject to revision or change of status. Information on the current status of this and other ETSI documents is available at https://portal.etsi.org/TB/ETSIDeliverableStatus.aspx If you find errors in the present document, please send your comment to one of the following services: https://portal.etsi.org/People/CommiteeSupportStaff.aspx Copyright Notification No part may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm except as authorized by written permission of ETSI. -

VIDEOTEX ALTERNATIVES in CABLE Walter S. Ciciora William L

VIDEOTEX ALTERNATIVES IN CABLE Walter s. Ciciora William L. Thomas AMERICAN TELEVISION & COMMUNICATIONS CORPORATION ZENITH RADIO CORPORATION Introduction without increasing bandwidth. VBI teletext services are available on any The first videotex alternative systems that carry WTBS, NBC or CBS. determines whether the transmission is Both NBC and CBS are currently broad broadcast, telephone, or cable. The casting teletext according to the North concentration here is on cable. The American Broadcast Teletext Specifi reasons for this will be discussed in cation (NABTS). WTBS carries the Keyfax detail since they are fundamental to signal which follows the British understanding cable's substantial advan approach. Unfortunately, two different tages over competing media. In cable decoders would be required to receive there are a wide variety of alternatives all three signals. Full field teletext to consider. Should the videotex ser requires the dedication of a complete vice be vertical blanking interval or video channel to the teletext service. full field? Will financial support come In return for this commitment, full from advertising or from pay, or both? field teletext offers tremendous page If a pay structure is chosen will the capacity. Typical systems can carry 500 security be soft, firm or hard? Will or more pages per second. This is in the service be tiered and addressable or contrast to the 4 or 5 pages per second simply go no-go? Will it be one-way, possible in a VBI service. Thus, for a one-way upgradable, or two-way? Will given 10-second maximum wait time, full the display be RF or RGB? Are mosaic field teletext has a capacity of 5,000 graphics adequate, or must geometric pages. -

Saa5x9x Family Economy Teletext and TV Microcontrollers

INTEGRATED CIRCUITS DATA SHEET SAA5x9x family Economy teletext and TV microcontrollers Preliminary specification 1997 Jul 07 File under Integrated Circuits, IC02 Philips Semiconductors Preliminary specification Economy teletext and TV microcontrollers SAA5x9x family CONTENTS 9.7 Language group identification 9.8 525-line operation 1 FEATURES 9.9 On Screen Display characters 1.1 General 9.10 Control characters 1.2 Microcontroller 9.11 Quadruple width display (SAA549x) 1.3 Teletext acquisition 9.12 Page attributes 1.4 Teletext Display 9.13 Display modes 1.5 Additional features of SAA529xA devices 9.14 On Screen Display boxes 1.6 Additional features of SAA549x devices 9.15 Screen colour 9.16 Redefinable Colours (SAA549x) 2 GENERAL DESCRIPTION 9.17 Cursor 3 ORDERING INFORMATION 9.18 Other display features 4 QUICK REFERENCE DATA 9.19 Display timing 5 BLOCK DIAGRAM 9.20 Horizontal timing 9.21 Vertical timing 6 PINNING INFORMATION 9.22 Display position 6.1 Pinning 9.23 Clock generator 6.2 Pin description 10 CHARACTER SETS 7 FUNCTIONAL DESCRIPTION 10.1 Pan-European 7.1 Microcontroller 10.2 Russian 7.2 80C51 Features not supported 10.3 Greek/Turkish 7.3 Additional features 10.4 Arabic/English/French 7.4 Microcontroller interfacing 10.5 Thai 8 TELETEXT DECODER 10.6 Arabic/Hebrew 8.1 Data slicer 11 LIMITING VALUES 8.2 Acquisition timing 12 CHARACTERISTICS 8.3 Teletext acquisition 13 CHARACTERISTICS FOR THE I2C-BUS 8.4 Rolling headers and time INTERFACE 8.5 Error checking 8.6 Memory organisation of SAA5296/7, 14 QUALITY SPECIFICATIONS SAA5296/7A and -

Data Services in Digital Television Broadcasting

Recommendation ITU-R BT.1301-1 (03/2011) Data services in digital television broadcasting BT Series Broadcasting service (television) ii Rec. ITU-R BT.1301-1 Foreword The role of the Radiocommunication Sector is to ensure the rational, equitable, efficient and economical use of the radio-frequency spectrum by all radiocommunication services, including satellite services, and carry out studies without limit of frequency range on the basis of which Recommendations are adopted. The regulatory and policy functions of the Radiocommunication Sector are performed by World and Regional Radiocommunication Conferences and Radiocommunication Assemblies supported by Study Groups. Policy on Intellectual Property Right (IPR) ITU-R policy on IPR is described in the Common Patent Policy for ITU-T/ITU-R/ISO/IEC referenced in Annex 1 of Resolution ITU-R 1. Forms to be used for the submission of patent statements and licensing declarations by patent holders are available from http://www.itu.int/ITU-R/go/patents/en where the Guidelines for Implementation of the Common Patent Policy for ITU-T/ITU-R/ISO/IEC and the ITU-R patent information database can also be found. Series of ITU-R Recommendations (Also available online at http://www.itu.int/publ/R-REC/en) Series Title BO Satellite delivery BR Recording for production, archival and play-out; film for television BS Broadcasting service (sound) BT Broadcasting service (television) F Fixed service M Mobile, radiodetermination, amateur and related satellite services P Radiowave propagation RA Radio astronomy RS Remote sensing systems S Fixed-satellite service SA Space applications and meteorology SF Frequency sharing and coordination between fixed-satellite and fixed service systems SM Spectrum management SNG Satellite news gathering TF Time signals and frequency standards emissions V Vocabulary and related subjects Note: This ITU-R Recommendation was approved in English under the procedure detailed in Resolution ITU-R 1. -

The New Video Marketplace and the Search for a Coherent Regulatory Philosophy

Catholic University Law Review Volume 32 Issue 3 Spring 1983 Article 5 1983 The New Video Marketplace and the Search for a Coherent Regulatory Philosophy Jill Abeshouse Stern Erwin G. Krasnow R. Michael Senkowski Follow this and additional works at: https://scholarship.law.edu/lawreview Recommended Citation Jill A. Stern, Erwin G. Krasnow & R. Michael Senkowski, The New Video Marketplace and the Search for a Coherent Regulatory Philosophy, 32 Cath. U. L. Rev. 529 (1983). Available at: https://scholarship.law.edu/lawreview/vol32/iss3/5 This Article is brought to you for free and open access by CUA Law Scholarship Repository. It has been accepted for inclusion in Catholic University Law Review by an authorized editor of CUA Law Scholarship Repository. For more information, please contact [email protected]. THE NEW VIDEO MARKETPLACE AND THE SEARCH FOR A COHERENT REGULATORY PHILOSOPHY JillAbeshouse Stern * Erwin G. Krasnow** A Michael Senkowski*** TABLE OF CONTENTS I. INNOVATIONS IN VIDEO SERVICES ............................ 532 A. New Over-the-Air Video Services to the Home ............ 532 I. Subscription Television (STV) ........................ 532 2. Teletext ............................................. 535 3. Low Power Television (LPTF) ....................... 538 4. Direct Broadcast Satellites (DBS) .................... 541 -5. Satellite Master Antenna Television (SMA TV ........ 543 6. Multipoint Distribution Service (MDS) ................ 544 7 Private Operational-FixedMicrowave Service (OFS) .. 549 B. New Closed Transmission Video Services to the Home .... 550 L Cable Television and Interactive Cable Television ..... 550 2. Cable Interconnect Systems .......................... 553 3. Common Carrier Wireline or Fiber Optic Services .... 554 4. Electronic Publishing Services ........................ 555 C. Recorded Video Servicesfor Home Use .................. 557 1. Videocassette Recorders and Videodisc Players .......