Device-Level Predictive Modeling of Extreme Electromagnetic Interference

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

3 Carbon Nanotubes – the Dispersion

DEPARTMENT OF PHYSICS UNIVERSITY OF JYVÄSKYLÄ RESEARCH REPORT No. 11/2018 DEVELOPMENT OF MICROFLUIDICS FOR SORTING OF CARBON NANOTUBES BY JÁN BOROVSKÝ Academic Dissertation for the Degree of Doctor of Philosophy To be presented, by permission of the Faculty of Mathematics and Science of the University of Jyväskylä, for public examination in Auditorium FYS1 of the University of Jyväskylä on December 13th, 2018 at 12 o’clock noon Jyväskylä, Finland December 2018 Preface The work reviewed in this thesis has been carried out during the years 2012 & 2014-2018 at the Department of Physics and Nanoscience Center in the University of Jyväskylä. First and foremost, I would like to thank my supervisor Doc. Andreas Jo- hansson for his guidance during my Erasmus internship and consequent Ph.D. studies. I am very grateful for his willingness to share both the professional com- petence and personal wisdom. Equal gratitude belongs to Prof. Mika Pettersson, without whom this project would never exist. His ability to see the big picture, his interesting insights, and genuine joy from the beauty of the microworld were a true motivation for me. It has been a great experience to work in the Nanoscience Center for all these years. I would like to express my gratitude to the whole staff for being supportive, sharing good ideas, or just having fun meaningful conversations. A special thanks goes to Prof. Janne Ihalainen for providing me access to the facilities of the Department of Biology. I humbly acknowledge the irreplaceable help of our technical staff, namely Dr. Kimmo Kinnunen, Mr. Tarmo Suppula, Dr. -

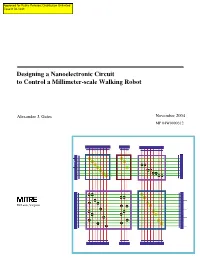

Designing a Nanoelectronic Circuit to Control a Millimeter-Scale Walking Robot

Designing a Nanoelectronic Circuit to Control a Millimeter-scale Walking Robot Alexander J. Gates November 2004 MP 04W0000312 McLean, Virginia Designing a Nanoelectronic Circuit to Control a Millimeter-scale Walking Robot Alexander J. Gates November 2004 MP 04W0000312 MITRE Nanosystems Group e-mail: [email protected] WWW: http://www.mitre.org/tech/nanotech Sponsor MITRE MSR Program Project No. 51MSR89G Dept. W809 Approved for public release; distribution unlimited. Copyright © 2004 by The MITRE Corporation. All rights reserved. Gates, Alexander Abstract A novel nanoelectronic digital logic circuit was designed to control a millimeter-scale walking robot using a nanowire circuit architecture. This nanoelectronic circuit has a number of benefits, including extremely small size and relatively low power consumption. These make it ideal for controlling microelectromechnical systems (MEMS), such as a millirobot. Simulations were performed using a SPICE circuit simulator, and unique device models were constructed in this research to assess the function and integrity of the nanoelectronic circuit’s output. It was determined that the output signals predicted for the nanocircuit by these simulations meet the requirements of the design, although there was a minor signal stability issue. A proposal is made to ameliorate this potential problem. Based on this proposal and the results of the simulations, the nanoelectronic circuit designed in this research could be used to begin to address the broader issue of further miniaturizing circuit-micromachine systems. i Gates, Alexander I. Introduction The purpose of this paper is to describe the novel nanoelectronic digital logic circuit shown in Figure 1, which has been designed by this author to control a millimeter-scale walking robot. -

MOSFET - Wikipedia, the Free Encyclopedia

MOSFET - Wikipedia, the free encyclopedia http://en.wikipedia.org/wiki/MOSFET MOSFET From Wikipedia, the free encyclopedia The metal-oxide-semiconductor field-effect transistor (MOSFET, MOS-FET, or MOS FET), is by far the most common field-effect transistor in both digital and analog circuits. The MOSFET is composed of a channel of n-type or p-type semiconductor material (see article on semiconductor devices), and is accordingly called an NMOSFET or a PMOSFET (also commonly nMOSFET, pMOSFET, NMOS FET, PMOS FET, nMOS FET, pMOS FET). The 'metal' in the name (for transistors upto the 65 nanometer technology node) is an anachronism from early chips in which the gates were metal; They use polysilicon gates. IGFET is a related, more general term meaning insulated-gate field-effect transistor, and is almost synonymous with "MOSFET", though it can refer to FETs with a gate insulator that is not oxide. Some prefer to use "IGFET" when referring to devices with polysilicon gates, but most still call them MOSFETs. With the new generation of high-k technology that Intel and IBM have announced [1] (http://www.intel.com/technology/silicon/45nm_technology.htm) , metal gates in conjunction with the a high-k dielectric material replacing the silicon dioxide are making a comeback replacing the polysilicon. Usually the semiconductor of choice is silicon, but some chip manufacturers, most notably IBM, have begun to use a mixture of silicon and germanium (SiGe) in MOSFET channels. Unfortunately, many semiconductors with better electrical properties than silicon, such as gallium arsenide, do not form good gate oxides and thus are not suitable for MOSFETs. -

Design and Analysis of Double Gate MOSFET Devices Using High-K Dielectric

International Journal of Electrical Engineering. ISSN 0974-2158 Volume 7, Number 1 (2014), pp. 53-60 © International Research Publication House http://www.irphouse.com Design and Analysis of Double Gate MOSFET Devices using High-k Dielectric Asha Balhara* and Divya Punia Department of E.C.E., B.P.S. Women University, khanpur kalan, Sonepat, India. *E-mail id: [email protected] Abstract Double gate MOSFET is one of the most promising and leading contender for Nano regime devices. In this paper an n-channel symmetric Double-Gate MOSFET using high-k (TiO2) dielectric with 80nm gate length is designed and simulated to study its electrical characteristics. ATHENA and ATLAS simulation tools from SILVACO are used in simulating electrical performance and analyzing the effectiveness of double gate MOSFET. High-k gate technology is emerging as a strong alternative for replacing the conventional SiO2 dielectrics gates in scaled MOSFETs for both high performance and low power applications. High-k oxides offer a solution to leakage problems that occur as gate oxide thickness’ are scaled down. Non-ideal effect of a MOSFET design such as short channel effects are investigated. The most common effect that generally occurs in the short channel MOSFETs are channel modulation, drain induced barrier lowering (DIBL). It is observed in the results that the device engineering would play an important role in optimizing the device parameters. Keywords- MOSFET-metal oxide semiconductor field effect transistor; DG- MOSFET-double-gate MOSFET; SG-MOSFET-single -

Advanced MOSFET Structures and Processes for Sub-7 Nm CMOS Technologies

Advanced MOSFET Structures and Processes for Sub-7 nm CMOS Technologies By Peng Zheng A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences in the Graduate Division of the University of California, Berkeley Committee in charge: Professor Tsu-Jae King Liu, Chair Professor Laura Waller Professor Costas J. Spanos Professor Junqiao Wu Spring 2016 © Copyright 2016 Peng Zheng All rights reserved Abstract Advanced MOSFET Structures and Processes for Sub-7 nm CMOS Technologies by Peng Zheng Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences University of California, Berkeley Professor Tsu-Jae King Liu, Chair The remarkable proliferation of information and communication technology (ICT) – which has had dramatic economic and social impact in our society – has been enabled by the steady advancement of integrated circuit (IC) technology following Moore’s Law, which states that the number of components (transistors) on an IC “chip” doubles every two years. Increasing the number of transistors on a chip provides for lower manufacturing cost per component and improved system performance. The virtuous cycle of IC technology advancement (higher transistor density lower cost / better performance semiconductor market growth technology advancement higher transistor density etc.) has been sustained for 50 years. Semiconductor industry experts predict that the pace of increasing transistor density will slow down dramatically in the sub-20 nm (minimum half-pitch) regime. Innovations in transistor design and fabrication processes are needed to address this issue. The FinFET structure has been widely adopted at the 14/16 nm generation of CMOS technology. -

Outline MOS Gate Dielectrics Incorporation of N Or F at the Si/Sio

MOS Gate Dielectrics Outline •Scaling issues •Technology •Reliability of SiO2 •Nitrided SiO2 •High k dielectrics araswat tanford University 42 EE311 / Gate Dielectric Incorporation of N or F at the Si/SiO2 Interface Incorporating nitrogen or fluorine instead of hydrogen strengthens the Si/SiO2 interface and increases the gate dielectric lifetime because Si-F and Si-N bonds are stronger than Si-H bonds. Nitroxides – Nitridation of SiO2 by NH3 , N2O, NO Poly-Si Gate – Growth in N2O – Improvement in reliability – Barrier to dopant penetration from poly-Si gate Oxide N or F – Marginal increase in K – Used extensively Si substrate Fluorination – Fluorination of SiO2 by F ion implantation – Improvement in reliability – Increases B penetration from P+ poly-Si gate – Reduces K – Not used intentionally – Can occur during processing (WF6 , BF2) araswat tanford University 43 EE311 / Gate Dielectric 1 Nitridation of SiO2 in NH3 H • Oxidation in O2 to grow SiO2. • RTP anneal in NH3 maximize N at the interface and minimize bulk incorporation. • Reoxidation in O2 remove excess nitrogen from the outer surface • Anneal in Ar remove excess hydrogen from the bulk • Process too complex araswat tanford University 44 EE311 / Gate Dielectric Nitridation in N2O or NO Profile of N in SiO2 Stress-time dependence of gm degradation of a NMOS SiO2 Ref. Bhat et.al IEEE IEDM 1994 (Ref: Ahn, et.al., IEEE Electron Dev. Lett. Feb. 1992) •The problem of H can be circumvented by replacing NH3 by N2O or NO araswat tanford University 45 EE311 / Gate Dielectric 2 Oxidation of Si in N2O N2O → N2 + O N2O + O → 2NO Ref: Okada, et.al., Appl. -

Organic Light-Emitting Transistors with Optimized Gate Dielectric

Organic light-emitting transistors with optimized gate dielectric Supervisor: Jakob Kjelstrup-Hansen Per B. W. Jensen Jian Zeng JUNE, 2013 ABSTRACT Organic materials have been developed as promising candidates in a variety of electronic and optoelectronic applications due to its semiconducting properties, synthesis, low temperature processing and plastic film compatibility. Hence, the organic light emitting transistor (OLET) has attracted considerable interest in realizing large-area optoelectronic devices and made tremendously progress in recent years. In order to further improve the device performance, one possibility is to optimize the gate dielectric material. Typically, silicon dioxide (SiO2) works as gate dielectric. However, SiO2 traps electrons at the semiconductor/dielectrics interface, which can prevent charge carriers transport. Therefore, the focus of this project is to look into the performance of OLETs with optimized gate dielectrics and investigate the improvement compared with conventional OLETs. The optimized gate dielectric used in this project is poly(methyl methacrylate) (PMMA), which is a promising polymer material. The device is developed with bottom contact/bottom gate (BC/BG) and top contact/bottom gate (TC/BG) configuration. Taking BC/BG configuration as an example, in an OLET, silicon substrate PPTTPP thin film acting as organic semiconductor is connect to gold (Au) source and drain electrodes, which is positioned on top of PMMA layer on Au bottom layer. Aluminum (Al) also be investigated as source and drain electrode. Then a suitable microfabrication recipe is introduced, which involves the fabrication recipe of stencil. The fabrication process is realized in clean room and optical lab, followed by the electrical and optical measurements to characterize the devices. -

14Ec230-Semiconductor Devices Innovative Method

14EC230-SEMICONDUCTOR DEVICES INNOVATIVE METHOD N.B.Balamurugan Associate Professor ECE Department Thiagarajar College of Engineering Madurai-15 nbbalamurugan @tce.edu 09894346320 1928 • The first patents for the transistor principle were registered in Germany by Julius Edgar Lilienfield. • He proposed the basic principle behind the MOS field-effect transistor. 2 1934 • German Physicist Dr. Oskar Heil patented the Field Effect Transistor 3 1936 • Mervin Kelly Bell Lab's director of research. He felt that to provide the best phone service it will need a better amplifier; the answer might lie in semiconductors. And he formed a department dedicated to solid state science. 4 1945 • Bill Shockley the team leader of the solid state department (Hell’s Bell Lab) hired Walter Brattain and John Bardeen. • He designed the first semiconductor amplifier, relying on the field effect. • His device was a small cylinder coated thinly with silicon, mounted close to a small, metal plate. • The device didn't work, and Shockley assigned Bardeen and Brattain to find out why. 5 1949 cont. • Shockley make the Junction transistor (sandwich). • This transistor was more practical and easier to fabricate. • The Junction Transistor became the central device of the electronic age 6 ENIAC – First electronic computer (1946) • Built by John W. Mauchly (Computer Architecture) and J. Presper Eckert (Circuit Engineering) , Moore School of Electrical Engineering, University of Pennsylvania. Formed Eckert & Marchly Computer Co. and built the 2nd computer, “UNIVAC”. Went bankrupt in 1950 and sold to Remington Rand (now defunct). IBM built “401” in 1952 (1st commercial computer) and John von Neumann invented controversial concept of interchangeable data and programs. -

Gate Oxide Reliability: Physical and Computational Models

Gate Oxide Reliability: Physical and Computational Models Andrea Ghetti 1 Introduction Since its birth, the microelectronics industry has been characterized by the continuous struggle to find new technological processes that allow the re- duction of the physical dimensions of the devices integrated in a single chip of silicon. As matter of fact, since the invention of the first integrated cir- cuit (IC) the number of single devices per chip has kept doubling every 18 months, that corresponds to a steady exponential growth over the last 30 years. Such shrinking process is driven by the fact that smaller device op- erate at higher speeds and allow the integration of more and more complex circuits of the same area of silicon making each single function less and less expensive. However, the operating voltage does not scale with the same pace, hence the electric fields inside the devices keep increasing. This leads to a degradation of the device performance over time even during normal oper- ation. Therefore, it is necessary to guarantee that microelectronics product performance remains within the customer’s specifications for a determined period of time. This is the concept of reliability. The large majority of the microelectronics products are bases on the Metal-Oxide-Semiconductor (MOS) transistor that is schematically shown in Fig. 1. Two heavily doped regions are formed in a semiconductor sub- strate to make the source and drain extensions. The gate electrode is built between source and drain over an insulator layer of silicon dioxide (or sim- ply ”oxide”), and controls the conduction between source and drain through the electric field across the oxide. -

Investigation of Gate Dielectric Materials and Dielectric/Silicon Interfaces for Metal Oxide Semiconductor Devices

University of Kentucky UKnowledge Theses and Dissertations--Electrical and Computer Engineering Electrical and Computer Engineering 2015 Investigation of Gate Dielectric Materials and Dielectric/Silicon Interfaces for Metal Oxide Semiconductor Devices Lei Han University of Kentucky, [email protected] Right click to open a feedback form in a new tab to let us know how this document benefits ou.y Recommended Citation Han, Lei, "Investigation of Gate Dielectric Materials and Dielectric/Silicon Interfaces for Metal Oxide Semiconductor Devices" (2015). Theses and Dissertations--Electrical and Computer Engineering. 69. https://uknowledge.uky.edu/ece_etds/69 This Doctoral Dissertation is brought to you for free and open access by the Electrical and Computer Engineering at UKnowledge. It has been accepted for inclusion in Theses and Dissertations--Electrical and Computer Engineering by an authorized administrator of UKnowledge. For more information, please contact [email protected]. STUDENT AGREEMENT: I represent that my thesis or dissertation and abstract are my original work. Proper attribution has been given to all outside sources. I understand that I am solely responsible for obtaining any needed copyright permissions. I have obtained needed written permission statement(s) from the owner(s) of each third-party copyrighted matter to be included in my work, allowing electronic distribution (if such use is not permitted by the fair use doctrine) which will be submitted to UKnowledge as Additional File. I hereby grant to The University of Kentucky and its agents the irrevocable, non-exclusive, and royalty-free license to archive and make accessible my work in whole or in part in all forms of media, now or hereafter known. -

Microelectronic Device Fabrication I Physics 445/545 Integration

Microelectronic Device Fabrication I (Basic Chemistry and Physics of Semiconductor Device Fabrication) Physics 445/545 Integration Seminar Dec. 1 & 3, 2014 Chip Fabrication • From bare Si wafers to fully functional IC’s requires a complicated series of processing steps. • Cleanliness regimen must be rigorous. Jack Kilby inspecting a 300 mm wafer (courtesy TI) Moore’s Law The IC was invented independently in 1959 by Jack Kilby at TI and Robert Noyce at Fairchild (later one of the founders of Intel). In 1965, Intel co-founder Gordon Moore saw the future. His prediction, now popularly known as Moore’s Law, states that the number of transistors on a chip doubles about every two years. Gordon Moore’s original graph from 1965 Today, Intel leads the industry with: • A worldwide silicon fab. Advanced technologies, such as “tri-gate” for improved performance, in production today • Research into new technologies that will enable Intel to continue the 2- year cycle of Moore’s Law for the foreseeable future (courtesy: Intel Corp.) Challenge to Moore’s Law 45 40 35 Gate Delay 30 Interconnect Delay (Al/SiO2) 25 Interconnect Delay (Cu/Low k) 20 Delay (ps) Delay Sum of Delays (Al/SiO2) 15 Sum of Delays 10 (Cu/Low k) 5 0 650 500 350 250 180 130 100 Generation (nm) SIA Technology Roadmap SIA Technology Roadmap-update SIA Technology Roadmap “Acceleration” “More than Moore” Speculative Future Technologies Long range roadmap for logic CMOS transistor research Photolithography Photolithography: • Simple photo-transfer technique quite similar in many respects to ordinary black and white photography. • The master image or pattern resides on a “mask” or “reticule” that consists of a plate of quartz glass initially coated on one side by a thin layer of metallic chromium. -

CSET Issue Brief

SEPTEMBER 2020 The Chipmakers U.S. Strengths and Priorities for the High-End Semiconductor Workforce CSET Issue Brief AUTHORS Will Hunt Remco Zwetsloot Table of Contents Executive Summary ............................................................................................... 3 Key Findings ...................................................................................................... 3 Workforce Policy Recommendations .............................................................. 5 Introduction ........................................................................................................... 7 Why Talent Matters and the American Talent Advantage .............................. 10 Mapping the U.S. Semiconductor Workforce .................................................. 12 Identifying and Analyzing the Semiconductor Workforce .......................... 12 A Large and International Workforce ........................................................... 14 The University Talent Pipeline ........................................................................ 16 Talent Across the Semiconductor Supply Chain .......................................... 21 Chip Design ................................................................................................ 23 Electronic Design Automation ................................................................... 24 Fabrication .................................................................................................. 24 Semiconductor Manufacturing Equipment (SME) Suppliers