(VTS 2010) Santa Cruz, CA, April 19-21, 2010

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

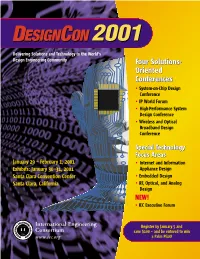

Oriented Conferences Four Solutions

Delivering Solutions and Technology to the World’s Design Engineering Community Four Solutions- Oriented Conferences • System-on-Chip Design Conference • IP World Forum • High-Performance System Design Conference • Wireless and Optical Broadband Design Conference Special Technology Focus Areas January 29 – February 1, 2001 • Internet and Information Exhibits: January 30–31, 2001 Appliance Design Santa Clara Convention Center • Embedded Design Santa Clara, California • RF, Optical, and Analog Design NEW! • IEC Executive Forum International Engineering Register by January 5 and Consortium save $100 – and be entered to win www.iec.org a Palm Pilot! Practical Design Solutions Practical design-engineering solutions presented by practicing engineers—The DesignCon reputation of excellence has been built largely by the practical nature of its sessions. Design engineers hand selected by our team of professionals provide you with the best electronic design and silicon-solutions information available in the industry. DesignCon provides attendees with DesignCon has an established reputation for the high design solutions from peers and professionals. quality of its papers and its expert-level speakers from Silicon Valley and around the world. Each year more than 100 industry pioneers bring to light the design-engineering solutions that are on the leading edge of technology. This elite group of design engineers presents unique case studies, technology innovations, practical techniques, design tips, and application overviews. Who Should Attend Any professionals who need to stay on top of current information regarding design-engineering theories, The most complete educational experience techniques, and application strategies should attend this in the industry conference. DesignCon attracts engineers and allied The four conference options of DesignCon 2001 provide a professionals from all levels and disciplines. -

Organising Committees

DATE 2005 Executive Committee GENERAL CHAIR PROGRAMME CHAIR Nobert Wehn Luca Benini Kaiserslautern U, DE DEIS – Bologna U, IT VICE CHAIR & PAST PROG. CHAIR VICE PROGRAMME CHAIR Georges Gielen Donatella Sciuto KU Leuven, BE Politecnico di Milano, IT FINANCE CHAIR PAST GENERAL CHAIR Rudy Lauwereins Joan Figueras IMEC, Leuven, BE UP Catalunya, Barcelona, ES DESIGNERS’ FORUM DESIGNERS’ FORUM Menno Lindwer Christoph Heer Philips, Eindhoven, NL Infineon, Munich, DE SPECIAL SESSIONS & DATE REP AT DAC FRIDAY WORKSHOPS Ahmed Jerraya Bashir Al-Hashimi TIMA, Grenoble, FR Southampton U, UK INTERACTIVE PRESENTATIONS ELECTRONIC REVIEW Eugenio Villar Wolfgang Mueller Cantabria U, ES Paderborn U, DE WEB MASTER AUDIO VISUAL Udo Kebschull Jaume Segura Heidelberg U, DE Illes Baleares U, ES TUTORIALS & MASTER COURSES FRINGE MEETINGS Enrico Macii Michel Renovell Politecnico di Torino, IT LIRMM, Montpellier, FR AUTOMOTIVE DAY BIOCHIPS DAY Juergen Bortolazzi Christian Paulus DaimlerChrysler, DE Infineon, Munich, DE PROCEEDINGS EXHIBITION PROGRAMME Christophe Bobda Juergen Haase Erlangen U, DE edacentrum, Hannover, DE UNIVERSITY BOOTH UNIVERSITY BOOTH & ICCAD Volker Schoeber REPRESENTATIVE edacentrum, Hannover, DE Wolfgang Rosenstiel Tuebingen U/FZI, DE AWARDS & DATE REP. AT ASPDAC PCB SYMPOSIUM Peter Marwedel Rainer Asfalg Dortmund U, DE Mentor Graphics, DE TRAVEL GRANTS COMMUNICATIONS Marta Rencz Bernard Courtois TU Budapest, HU TIMA, Grenoble, FR LOCAL ARRANGEMENTS PRESS LIASON Volker Dueppe Fred Santamaria Siemens, DE Infotest, Paris, FR ESF CHAIR & EDAA -

Exhibition Report

Exhibition Report Japan Electronics and Information Technology Industries Association (JEITA) Contents Exhibition Outline 1 Exhibition Configuration 2 1. Scope of Exhibits 2 2. Conference 2 3. Number of Exhibitors and Booths 2 4. Suite Exhibits 2 5. Exhibitors 3 Conference Activities 4 1. Exhibitor Seminars 4 2. Keynote Speech 4 3. Special Event Stage 4 4. The 13th FPGA/PLD Design Conference 4 5. FPGA/PLD Design Conference User’s Presentations 4 6. IP(Intellectual Property) Flea Market in EDSFair 4 7. System Design Forum 2006 Conference 4 Other Events and Special Projects 5 1. Opening Ceremony 5 2. University Plaza 5 3. Venture Conpany Pavilion 5 4. EDAC Reception 5 5. Press 5 Number of Visitors 6 Results of Visitor Questionnaire 6-7 Exhibition Outline Name . Electronic Design and Solution Fair 2006 (EDSFair2006) Duration . Thursday, January 26 and Friday, January 27, 2006 (2 days) 10:00 a.m. to 6:00 p.m. Location . Pacifico Yokohama (Halls C-D hall and Annex Hall) 1-1-1 Minato Mirai, Nishi-ku, Yokohama 220-0012, Japan Admission. Exhibition: Free (registration required at show entrance) Conference: Fees charged for some sessions Sponsorship . Japan Electronics and Information Technology Industries Association (JEITA) Cooperation . Electronic Design Automation Consortium (EDAC) Support . Ministry of the Economy, Trade and Industry, Japan (METI) Embassy of the United States of America in Japan Distributors Association of Foreign Semiconductors (DAFS) City of Yokohama Assistance . Institute of Electronics, Information and Communication Engineers (IEICE) Information Processing Society of Japan (IPSJ) Japan Printed Circuit Association (JPCA) Spacial Assistance. Hewlett-Packard Japan, Ltd. Sun Microsystems K.K Management . -

28Th IEEE VLSI Test Symposium (VTS 2010) Santa Cruz, CA, April 19-21, 2010

28th IEEE VLSI Test Symposium (VTS 2010) Santa Cruz, CA, April 19-21, 2010 Preliminary Program (as of 3/25/10) Monday, 4/19/10 Plenary Session (9:00 – 11:00) Break (11:00 – 11:15) Sessions 1 (11:15 – 12:15) Session 1A: Delay & Performance Test 1 Moderator: M. Batek - Broadcom Fast Path Selection for Testing of Small Delay Defects Considering Path Correlations Z. He, T. Lv - Institute of Computing Technology, H. Li, X. Li - Chinese Academy of Sciences Identification of Critical Primitive Path Delay Faults without any Path Enumeration K. Christou, M. Michael, S. Neophytou - University of Cyprus Path Clustering for Adaptive Test T. Uezono, T. Takahashi - Tokyo Institute of Technology, M. Shintani , K. Hatayama - Semiconductor Technology Academic Research Center, K. Masu - Tokyo Institute of Technology, H. Ochi, T. Sato - Kyoto University Session 1B: Memory Test & Repair Moderator: P. Prinetto - Politecnico di Torino Automatic Generation of Memory Built-In Self-Repair Circuits in SOCs for Minimizing Test Time and Area Cost T. Tseng, C. Hou, J. Li - National Central University Bit Line Coupling Memory Tests for Single Cell Fails in SRAMs S. Irobi, Z. Al-ars, S. Hamdioui - Delft University of Technology Reducing Test Time and Area Overhead of an Embedded Memory Array Built-In Repair Analyzer with Optimal Repair Rate J. Chung, J. Park - The University of Texas at Austin, E. Byun, C. Woo - Samsung Electronics, J. Abraham - The University of Texas at Austin IP Session 1C: Innovative Practices in RF Test Organizer: R. Parekhji - Texas Instruments Moderator: TBA Test Time Reduction Using Parallel RF Test Techniques R. -

PLM Industry Summary Editor: Christine Bennett Vol

PLM Industry Summary Editor: Christine Bennett Vol. 11 No. 4 Friday 23 January 2009 Contents Acquisitions _______________________________________________________________________ 2 Autodesk Completes Acquisition of ALGOR, Inc. _____________________________________________2 Mentor Graphics Extends High Level Synthesis Leadership with Acquisition of Agility Design Solutions Inc. C Synthesis Suite ____________________________________________________________________3 Company News _____________________________________________________________________ 3 Anark Names Chris Garcia Senior Vice President, Business Development ___________________________3 Autodesk Manufacturing Community to Select 2008 Inventor of the Year Award Winner ______________4 Delcam Offers Free ArtCAM Demo Software for Artistic Users __________________________________5 DP signs Agreement with Italian Lathe Manufacturer GRAZIANO Tortona S.r.l. _____________________6 DP Technology Moves its Midwest Team to a Larger, New and Improved Site _______________________6 DP Technology Signs Agreement with Italian Machine-Tool Builder Salvadeo S.r.l. __________________7 Kalypso and Endeca Announce Partnership in Support of Engineering and PLM-Related Information Visibility Solutions ______________________________________________________________________7 New WorkXPlore 3D Website Allows Engineers to Download High Speed Collaborative CAD Viewer Free _____________________________________________________________________________________8 Si2’s Open Modeling Coalition Releases Document on Statistical -

When Innovation Is Hard

WhenWhen InnovationInnovation isis HardHard Does the Open Source Development Model Work in Hardware? ilkka.tuomi meaningprocessing.com © I. Tuomi 2 Oct. 2008 page: 1 ThesesTheses • 1. Software and hardware are epistemologically different artifacts • This leads to different innovation and conflict models in software and hardware projects • The success of the open distributed approach in ”close-to-hardware” software development (e.g. Linux kernel) is partly explained by this epistemological difference • 2. Close-to-hardware software, social software, and hardware are different • Close-to-hardware software development is easy to distribute because the developer community consists of a homogenous network of people and tools • There exists a ”phenomenological bottleneck:” Real hardware can only be approximated using digital representations; distributed hardware projects can therefore be really hard • There also exists a ”political bottleneck:” Social software can be hard as there are multiple interpretations and systems of meaning © I. Tuomi 2 Oct. 2008 page: 2 DifferentDifferent TypesTypes ofof AnimalsAnimals RequireRequire DifferentDifferent StylesStyles ofof BreedingBreeding • Close-to-hardware SW • HW • In a given HW environment: • The context is the open world: SW is both the description and the Unmodeled features matter implementation Systems wear, tear and break down Mapping between software and the Although dominant voices are loudest, functionality of the system is one-to-one evaluation criteria have to be negotiated Technical functionality can be empirically from multiple perspectives tested • A homogenous developer community, • A homogenous developer community, rooted in its own ”objective reality.” rooted in its own ”professional reality.” or: • A network of interacting communities, each with their own stocks of knowledge. -

FPGA Based High Speed Memory BIST Controller for Embedded Applications

ISSN (Print) : 0974-6846 Indian Journal of Science and Technology, Vol 8(33), DOI: 10.17485/ijst/2015/v8i33/76080, December 2015 ISSN (Online) : 0974-5645 FPGA based High Speed Memory BIST Controller for Embedded Applications Mohammed Altaf Ahmed1*, D. Elizabeth Rani1 and Syed Abdul Sattar2 1GITAM Institute of Technology, GITAM University, Visakhapatnam – 531173, Andhra Pradesh, India; [email protected], [email protected]; [email protected] 2Royal Institute of Technology and Science, Chevella – 501503, Andhra Pradesh, India; [email protected] Abstract In the current high speed, low power VLSI Technology design, Built in Self Test (BIST) is emerging as the most essential based algorithms are become popular so quickly for locating faults in memories. This research study attempt to design the part of System on Chip (SoC). The industries are flooded with diverse algorithms to test memories for faults. The March implemented in Verilog Hardware Description Language (HDL), which can be easily integrate with SoC and is able to locate memory BIST controller for March 17N as selected algorithm. It tests various memories for faults. A simple architecture is the fault location in the semiconductor memories. Integration of memory BIST controller in SoC design improves chip yield. The design has achieved 497.47MHzof maximum frequency by use of only 158 slice LUTs on Virtex-7 Field Programming Gate Array (FPGA) device. The proposed memory BIST controller is suitable for SoC integration to test various memories atKeywords: high speed with very low area overhead. Low Area, Memory BIST, SoC Integration, Test Memories, Yield Improvement 1. Introduction percent till 2014. The International Technology Roadmap for Semiconductors (ITRS) report is available for public2,3 Embedded memories in Integrated circuit and System on to track the survey. -

Automated Bus Generation for Multi-Processor Soc Design

AUTOMATED BUS GENERATION FOR MULTI-PROCESSOR SOC DESIGN A Dissertation Presented to The Academic Faculty by Kyeong Keol Ryu In Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy School of Electrical and Computer Engineering Georgia Institute of Technology June 2004 AUTOMATED BUS GENERATION FOR MULTI-PROCESSOR SOC DESIGN Approved by: Dr. Vincent J. Mooney III, Adviser Dr. Jeffrey A. Davis Dr. Sudhakar Yalamanchili Dr. Paul Benkeser Dr. Thad Starner Date Approved: June 11, 2004 Dedicated to my wife, Hyejung Hyeon, my parents, and my parents-in-law iii ACKNOWLEDGMENTS This work could have not been finished without the support and sacrifice of many people I had to express my gratitude. First of all, I would like to deeply thank my adviser Vincent J. Mooney III. He has supported and encouraged me to develop my dissertation with his enthusiasm and professionalism throughout all stages of my Ph.D. program. He has been a great source of ideas and provided me with invaluable feedback. In addition, Dr. Mooney has been helping me improve my English skills with his consideration. I would also like to extend my appreciation to Dr. Jeffrey Davis, Dr. Sudhakar Yalamanchili, Dr. Paul Benkeser, and Dr. Thad Starner for serving on the committee and offering constructive comments. I have to thank all Hardware/Software Codesign group members for their helps and friendship. It is obvious that, without many helps by them, my long journey at Georgia Tech would have been much harder and lonelier. Also, I wish to thank my friends, Dr. Chang-ho Lee, Dr. -

Technical Program Topic Chairs

TOtePchIniCca lC pHrogAraImRmSe topic chairs 0 System Specification and Modelling Physical Design and Verification System and Industrial Test 1 E Eugenio Villar Igor L Markov Erik Jan Marinissen T A Cantabria U, ES U of Michigan, US IMEC, BE D Grant Martin Jens Lienig Peter Harrod Tensilica, US TU Dresden, DE ARM, UK y n MPSoC and System Design Methods Virtualisation Technologies Design for Test and BIST a m r Andy Pimentel Andre Brinkmann Krishnendu Chakrabarty e G Amsterdam U, NL Paderborn U, DE Duke U, US , Wido Kruijtzer Mike Kreiten Sandeep Kumar Goel n e Virage Logic, NL AMD, DE LSI CORP, US d s e System Synthesis and Optimisation Analogue and Mixed-Signal Systems Test Generation, Simulation and r D and Circuits Diagnosis Peter Marwedel , C Dortmund U, DE Tom Kazmierski Nicola Nicolici C I Samarjit Chakraborty Southampton U, UK McMaster U, Hamilton, CA TU Munich, DE Christoph Grimm Bart Vermeulen 0 TU Vienna, AT NXP, NL 1 Simulation and Validation 0 2 Interconnect, EMC, ESD and On-Line Testing and Fault Tolerance Ian Harris h Packaging Modelling c UC Irvine, US Dimitris Gizopoulos r Valeria Bertacco Wil Schilders Piraeus U, GR a M U of Michigan, US NXP, NL Davide Appello 2 Tom Dhaene STMicroelectronics, IT 1 Design of Low Power Systems - Ghent U, BE Test for Variability, Reliability and 8 Miguel Miranda Signal Processing for Multimedia Defects IMEC, BE Alberto Macii Christos-Savvas Bouganis Sandip Kundu Politecnico di Torino, IT Imperial College, UK Massachusetts U, US Power Estimation and Optimisation Sergio Saponara Rob Aitken -

VTS08 Technical Program

Technical Program 26th IEEE VLSI TEST SYMPOSIUM (VTS 2008) http://www.tttc-vts.org/ http://tab.computer.org/tttc 26th IEEE VLSI TEST SYMPOSIUM SYMPOSIUM COMMITTEES ORGANIZING COMMITTEE General Chair A. Orailoglu – UC San Diego Program Co-Chairs P. Maxwell – Micron C. Metra – U of Bologna Past Chair P. Prinetto – Polit di Torino Vice-General Co-Chairs S.M. Reddy - U Iowa H.-J. Wunderlich - U Stuttgart Vice-Program Chair M. Renovell – LIRMM Finance M. Abadir – Freescale New Topics B. Courtois – CMP Publications S. Ravi - Texas Instr. Innovative Practices Track K. Hatayama - STARC S. Mitra - Stanford U Special Sessions L. Anghel – TIMA C.P. Ravikumar – Texas Instr. Publicity Chair C.-H. Chiang – Alcatel-Lucent Publicity Sub-Committee I. Bayraktaroglu - Sun Micro. S. Di Carlo - Polit di Torino G. DI Natale - LIRMM Local Arrangements I. Harris – UC Irvine Audio/Visual S. Hellebrand – U Paderborn Registration C. Thibeault– ETS Montreal Latin America Liaison L. Carro – UFRGS North America Liaison R. Kapur – Synopsys Asia & Pacifi c Liaison Y. Sato – Hitachi Eastern Europe Liaison R. Ubar – Tallinn U Western Europe Liaison Z. Peng – Linkoping U Middle East & Africa Liaison R. Makki– UAE U Ex-Offi cio Y. Zorian - Virage Logic PROGRAM COMMITTEE J. A. Abraham – U.T. Austin Y. Makris – Yale U V. D. Agrawal – Auburn U E.J. Marinissen – NXP D. Appello – ST Micro. E.J. McCluskey – Stanford U K. Arabi – PMC-Sierra L. Milor – Georgia Tech B. Becker – U Freiburg S. Mourad – Santa Clara U C.J. Clark – Intellitech P. Muhmenthaler – Infi neon B. Cory – Nvidia Z. Navabi – Worcester Poly. R. Galivanche – Intel S. -

Who Drives Soc Chips:Applications Or Silicon ? Pierre Bricaud Director

Who drives SoC Chips:Applications or Silicon ? Pierre Bricaud Director, R&D Solutions Group Synopsys, Inc. Sophia Antipolis SoC is not just HW, its HW+SW+Application System Trade-Offs SOFTWARE HARDWARE Digital Embedded Embedded Analog Cores Logic/ Software ion Loop ion Loop Memory t t a a r r Integration & ite ite Integration & e e Verification Verification R R Integration & Verification Manufacturing • Multiple Technologies - Hardware/Software, Analog/Digital • Multiple Teams - Hardware (Analog/Digital), Software, System • Multiple Embedded Systems - IP Cores © 2003 Synopsys, Inc. (2) Average Gate Count Continues to Grow 30% 25% 20% 2000 2002 15% 2001 2003 10% 5% 0% <.1M © 2003 Synopsys, Inc. (3) .1-.3M .301-.5M 36% of designs in .501-1M 2003 >4M gates .101-1.5M Data from Synopsys SN 1.501-2M 26% 2.001-2.5M 2.501-3M UG 3.001-3.5M 10% San Jose 2003 seminar survey 3.501-4M 4.001-4.5M 4.501-5M >5.001M Design Keeps Getting More Complex 180nm 130nm 90nm 65nm Computing Parallelism 64 Bits IP IP 30% 50% 70% 90% Flow Hierarchy Large designs Database Partial Partial Integrated Integrated API Proprietary Open Open Open S, P&R S, P&R S&P - R S&P - R Integrated Integrated Handoff Placed Gates Placed Gates Layout Layout Timing TC SI L for Busses 1.5GHz 1.5GHz 1.5GHz Clocking Cycles across Chip 1 Few Few Many Clocking Sync Sync Sync/Async Sync/Async IR drop Power Power Power Power&Signal © 2003 Synopsys, Inc. (4) Design Keeps Getting More Complex 180nm 130nm 90nm 65nm Power Clock Gating Multi Vdd Multi Vth (leakage) Test Scan Mem Bist Logic Bist Design for Debug RET OPC PSM DR for RET DFM Statistical Timing PD for DFM Analog P&R Manual Semi-Auto Semi-Auto Semi-Auto Synthesis Manual Manual Semi-Auto Semi-Auto Package Spice Chip/Pack. -

Sia 2005 Annual Report Contents

SEMICONDUCTOR INDUSTRY ASSOCIATION 2005 ANNUAL REPORT 2020 IS CLOSER THAN YOU THINK SIA 2005 ANNUAL REPORT CONTENTS Letter from the President 6 The Man Behind the Law 8 40 Years of Moore’s Law 10 Moore’s Law and the Emergence of the New Economy 16 About SIA 21 SIA Agenda Domestic Policy 23 Environment, Safety, and Health 25 Economy 28 World Markets 30 Technology 33 Workforce 36 2004 Robert N. Noyce Award 39 SIA Board of Directors 40 Committees 41 Member Profiles 49 Corporate Associates 61 SIA Staff 64 LAST YEAR, MORE TRANSISTORS WERE PRODUCED—AND AT A LOWER COST—THAN GRAINS OF RICE. 2 / SIA 2005 ANNUAL REPORT VIRTUALLY EVERY ASPECTCHIP OF HUMANAT CONSTANTLY ENDEAVOR. DECLINING AN EVER-INCREASING COST HAS REVOLUTIONIZED NUMBERTO DOUBLE OF COMPONENTS EVERY COUPLE ASONTO OFTHE AYEARS—THIS COMPLEXITY ABILITY OFCONTINUOUS INTEGRATED TO CRAM PROGRESSCIRCUITS ITINHAS ISSEMICONDUCTOR CONTINUED IMPOSSIBLE TOTECHNOLOGY. 40OVERSTATE YEARS THEOF EXPONENTIALIMPACT OF 40 PROGRESS YEARS OF MOORE’S* LAW: Transistors perintegratedcircuit: Transistors 1965 / he extendedtheamountoftimeto24months. with acommensuratereductionincostpercomponent.In1970, on anintegratedcircuitwasdoublingroughlyevery12months In 1965,GordonMooreobservedthatthenumberofcomponents 1966 / 1967 / 1968 / 1969 / 1970 / 1971 / 1972 / 2,500 1,000 1973 / 1974 / 3,200 4,000 Logic 1975 / 1976 / / Memory 1977 / 1978 / 29,000 16,000 1979 / 1980 / 1981 / 1982 / 120,000 64,000 1983 / 1984 / 1985 / 1986 / 275,000 256,000 1987 / 1988 / 1989 / 1990 / 1,180,000 1,000,000 1991 / 1992 / 1993 / 1994 / 3,100,000 4,000,000 1995 / 1996 / 7,500,000 16,000,000 1997 / 1998 / 24,000,000 64,000,000 1999 / 2000 / 42,000,000 128,000,000 2001 / 2002 / 220,000,000 256,000,000 2003 / 2004 / 410,000,000 256,000,000 2005 / 1,700,000,000 1,000,000,000 IN 1978, A COMMERCIAL FLIGHT BETWEEN NEW YORK AND PARIS COST $900 AND TOOK SEVEN HOURS.