The Design of a Custom 32-Bit SIMD Enhanced Digital Signal Processor

Total Page:16

File Type:pdf, Size:1020Kb

Load more

Recommended publications

-

DSP56303 Product Brief, Rev

Freescale Semiconductor DSP56303PB Product Brief Rev. 2, 2/2005 DSP56303 24-Bit Digital Signal Processor 16 6 6 3 Memory Expansion Area The DSP56303 is intended Triple X Data HI08 ESSI SCI PrograM Y Data for use in telecommunication Timer RAM RAM RAM 4096 × 24 2048 × 24 2048 × 24 applications, such as multi- bits bits bits line voice/data/ fax (default) (default) (default) processing, video Peripheral Expansion Area conferencing, audio PM_EB XM_EB PIO_EB YAB YM_EB applications, control, and Address External 18 Generation XAB Address general digital signal Unit PAB Bus Address Six-Channel DAB Switch processing. DMA Unit External 24-Bit Bus 13 Bootstrap DSP56300 Interface ROM and Inst. Core Cache Control Control DDB 24 Internal YDB External Data XDB Data Bus Bus PDB Switch Data Switch GDB EXTAL Power Clock Management Data ALU 5 Generator Program Program Program × + → XTAL Interrupt Decode Address 24 24 56 56-bit MAC JTAG PLL Two 56-bit Accumulators Controller Controller Generator 56-bit Barrel Shifter OnCE™ DE 2 MODA/IRQA MODB/IRQB RESET MODC/IRQC PINIT/NMI MODD/IRQD Figure 1. DSP56303 Block Diagram The DSP56303 is a member of the DSP56300 core family of programmable CMOS DSPs. Significant architectural features of the DSP56300 core family include a barrel shifter, 24-bit addressing, instruction cache, and DMA. The DSP56303 offers 100 million multiply-accumulates per second (MMACS) using an internal 100 MHz clock at 3.0–3.6 volts. The DSP56300 core family offers a rich instruction set and low power dissipation, as well as increasing levels of speed and power to enable wireless, telecommunications, and multimedia products. -

Low Power Asynchronous Digital Signal Processing

LOW POWER ASYNCHRONOUS DIGITAL SIGNAL PROCESSING A thesis submitted to the University of Manchester for the degree of Doctor of Philosophy in the Faculty of Science & Engineering October 2000 Michael John George Lewis Department of Computer Science 1 Contents Chapter 1: Introduction ....................................................................................14 Digital Signal Processing ...............................................................................15 Evolution of digital signal processors ....................................................17 Architectural features of modern DSPs .........................................................19 High performance multiplier circuits .....................................................20 Memory architecture ..............................................................................21 Data address generation .........................................................................21 Loop management ..................................................................................23 Numerical precision, overflows and rounding .......................................24 Architecture of the GSM Mobile Phone System ...........................................25 Channel equalization ..............................................................................28 Error correction and Viterbi decoding ...................................................29 Speech transcoding ................................................................................31 Half-rate and enhanced -

Rlsc & DSP Advanced Microprocessor System Design

Purdue University Purdue e-Pubs ECE Technical Reports Electrical and Computer Engineering 3-1-1992 RlSC & DSP Advanced Microprocessor System Design; Sample Projects, Fall 1991 John E. Fredine Purdue University, School of Electrical Engineering Dennis L. Goeckel Purdue University, School of Electrical Engineering David G. Meyer Purdue University, School of Electrical Engineering Stuart E. Sailer Purdue University, School of Electrical Engineering Glenn E. Schmottlach Purdue University, School of Electrical Engineering Follow this and additional works at: http://docs.lib.purdue.edu/ecetr Fredine, John E.; Goeckel, Dennis L.; Meyer, David G.; Sailer, Stuart E.; and Schmottlach, Glenn E., "RlSC & DSP Advanced Microprocessor System Design; Sample Projects, Fall 1991" (1992). ECE Technical Reports. Paper 302. http://docs.lib.purdue.edu/ecetr/302 This document has been made available through Purdue e-Pubs, a service of the Purdue University Libraries. Please contact [email protected] for additional information. RISC & DSP Advanced Microprocessor System Design Sample Projects, Fall 1991 John E. Fredine Dennis L. Goeckel David G. Meyer Stuart E. Sailer Glenn E. Schmottlach TR-EE 92- 11 March 1992 School of Electrical Engineering Purdue University West Lafayette, Indiana 47907 RlSC & DSP Advanced Microprocessor System Design Sample Projects, Fall 1991 John E. Fredine Dennis L. Goeckel David G. Meyer Stuart E. Sailer Glenn E. Schrnottlach School of Electrical Engineering Purdue University West Lafayette, Indiana 47907 Table of Contents Abstract ................................................................................................................... -

Introduction to Digital Signal Processors

INTRODUCTION TO Accumulator architecture DIGITAL SIGNAL PROCESSORS Memory-register architecture Prof. Brian L. Evans in collaboration with Niranjan Damera-Venkata and Magesh Valliappan Load-store architecture Embedded Signal Processing Laboratory The University of Texas at Austin Austin, TX 78712-1084 http://anchovy.ece.utexas.edu/ Outline n Signal processing applications n Conventional DSP architecture n Pipelining in DSP processors n RISC vs. DSP processor architectures n TI TMS320C6x VLIW DSP architecture n Signal and image processing applications n Signal processing on general-purpose processors n Conclusion 2 Signal Processing Applications n Low-cost embedded systems 4 Modems, cellular telephones, disk drives, printers n High-throughput applications 4 Halftoning, radar, high-resolution sonar, tomography n PC based multimedia 4 Compression/decompression of audio, graphics, video n Embedded processor requirements 4 Inexpensive with small area and volume 4 Deterministic interrupt service routine latency 4 Low power: ~50 mW (TMS320C5402/20: 0.32 mA/MIP) 3 Conventional DSP Architecture n High data throughput 4 Harvard architecture n Separate data memory/bus and program memory/bus n Three reads and one or two writes per instruction cycle 4 Short deterministic interrupt service routine latency 4 Multiply-accumulate (MAC) in a single instruction cycle 4 Special addressing modes supported in hardware n Modulo addressing for circular buffers (e.g. FIR filters) n Bit-reversed addressing (e.g. fast Fourier transforms) 4Instructions to keep the -

The Digital Signal Processor Derby

SEMICONDUCTORS The newest breeds trade off speed, energy consumption, and cost to vie for The an ever bigger piece of the action Digital Signal Processor BY JENNIFER EYRE Derby Berkeley Design Technology Inc. pplications that use digital signal-processing purpose processors typically lack these specialized features and chips are flourishing, buoyed by increasing per- are not as efficient at executing DSP algorithms. formance and falling prices. Concurrently, the For any processor, the faster its clock rate or the greater the market has expanded enormously, to an esti- amount of work performed in each clock cycle, the faster it can mated US $6 billion in 2000. Vendors abound. complete DSP tasks. Higher levels of parallelism, meaning the AMany newcomers have entered the market, while established ability to perform multiple operations at the same time, have companies compete for market share by creating ever more a direct effect on a processor’s speed, assuming that its clock novel, efficient, and higher-performing architectures. The rate does not decrease commensurately. The combination of range of digital signal-processing (DSP) architectures available more parallelism and faster clock speeds has increased the is unprecedented. speed of DSP processors since their commercial introduction In addition to expanding competition among DSP proces- in the early 1980s. A high-end DSP processor available in sor vendors, a new threat is coming from general-purpose 2000 from Texas Instruments Inc., Dallas, for example, is processors with DSP enhancements. So, DSP vendors have roughly 250 times as fast as the fastest processor the company begun to adapt their architectures to stave off the outsiders. -

The DENX U-Boot and Linux Guide (DULG) for Canyonlands

The DENX U-Boot and Linux Guide (DULG) for canyonlands Table of contents: • 1. Abstract • 2. Introduction ♦ 2.1. Copyright ♦ 2.2. Disclaimer ♦ 2.3. Availability ♦ 2.4. Credits ♦ 2.5. Translations ♦ 2.6. Feedback ♦ 2.7. Conventions • 3. Embedded Linux Development Kit ♦ 3.1. ELDK Availability ♦ 3.2. ELDK Getting Help ♦ 3.3. Supported Host Systems ♦ 3.4. Supported Target Architectures ♦ 3.5. Installation ◊ 3.5.1. Product Packaging ◊ 3.5.2. Downloading the ELDK ◊ 3.5.3. Initial Installation ◊ 3.5.4. Installation and Removal of Individual Packages ◊ 3.5.5. Removal of the Entire Installation ♦ 3.6. Working with ELDK ◊ 3.6.1. Switching Between Multiple Installations ♦ 3.7. Mounting Target Components via NFS ♦ 3.8. Rebuilding ELDK Components ◊ 3.8.1. ELDK Source Distribution ◊ 3.8.2. Rebuilding Target Packages ◊ 3.8.3. Rebuilding ELDT Packages ♦ 3.9. ELDK Packages ◊ 3.9.1. List of ELDT Packages ◊ 3.9.2. List of Target Packages ♦ 3.10. Rebuilding the ELDK from Scratch ◊ 3.10.1. ELDK Build Process Overview ◊ 3.10.2. Setting Up ELDK Build Environment ◊ 3.10.3. build.sh Usage ◊ 3.10.4. Format of the cpkgs.lst and tpkgs.lst Files ♦ 3.11. Notes for Solaris 2.x Host Environment • 4. System Setup ♦ 4.1. Serial Console Access ♦ 4.2. Configuring the "cu" command ♦ 4.3. Configuring the "kermit" command ♦ 4.4. Using the "minicom" program ♦ 4.5. Permission Denied Problems ♦ 4.6. Configuration of a TFTP Server ♦ 4.7. Configuration of a BOOTP / DHCP Server ♦ 4.8. Configuring a NFS Server • 5. -

On Performance of GPU and DSP Architectures for Computationally Intensive Applications

University of Rhode Island DigitalCommons@URI Open Access Master's Theses 2013 On Performance of GPU and DSP Architectures for Computationally Intensive Applications John Faella University of Rhode Island, [email protected] Follow this and additional works at: https://digitalcommons.uri.edu/theses Recommended Citation Faella, John, "On Performance of GPU and DSP Architectures for Computationally Intensive Applications" (2013). Open Access Master's Theses. Paper 2. https://digitalcommons.uri.edu/theses/2 This Thesis is brought to you for free and open access by DigitalCommons@URI. It has been accepted for inclusion in Open Access Master's Theses by an authorized administrator of DigitalCommons@URI. For more information, please contact [email protected]. ON PERFORMANCE OF GPU AND DSP ARCHITECTURES FOR COMPUTATIONALLY INTENSIVE APPLICATIONS BY JOHN FAELLA A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENE IN ELECTRICAL ENGINEERING UNIVERSITY OF RHODE ISLAND 2013 MASTER OF SCIENCE THESIS OF JOHN FAELLA APPROVED: Thesis Committee: Major Professor Dr. Jien-Chung Lo Dr. Resit Sendag Dr. Lutz Hamel Nasser H. Zawia DEAN OF THE GRADUATE SCHOOL UNIVERSITY OF RHODE ISLAND 2013 ABSTRACT This thesis focuses on the implementations of a support vector machine (SVM) algorithm on digital signal processor (DSP), graphics processor unit (GPU), and a common Intel i7 core architecture. The purpose of this work is to identify which of the three is most suitable for SVM implementation. The performance is measured by looking at the time required by each of the architectures per prediction. This work also provides an analysis of possible alternatives to existing implementations of computationally intensive algorithms, such as SVM. -

General Purpose Processors And

Benchmarking Microprocessors for High-End Signal Processing Stephen Paavola SKY Computers Phone: 978-250-1920 Email Address: [email protected] There are a number of general-purpose methodology was chosen because the microprocessor architectures which, while not benchmark is intended to measure bandwidth, designed for high-end signal processing, might not computational performance. provide the processing performance required for complex radars, signal intelligence and other As might be expected, the 800 MHz Broadcom demanding applications. But how well does each BCM1250, with the lowest operating frequency really perform as a digital signal processor? of the group, also has the lowest bandwidth, whether the access is to L1 or L2 cache. Despite To answer this question, some simple the fact that this dual-processor chip has benchmarks were run on a 1GHz Freescale integrated memory controllers, it still lags behind 7447 PowerPC, 1.8 GHz IBM 970 PowerPC, 1.8 the other processors when accessing DRAM. GHz AMD Opteron and 800 MHz Broadcom MIPS-based 1250 chip. Memory Read Bandwidth The bottom line of this set of benchmarks is that 20.0 the PowerPC with AltiVec produces impressive 18.0 computational performance compared to the 16.0 14.0 other processors considered. Now that IBM is s) / B 12.0 1.8 GHz Opteron shipping its PowerPC 970 with AltiVec, there is a G 1 GHz 7447 h ( t 10.0 d 1.8 GHz 970 processor alternative that addresses the i w 8.0 800 MHz Broadcom d memory bandwidth limitations of the 7447. n 6.0 Ba Yet, despite the strengths of AltiVec, the 4.0 benchmarks revealed that the alternative 2.0 0.0 1 2 4 8 6 2 4 8 6 2 2 processors offer some interesting capabilities for 1 3 6 2 24 48 96 9 1 25 51 0 0 0 1 2 4 81 particular types of signal processing. -

CORDIC Co-Processor Architecture for Digital Signal Processing Applications

A Fast CORDIC Co-Processor Architecture for Digital Signal Processing Applications Javier O. Giacomantone, Horacio Villagarcía Wanza, Oscar N. Bria CeTADΗ – Fac. de Ingeniería – UNLP [email protected] Abstract The coordinate rotational digital computer (CORDIC) is an arithmetic algorithm, which has been used for arithmetic units in the fast computing of elementary functions and for special purpose hardware in programmable logic devices. This paper describes a classification method that can be used for the possible applications of the algorithm and the architecture that is required for fast hardware computing of the algorithm. Keywords: Computer Architectures, CORDIC, Computer Arithmetic, Hardware Algorithms, Digital Signal Processing Applications. Η Centro de Técnicas Analógico-Digitales. Director: Ing. Antonio A. Quijano. A Fast CORDIC Co-Processor Architecture for Digital Signal Processing Applications Javier O. Giacomantone, Horacio Villagarcía Wanza, Oscar N. Bria CeTADΗ – Fac. de Ingeniería – UNLP [email protected] Abstract The coordinate rotational digital computer (CORDIC) is an arithmetic algorithm, which has been used for arithmetic units in the fast computing of elementary functions and for special purpose hardware in programmable logic devices. This paper describes a classification method that can be used for the possible applications of the algorithm and the architecture that is required for fast hardware computing of the algorithm. Keywords: Computer Architectures, CORDIC, Computer Arithmetic, Hardware Algorithms, Digital Signal Processing Applications. I. Introduction The Coordinate Rotation Digital Computer (CORDIC) is an arithmetic technique, which makes it possible to perform two dimensional rotations using simple hardware components. The algorithm can be used to evaluate elementary functions such as cosine, sine, arctangent, sinh, cosh, tanh, ln and exp. -

CMU DSP the Carnegie Mellon Synthesizable Digital Signal Processor Core

CMU DSP The Carnegie Mellon Synthesizable Digital Signal Processor Core Alpha Version Documentation 1.12 1999/06/10 Chris Inacio The CMU DSP Team [email protected] June 10, 1999 CONTENTS CONTENTS Contents 1 Introduction 3 1.1 Getting and Installing the Distribution . ................ 4 2 Architecture 5 2.1Overview................................ 5 2.2ArithmeticandDataLogicUnit.................... 6 2.3AddressGenerationUnit........................ 6 2.4OtherUnits............................... 7 2.4.1 Bus Switch ........................... 7 2.4.2 ProgramControlUnit..................... 7 2.5MemoryandExternalInterface..................... 7 3 File Repository 9 3.1 Availability ............................... 9 3.2VerilogSourceFiles........................... 9 3.3Documentation............................. 10 3.4TestScriptsandFiles.......................... 11 3.5MiscellaneousFiles........................... 11 4 Scripts and Tools 13 4.1 Introduction ............................... 13 4.2 Verilog PreProcessor ..................... 13 4.3 reformat ............................... 14 4.4 coff_text_dump .......................... 14 4.5 run-test ............................... 14 4.6 cp2build ............................... 16 4.7BuildingtheTools............................ 16 5 CMU DSP Testing 17 5.1 Introduction ............................... 17 5.2 Writing a new functional test . ................ 17 5.2.1 Overview............................ 17 5.2.2 Writing a new program . ................ 18 5.2.3 Motorola Simulation Traces . ............... -

(DSP) Application Development System (ADS) User's Manual

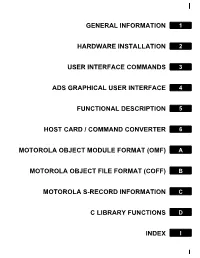

GENERAL INFORMATION 1 HARDWARE INSTALLATION 2 USER INTERFACE COMMANDS 3 ADS GRAPHICAL USER INTERFACE 4 FUNCTIONAL DESCRIPTION 5 HOST CARD / COMMAND CONVERTER 6 MOTOROLA OBJECT MODULE FORMAT (OMF) A MOTOROLA OBJECT FILE FORMAT (COFF) B MOTOROLA S-RECORD INFORMATION C C LIBRARY FUNCTIONS D INDEX I 1 GENERAL INFORMATION 2 HARDWARE INSTALLATION 3 USER INTERFACE COMMANDS 4 ADS GRAPHICAL USER INTERFACE 5 FUNCTIONAL DESCRIPTION 6 HOST CARD / COMMAND CONVERTER A MOTOROLA OBJECT MODULE FORMAT (OMF) B MOTOROLA OBJECT FILE FORMAT (COFF) C MOTOROLA S-RECORD INFORMATION D C LIBRARY FUNCTIONS I INDEX DIGITAL SIGNAL PROCESSOR (DSP) Application Development System (ADS) User’s Manual PRELIMINARY Motorola, Incorporated Semiconductor Products Sector Wireless Signal Processing Division 6501 William Cannon Drive West Austin, TX 78735-8598 This document (and other documents) can be viewed on the World Wide Web at http://www.motorola-dsp.com. OnCE is a trademark of Motorola, Inc. MOTOROLA INC., 1989, 1997 Order this document by DSPADSUM/AD Motorola reserves the right to make changes without further notice to any products herein to improve reliability, function, or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. Motorola products are not authorized for use as components in life support devices or systems intendedPRELIMINARY for surgical implant into the body or intended to support or sustain life. Buyer agrees to notify Motorola of any such intended end use whereupon Motorola shall determine availability and suitability of its product or products for the use intended. -

Fixed-Point C Compiler for Tms320c50 Digital Signal Processor

FIXED-POINT C COMPILER FOR TMS320C50 DIGITAL SIGNAL PROCESSOR Jiyang liang Wonyong Sung School of Electrical Engineering Seoul National University, KOREA jiyang@hdtv .snu.ac. kr and wysung@dsp, snu. ac. kr ABSTRACT 2. FIXED-POINT ARITHMETIC RULES A fixed-point C compiler is developed for convenient and ef- An integer variable or a constant in C language consists of, ficient programming of TMS320C50 fixed-point digital sig- usually, 16 bits, and the LSB(Least Significant Bit) has the nal processor. This compiler supports the ‘fix’ data type weight of one for the conversion to or from the floating-point that can have an individual integer word-length according data type. This can bring overflows or unacceptable quanti- to the range of a variable. It can add or subtract two data zation errors when a floating-point digital signal processing having different integer word-lengths by automatically in- program is converted to an integer version. Therefore, it is serting shift operations. The accuracy of fixed-point mul- necessary to assign a different weight to the LSB of a vari- tiply operation is significantly increased by storing the up- able or a constant [7] [8]. For this purpose, we employed per part of the multiplied double-precision result instead of a fixed-point data type that can have an individual integer keeping the lower part as conducted in the integer multipli- word-length as follows: cation. Several target specific code optimization techniques are employed to improve the compiler efficiency. The empir- fix(integer-wordlength) variable-name; ical results show that the execution speed of a fixed-point C program is much, about an order of magnitude, faster than that of a floating-point C program in a fixed-point digital Note that the range (R)that a variable can represent and signal processor.